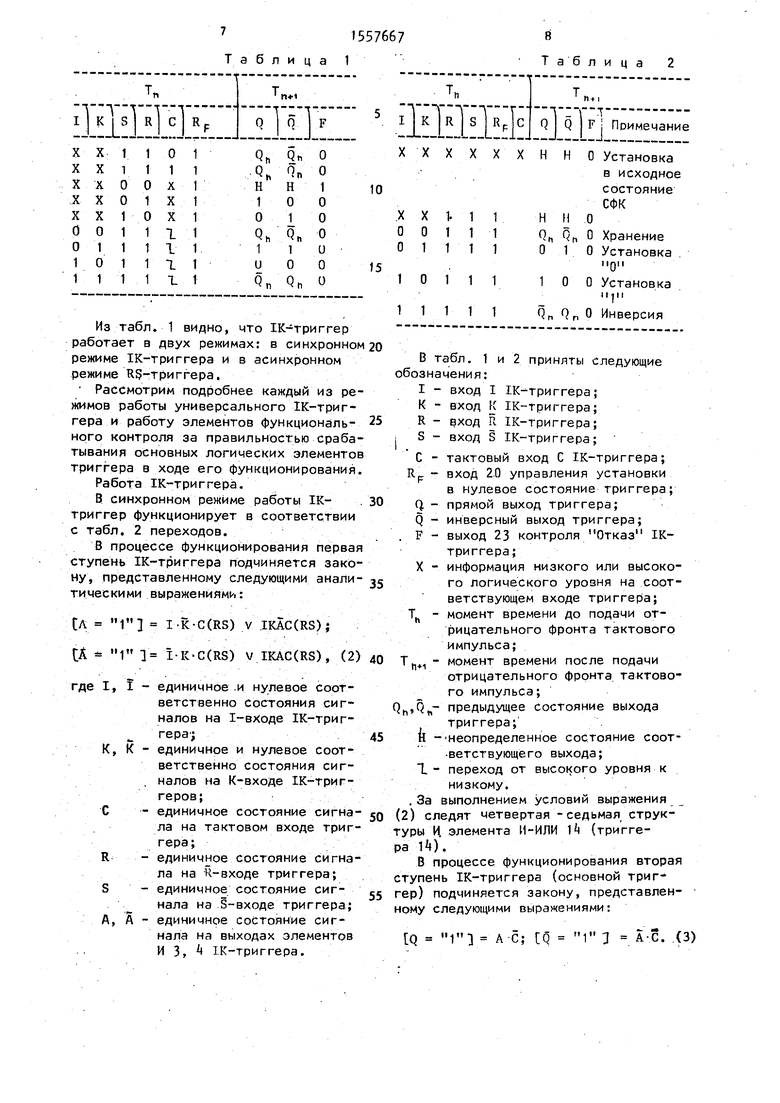

Из табл. 1 видно, что IK-триггер работает в двух режимах: в синхронном режиме IK-триггера и в асинхронном режиме КЗ-триггера. Рассмотрим подробнее каждый из режимов работы универсального IK-триггера и работу элементов функциональ- ного контроля за правильностью срабатывания основных логических элементов триггера в ходе его функционирования.

Работа 1К-триггера.

В синхронном режиме работы IK- триггер функционирует в соответствии с табл. 2 переходов.

В процессе функционирования первая ступень IK-триггера подчиняется закону, представленному следующими знали- тическими выражениями:

гл 1 I-K-C(RS) v IKAC(RS);

А 1 3 i-K-C(RS) V IKAC(RS), (2)

где I, I - единичное и нулевое соответственно состояния CHI- налов на 1-входе IK-три - гера;

К, К - единичное и нулевое соответственно состояния сигналов на К-входе 1К-триг- геров;

С - единичное состояние сигна- ла на тактовом входе триггера;

R - единичное состояние сигнала на Н-входе триггера;

S - единичное состояние CHI- нала на S-входе триггера;

А, А - единичное состояние сигнала на выходах элементов И 3, IK-триггера.

X X 1. 1 1 00111 01111

ХХХХХХННО Установка

в исходное состояние СФК

НПО Qtt Qn 0 Хранение

01 0 Установка

О

1О О Установка

Hill

Qn Qn 0 Инверсия

В табл. 1 и 2 приняты следующие обозначения:

I - вход I IK-триггера;

К - вход К IK-триггера;

R - вход R IK-триггера; I S - вход S IK-триггера;

С - тактовый вход С IK-триггера; RF - вход 20 управления установки

в нулевое состояние триггера; Q - прямой выход триггера; Q - инверсный выход триггера; F - выход 23 контроля Отказ IK- триггера;

X - информация низкого или высокого логического уровня на соответствующем входе триггера; момент времени до подачи отрицательного фронта тактового импульса;

момент времени после подачи отрицательного фронта тактового импульса; Qh,Qn- предыдущее состояние выхода

триггера;

И - Неопределенное состояние соответствующего выхода; 1 - переход от высокого уровня к

низкому.

. За выполнением условий выражения (2) следят четвертая -седьмая структуры К элемента И-ИЛИ И (триггера 1А).

В процессе функционирования вторая ступень IK-триггера (основной триггер) подчиняется закону, представленному следующими выражениями:

Q } А С; Q 1 7 А-С. (

Т. ti+i

За выполнением условий выражения (3) следят вторая и третьи структуры И элемента М-ИЛИ 1,

Функционал отказа любого из логических элементов первой ступени (вспомогательного триггера) , реализованный в предлагаемом техническом решении IK-триггера, можно представить следующим аналитическим выражением:}Q

F I К C/RS)A v C(RS)A v VIKAQ(RS)C V IKJq(RS)C. (4)

В случае нарушения условий ф ункци- онирования, представленных в выражении (2), на выходе триггера уже в мо- ,мент срабатывания логических элементов первой ступени вырабатывается сигнал 1К-триггера,20

Функционал отказа любого из логических элементов второй ступени (основного триггера), реализованный в техническом решении предлагаемого IK-триггера, можно представить выра- 25 жением:

F Q-Л-С v О-А-С.

В случае нарушения условий функци- онирования, представленных в выражении (3), на выходе триггера также вырабатывается сигнал Отказ IK- триггера ,

Рассмотрим последовательность срабатывания всех элементов логической структуры предлагаемого ТК-триггера в четырех основных режимах функционирования: хранения, установки О, установки 1 и инверсии.

В режиме Хранение (табл. 2, п.З) с приходом положительного фронта тактового импульса на С-вход не производится изменение состояния во вспомогательном триггере. Это осуществляется следующим образом. Примем, что предыдущее состояние IK-триггера было единичным. Тогда при нулевых логических уровнях сигнала на I- и К-входах и единичных уровнях сигнала на R-, S- и RF-входах будут закрыты вторые структуры И элементов И-ИЛИ-НЕ 1, 2, а открыты первые структуры элементов И-ИЛИ-НЕ 1, 2. Таким образом, срабатывание вспомогательного триггера не происходит. Контроль правильности хранения предыдущего состояния в IK-триггере происходит следующим образом. В результате выполнения

ой}Q

- -20

25

35

зо

,„

,„ .

45

55

67ifl

триггером режима хранения состояния основного и вспомогательного триггеров должны совпадать. В предлагаемом устройстве это осуществляется второй и третьей структурами И элемента И-ИЛИ 1 t (фиг. 1), на входы которых подаются сигналы с противоположных плеч основного и вспомогательного триггеров (точки Л и Q, А и Q соответственно) , а также сигнал разрешения проведения сравнения при тактовом сигнале С 0 с выхода элемента НЕ 9 и после допустимого времени срабатывания зсех элементов основного и вспомогательного триггеров, равного AT, с выхода элемента НЕ 11. При исправном функционировании всех основных логических элементов IK-триггера на выходе 23 будет присутствовать сигнал низкого логического уровня и в противном случае триггер I формирует на своем выходе высокий логический уровень сигнала.

При установке IK-триггерз в состояние О (см. табл. 2 п. А) с приходом положительного фронта синхроимпульса производится запись нулевого состояния во свпомогательный триггер и на время действия синхроимпульса в основном триггере хранится предыдущее состояние, так как с выхода элемента НЕ 9 на входы элементов И-НЕ 5 и 6 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие переходных процессов в элементах И-ИЛИ-НЕ 1 и 2, И 3 и А вспомогательного триггера на состояние основного триггера (элементы И-НЕ 7 и 8). Срабатывание элементов вспомогательного триггера происходит следующим образом. При предыдущем единичном состоянии IK-триггера вторая структура И элемента И-ИЛИ-НЕ 2 открыта и на его выходе через время Т будет установлен сигнал нулевого логического уровня. Первая и вторая структуры И элемента И-ИЛИ-НЕ 1 будут закрыты нулевыми потенциалами с выхода элемента И-НЕ 8 и с выхода элемента 2. Через время 2Т с момента поступления положительного фронта синхроимпульса на вход выходах элементов И-НЕ 5 и 6 установится высокий логический уровень сигнала. (Таким образом, через время 2Т с момента поступления положительного фронта синхроимпульса на входах элементов И 3 и А присутствуют следующие

11,5

сигналы: элемент И 3 будет закрыт нулевым логическим уровнем сигнала с выхода элемента И-ИЛИ-ПЕ 2, элемент И Ц пропустит на свой выхоп; высокий логический уровень сигнала, так как на его входах будут присутствовать все высокие логические уровни cm- налов (с выхода элемента И-Ht 5, с выхода элемента И-ИЛИ-НЕ 1 и с S-вхо- да IK-триггера). Следовательно, через время ЗТ на выходе элемента И 3 (см. Л, фиг. 1) будет установлен сигнал нулевого логического уровня, а на выходе элемента И ) (А, фиг, 1) - высокий логический уровень сигнала. Контроль правильности срабатывания основных элементов вспомогательного триггера будет осуществлен следующим образом. Через время, несколько больше чем ЗТ, ча выходе элемента И 10 появится высокий логический уровень сигнала, КОТОРЫЙ является стробом сравнения для четвертой и пятой структур И элемента И-ИЛИ , осуществляющих контроль правильности срабатывания логических элементов вспомогательного триггера. Еспи в -оезультате срабатывания основных логических элементов вспомогательного триггера будет выполнено условие

(RS)-C-(I Ю-А Г1,(6)

где R - единичный логический уровень сигнала на R-входе триггера;

S - единичный логический уровень сигнала на S-входе триггера;

С - единичный уровень сигнала на С-входе триггера;

К - единичный сигнал на К-входе триггера;

А - единичный сигнал на выходе

элемента И Ц,

то первая ступень (элементы вспомогательного триггера) сработала правильно и на входе элемента И-ИЛИ И присутствует сигнал О. При неправильном срабатывании (отказе какого- либо из основных элементов вспомогательного триггера) равенство (6) нарушается и элемент И-ИЛИ 1 пропускает высокий логический уровень сигнала на свой выход и устанавливается устой чивое единичное состояние, сигнализируя о возникновении отказа. На выходе 23 (F) устройства формируется сигнал Отказ, означающий, что первая ступень IK-триггера сработала неправильно.

766712

Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в этом режиме производится следующим образом. По окончании действия сигнала на тактовом входе 17 и при правильном срабатывании элементов вспомогательного триггера на одном из

JQ элементов И-НЕ 5 и 6 сформируется сигнал О, который установит сигнал на выходе элемента И 10 в одноименное состояние, что приведет к формированию высокого логического уровня сиг15 нала на выходе элемента НЕ 11, т.е. к формированию строба сравнения через время 4Т с момента поступления отри- цатепьного фронта тактового сигнала Одновременно с этим появление CHI-

20 нала О на выходе одного из элементов И-НЕ 5 и 6 а для рассматриваемого примера сигнал О присутствует на выхоце элемента И-НЕ 6. приведет к формированию единичного сос25 тояния на выходе элемента И-НЕ 8,

что соответствует необходимому значению логического сигнала на выходе 22 (Q), т.е. режиму Установка нуля. Через время Т закончатся переходный

Зо пооцесс установки в нулевое состояние сигнала на выходе элемента И-НЕ 7. Таким образом, через время 4 Т с момента поступления на вход 17 IK-триггера отрицательного фронта синхросигнала в основном триггере (элементы И-НЕ 7 и 8) заканчиваются переходные процессы и на второй и третьей структурах И элемента И-ИЛИ И производится контроль состояний противоположных плеч вспомогательного и основного

триггеров (сигнал в точке сигналом на выходе 22 и в точке А с сигналом на выходе 21). При правильном срабатывании основного триггера на

45 выходе элемента И-ИЛИ И присутствует сигнал О, в противном случае вырабатывается сигнал 1, означающий отказ одного из элементов И-НЕ 7 и 8 основного триггера.

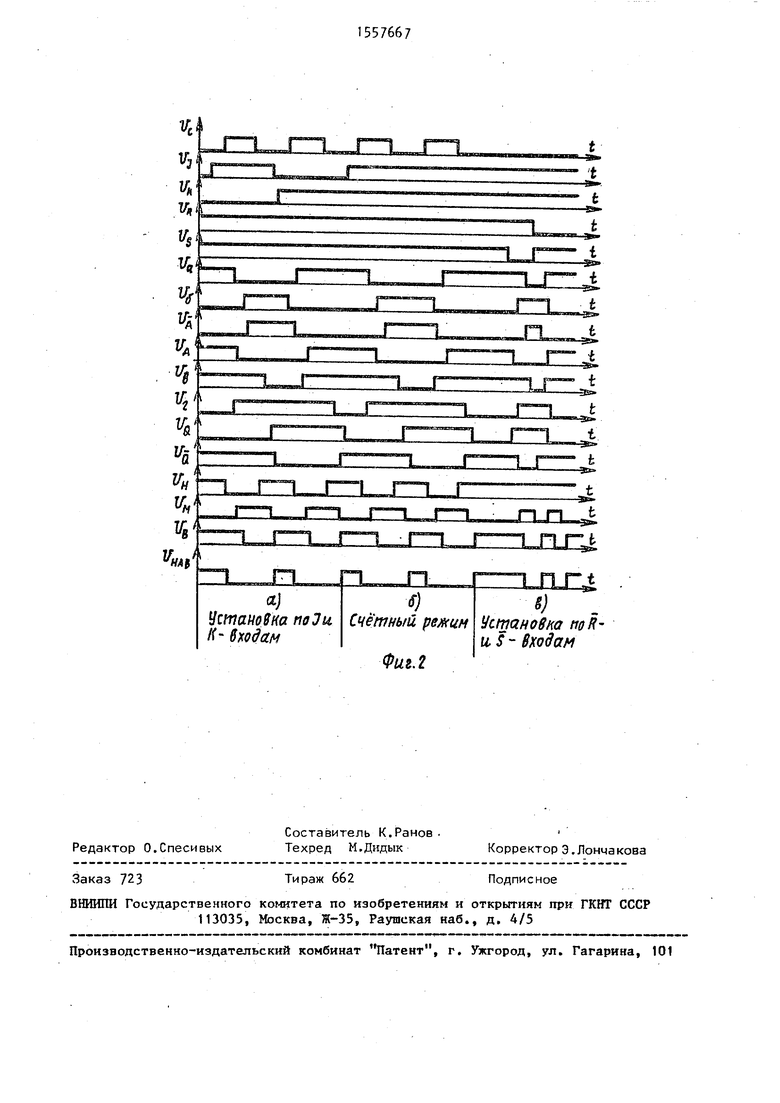

50 В режиме установки IK-триггера в 1 (табл. 2, п. 5) с приходом положительного фронта синхроимпульса на вход 17 (см. фиг. 2а) производится запись единичного состояния во вспомогательный триггер и на время действия синхроимпульса основной триггер переводится в режим хранения предыдущего состояния, так как с выхода1 элемента НЕ 9 на входы элементов

40

55

Ч155

И-НЕ 5 и 6 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие переходных процессов в логических элементах вспомогательного триггера на состояние основного триггера. Срабатывание логических элементов вспомогательного триггера производится следующим образом. При предыдущем нулевом состоянии IK- триггера на выходе элемента И-ИЛИ-НЕ 1 через время 2Т будет сформирован нулевой логический уровень сигнала, а на выходе элемента И-ИЛИ-НЕ 2 - высокий логический уровень сигнала. В результате этого элемент И 4 будет закрыт нулевым уровнем сигнала с выхода элемента И-ИЛИ-НЕ 1, а элемент

СР

И 3 - открыт, т.е. через врем,) ЗТ при правильном срабатывании элементов вспомогательного триггера в точке А устанавливается высокий логический уровень сигнала, а в точке Л - нулевой логический уровень сигнала.

Контроль правильности срабатывания логических элементов вспомогатель ного триггера в этом режиме осуществляется следующим обрезом. Через такое же время ЗТ на выходе элемента И 10 формируется высокий логический уровень сигнала, который для четвертой и пятой структур И элемента И-ИЛИ 14 является стробом соавнения. Если в результате срабатывания основных элементов вспомогательного триггера будет выполнено условие

(RS)-G-(I К)-А 1

где R - единичный сигнал на R-входе

триггера; S - единичный сигнал на S-входе

триггера; С - единичный сигнал на С-входе

триггера; К - нулевой сигнал на К-входе

триггера; А - единичный сигнал на выходе

элемента И 3 (ил, фиг. 2), то элементы вспомогательного триггера сработали правильно и на выходе элемента И-ИЛИ 14 будет присутствовать сигнал О. При неправильном срабатывании (отказе) какого-либо из основных логических элементов вспомогательного триггера равенство (7) нарушается и пятая структура И- элемента И-ИЛИ 1 пропускает на его выход высокий технологический уровень сигнала

5

7667|б

-4 Т О ПРИВОДИТ К ФОРМИРОВАНИЮ YfnulMвого сигнала Отказ на выходе устройства.

Функционирование и контроль правильности срабатывания основных логических элементов соновного триггерт s этом режиме производится следующим образом. По окончании действия CHI- JQ нала на входе 17 (фиг. 2, UcUi при

5

,

правильном срабатывании вспомогательного триггера элементом И-НЕ 5 формируется сигнал О, который установит выходы элементов И 10 и И-НЕ 7 в CQOIjr ветствующие логические состояния. На выходе элемента И 10 будет сформирован сигнал О, который приведет к формированию на выходе элемента НЕ 11 сигнала высокого логического уровня.

20 Этот сигнал будет сформирован с задержкой на 4Т по отношению к моменту появления отрицательного фронта тактового импульса. На выходе элемента И-НЕ 7 также через время ЗТ сформи25 руется сигнал 1, который через время 4Т приводит к формированию сигнала О на выходе элемента S1-HE 8. Таким образом, через время 4 Т на выходах 21 и 22 устройства будут сформиIQ рованы соответственно высокий и низкий логические уровни сигналов, что будет соответствовать заданному режиму функционирования IK-триггера, т. е. режиму Установка 1. Таким образом, через время 4 Т с момента поступления на вход 17 1К-триггера отрицательного фронта тактового CHI- нала в основном триггере заканчиваются переходные процессы и на второй и третьей структурах И элемента И-ИЛИ 14 по стробу сравнения с выхода элемента НЕ 11 производится контроль правильности срабатывания его логических элементов И-НЕ 7 и 8. При правильном срабатывании на выходе элемента И-ИЛИ 14 вырабатывается сигнал О, в противном случае - 1м. В режиме инверсии состояния IK- триггера (табл. 2, п. 6), или- режиме счета с приходом положительного фронта синхроимпульса на вход 17 IK-триггера производится изменение предыдущего состояния триггера на противоположное. При исправном функционировании основных логических элементов IK- триггера должны быть выполнены следующие равенства:

(RS)4l К С)-A Q 1, (8) (RS),(I К С)-A Q М. (9)40

50

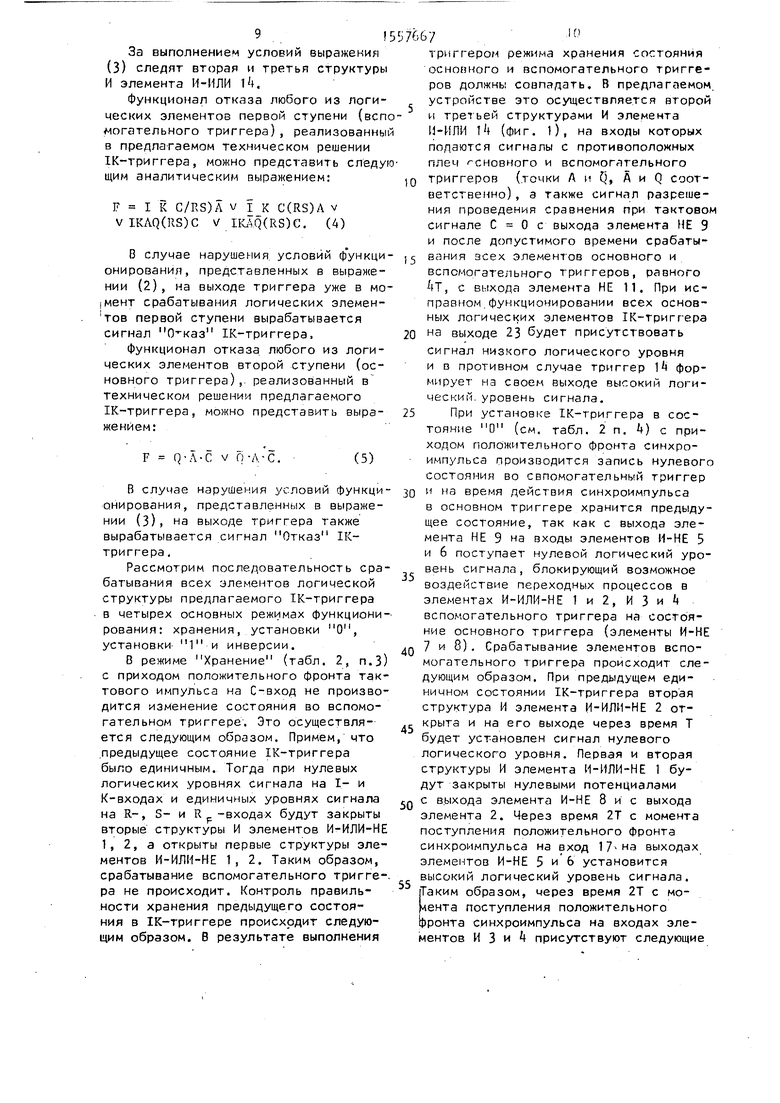

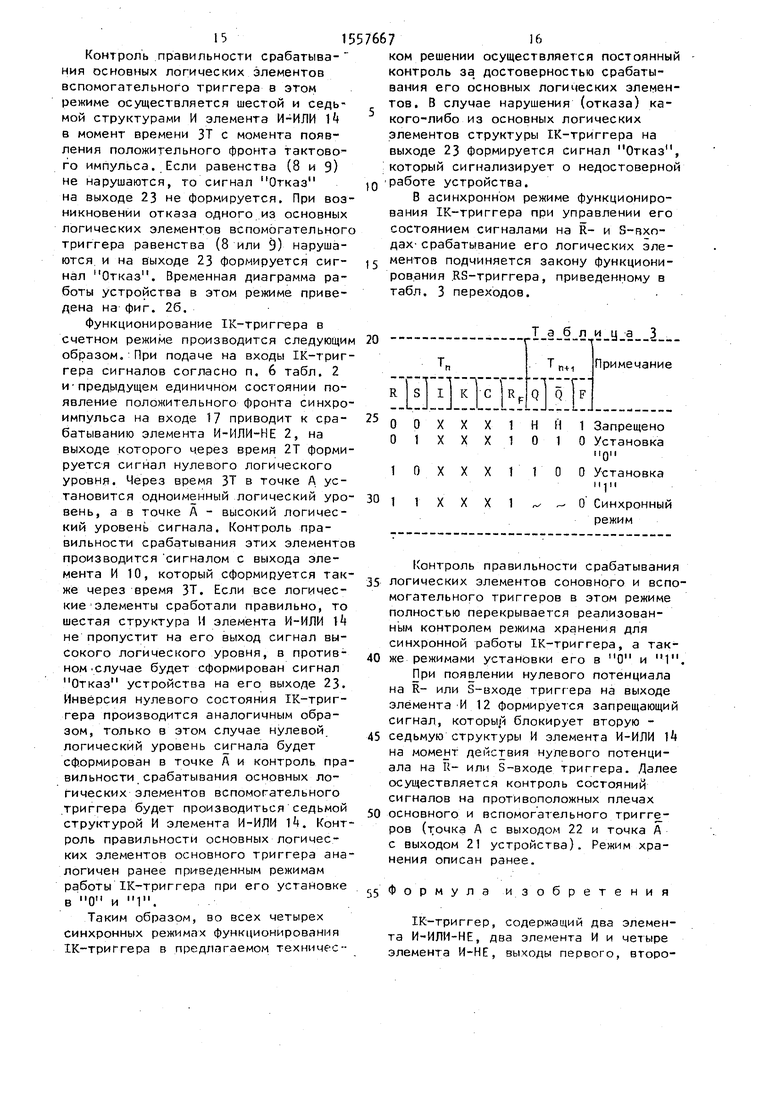

Контроль правильности срабатыва- ния основных логических элементов вспомогательного триггера в этом режиме осуществляется шестой и седьмой структурами И элемента И-ИЛИ И в момент времени ЗТ с момента появления положительного фронта тактового импульса. Если равенства (8 и 9) не нарушаются, то сигнал Отказ на выходе 23 не формируется. При возникновении отказа одного из основных логических элементов вспомогательного триггера равенства (8 или 9) нарушаются и на выходе 23 формируется сигнал Отказ. Временная диаграмма работы устройства в этом режиме приведена на фиг. 26.

Функционирование IK-триггера в счетном режиме производится следующим образом. При подаче на входы IK-триггера сигналов согласно п. 6 табл. 2 и предыдущем единичном состоянии появление положительного фронта синхроимпульса на входе 17 приводит к срабатыванию элемента И-ИЛИ-НЕ 2, на выходе которого через время 2Т формируется сигнал нулевого логического уровня. Через время ЗТ в точке А установится одноименный логический уровень, а в точке А - высокий логический уровень сигнала. Контроль правильности срабатывания этих элементов производится сигналом с выхода элемента И 10, который сформируется также через время ЗТ. Если все логические элементы сработали правильно, то шестая структура И элемента И-ИЛИ k не пропустит на его выход сигнал высокого логического уровня, в противном случае будет сформирован сигнал Отказ устройства на его выходе 23. Инверсия нулевого состояния IK-триггера производится аналогичным образом, только в этом случае нулевой логический уровень сигнала будет сформирован в точке А и контроль правильности срабатывания основных логических элементов вспомогательного триггера будет производиться седьмой структурой И элемента И-ИЛИ И. Контроль правильности основных логических элементов основного триггера аналогичен ранее при-веденным режимам работы IK-триггера при его установке в О и 1.

Таким образом, во всех четырех синхронных режимах функционирования IK-триггера в предлагаемом техническом решении осуществляется постоянный контроль за достоверностью срабатывания его основных логических элементов. В случае нарушения (отказа) какого-либо из основных логических элементов структуры IK-триггера на выходе 23 формируется сигнал Отказ, который сигнализирует о недостоверной

работе устройства.

В асинхронном режиме функционирования IK-триггера при управлении его состоянием сигналами на R- и S-RXO- дах- срабатывание его логических эле5 ментов подчиняется закону функционирования RS-триггера, приведенному в табл. 3 переходов.

О О X X X 1 Н Н 1 Запрещено

01 X X X 1 0 1 0 Установка

О

1О X X X 1 100 Установка

и 1 м

1 1 X X X 1 0 Синхронный

режим

Контроль правильности срабатывания

логических элементов соновного и вспомогательного триггеров в этом режиме полностью перекрывается реализованным контролем режима хранения для синхронной работы IK-триггера, а также режимами установки его в О и 1.

При появлении нулевого потенциала на R- или S-входе триггера на выходе элемента И 12 формируется запрещающий сигнал, которы.й блокирует вторую седьмую структуры И элемента И-ИЛИ 1 на момент действия нулевого потенциала на II- или S-входе триггера. Далее осуществляется контроль состояний сигналов на противоположных плечах

основного и вспомогательного триггеров (точка А с выходом 22 и точка А с выходом 21 устройства). Режим хранения описан ранее.

Формула изобретения

IK-триггер, содержащий два элемента И-ИЛИ-НЕ, два элемента И и четыре элемента И-НЕ, выходы первого, второго элементов И-ИЛИ-НЕ соединены соответственно с первыми входами первых структур И второго и первого элементов И-ИЛИ-НЕ и соединены соответственно с первыми входами первого, второго элементов И, выходы которых соединены соответственно с первыми входами первого, второго элементов И-НЕ, выходы которых соединены соответст- венно с вторыми входами второго и первого элементов И и соединены соответственно с первыми входами третьего и четвертого элементов И-НЕ, выходы которых соединены соответственно с прямым и инверсным выходами, соединены соответственно с вторыми входами четвертого и третьего элементов И-НЕ и соединены соответственно с первыми входами вторых структур И второго и первого элементов И-ИЛИ-НЕ, вторые входы вторых структур И которых соединены соответственно с входами S и R, соединены соответственно с вторыми входами первых струк- тур И второго и первого элементов И-ИЛИ-НЕ, соединены соответственно с третьими входами второго и первого элементов И и соединены соответственно с третьими входами третьего и чет- вертого элементов И-НЕ, входы I и К соединены соответственно с третьими входами вторых структур И первого и второго элементов И-ИЛИ-НЕ, четвертые входы вторых структур И которых соединены с тактовым входом (отличающийся тем, что, с целью повышения достоверности функционирования, в него введены два элемента НЕ, третий, четвертый элементы И, элемент И/И-НЕ, элемент И-ИЛИ, выход контроля и вход управления, который соединен с первым входом первой структуры И элемента И-ИЛИ, второй вход первой структуры И кото- рого соединен с выходом элемента И-ИЛИ и с выходом контроля, тактовый вход С соединен с входом первого элемента НЕ, выход которого соединен с вторыми

g 5 0 5 о Q с

5

входами первого и второго элементов И-НЕ, выходы которых соединены соответственно с первым, вторым входами третьего элемента И, выход которого соединен с входом второго элемента НЕ, входы R и П соединены соответственно с первым, вторым входами четвертого элемента И, выход которого соединен с первыми входами второй, третьей, четвертой, пятой, шестой и седьмой структур И элемента И-ИЛИ. второй, третий четвертый и пятый входы второй структуры И которого соединены соответственно с выходами третьего элемента И-НЕ, второго элемента НЕ, первого элемента НЕ и второго элемента И, второй, третий, четвертый и пятый входы третьей структуры И элемента И-ИЛИ соединены соответственно с выходами второго, первого элементов НЕ, первого элемента И и четвертого элемента И-НЕ, второй, третий, четвертый и пятый входы четвертой структуры И элемента И-ИЛИ соединены соответственно с выходом второго элемента И, с входом I, с выходом третьего элемента И и с инверсным выходом элемента И/И-НЕ, первый, второй входы которого соединены соответственно с входами I и К, второй, третий, четвертый и пятый входы пятой структуры И элемента И-ИЛИ Соединены соответственно с входом К, с выходами первого элемента И, третьего элемента И и с инверсным выходом элемента И/И-НЕ, второй, третий, четвертый и пятый входы шестой структуры И элемента И-ИЛИ соединены соответственно с выходами третьего элемента И-НЕ, первого элемента И, третьего элемента И и с прямым выходом элемента И/И-НЕ, второй, третий, четвертый и, пятый входы седьмой структуры И элемента И-ИЛИ соединены соответственно с BbixoflaMvt четвертого элемента И-НЕ, второго, третьего элементов И и с прямым выходом элемента И/И-НЕ.

Vc

I-} r°i r°i

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| DV-триггер | 1988 |

|

SU1564714A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Резервированный RS-триггер | 1989 |

|

SU1629962A1 |

| ДV-триггер | 1989 |

|

SU1629963A1 |

| DV-триггер | 1987 |

|

SU1465936A1 |

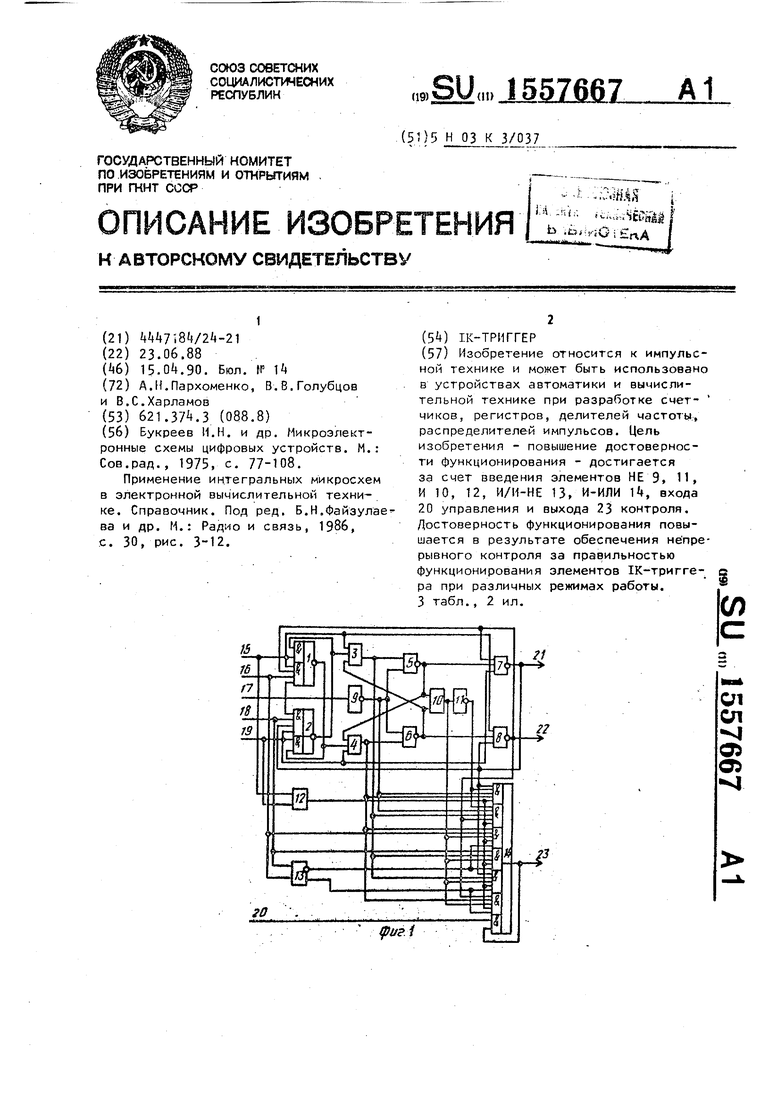

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной технике при разработке счетчиков, регистров, делителей частоты, распределителей импульсов. Цель изобретения - повышение достоверности функционирования - достигается за счет введения элементов НЕ 9, 11, И 10, 12, И/И-НЕ 13, И-ИЛИ 14, входа 20 управления и выхода 23 контроля. Достоверность функционирования повышается в результате обеспечения непрерывного контроля за правильностью функционирования элементов JK-триггера при различных режимах работы. 3 табл., 2 ил.

W

&H IU

1™C

К

/ид

ГТ

aj

Установка па У и К- входам

ГТ

Г

t

ь

Ш

П.

rt

I) Установка по till $- Входам

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М.: Сов.рад., 1975, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник | |||

| Под рец | |||

| Б.Н.Файзулае- ва и др | |||

| М.: Радио и связь, 1986, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( IK-ТРИГГЕР | |||

Авторы

Даты

1990-04-15—Публикация

1988-06-23—Подача