В процессе своего функционирования первая ступень DV-триггера подчиняется закону, представленному Следующим аналитическим выражением:

f() D-V-C-(R-S) -V-S; (2) Ј() D-V-C -(R-S)- V-R, (3)

где V - единичное состояние сигнала

на V-входе DV-триггера; 1 С - единичное состояние сигнала

на синхровходе DV-триггера; D, D - единичное и нулевое соответственно состояния сигналов на D-входе DV-триггера; А, А - состояния сигналов в точках А и А на чертеже DV-триггеРа;

R, R - единичное и нулевое соответственно состояния сигналов на R-входе DV-триггера; S, S - единичное и нулевое соответственно состояния сигналов на S-входе DV-триггера. За выполнением условий выражений (2 и 3) следят третья и четвертая структуры И элемента И-ИЛИ 1ч.

В процессе своего функционирования вторая ступень (вспомогательный триггер) DV-триггера подчиняется закону, который можно представить следующим аналитическим выражением:

OFC)-A-Q-(R.S) IJ VKV D-A-Q (R-S) I,(4)

0

0

5

5

0

5

где - единичное состояние CHI- нала на выходе элемента И/И-НЕ 10 DV-триггера; Q, Q - состояния сигналов на

прямом и инверсном соответственно выходах DV- триггера.

За выполнением условий выражения (ч) следят первая и вторая структуры И элемента И-ИЛИ 1ч.

Функционал отказа любого из логических элементов первой ступени (основного триггера), реализованный в предлагаемом DV-триггере, можно представить следующим аналитическим выражением:

R (V-C) D-A-(R-S) V(T.C)-D-A(R-S)..

(5)

В случае нарушения условий функционирования, представленных в выражениях Д2 и 3), на выходе элемента И-ИЛИ 1ч уже в момент срабатывания логических элементов первой ступени вырабатывается сигнал Отказ DV- триггера.

Функционал отказа любого из логических элементов второй ступени (вспомогательного триггера), реализованный в техническом решении предлагаемого DV-триггера, можно представить следующим выражением:

F ()-A-Q -(R-S) V(Tc)-A-Q.(R-S)

(6)

915647

8 случае нарушения условий функционирования, представленных в вырз- жении (4), на выходе элемента И-ИЛИ 14 также вырабатывается сигнал Отказ DV-триггера.

Асинхронный режим функционирования предлагаемого DV-триггера контролируется шестой и седьмой структурами И элемента И-ИЛИ 1ч. Режим установки

10

в 1 контролирует шестая структура И, режим установки в О контролирует седьмая структура И элемента И- ИЛИ 14. Характерной особенностью этого режима является то, что установка основного и вспомогательного триггеров структуры DV-триггера осуществляется одновременно. Вот почему строб сравнения на выходах элементов НЕ 12 и 13 вырабатывается через время не менее 2ТСр, т.е. . мерез время срабатывания элементов И-НЕ 3 и 4, а также элементов И-НЕ 7 и 8. В случае правильного срабатывания всех элементов ни шестая, ни седьмая структуры И не пропустят на свой выход высокий логический уровень сигнала и на выходе элемента И-ИЛИ 14 сигнал Отказ не будет сформирован. В противном случае такой сигнал будет сформирован и он будет означать, что при асинхронной установке триггера в О или 1 произошел отказ какого-либо логического элемента структуры DV-триггера.

Рассмотрим последовательность срабатывания всех элементов логической структуры предлагаемого DV-триггера в его трех основных режимах синхронного функционирования: Хранение, Установка 1 и Установка О.

В режиме Установка 1 (таблица п. 4) по D-входу с поступлением положительного фронта синхросигнала на С-вход триггера на выходе первого элемента И-НЕ 1 через время 2Тср срабатывания элементов И 15 и И-НЕ 1 установится сигнал логического О. Следовательно, через время ЗТСрсрабатывания, с момента поступления1 положительного фронта сигнала на С- вход, на выходах второго и третьего элементов И-НЕ 2 и 3 установятся CHI- налы логической 1, а через время 4Тср срабатывания на выходе четвер того элемента И-НЕ 4 - сигнал логичекого О. Таким образом, через время 4 Тср в точке А (см. чертеж) будет установлено состояние логической

0

5

0

5

0

0

5

5

0

10

1, а в точке А - состояние логического О. Контроль правильности срабатывания логических элементов первой ступени DV-триггера осуществляется стробом сравнения с инверсного выхода элемента И/И-riE 10, который появляется также через время не менее 4 Тсо срабатывания элементов И 15, НЕ 9 и самого элемента И/И-НЕ 10. Если в ходе контроля будут выполнены условия (2 и 3), то третья и четвертая структуры И элемента И-ИЛИ 14 не пропустят на его выход сигнал логической 1. При нарушении алгоритма функционирования логическими элементами первой ступени, т.е. выполнится условие (4), на выходе триггера на элементе И-ИЛИ 14 вырабатывается сигнал логической 1, сигнализируя об отказе первой ступени DV-триггерз.

С приходом на С-вход DV-триггера отрицательного фронта синхроимпульса состояние первой ступени передается во вторую ступень, т.е. пятый элемент И-НЕ 5 установится в состояние логического О на своем выходе, а шестой элемент И-НЕ 6 останется в состоянии логической 1 на своем выходе. Следовательно, через время 4 Тср срабатывания с момента поступления отрицательного фронта синхроимпульса на выходе элемента И-НЕ 7 установится сигнал логической 1, а через время 5ТСр на выходе элемента И-НЕ 8 - сигнал логического О. Контроль правипьности срабатывания логических элементов второй ступени производится стробом сравнения, который появляется на выходе элемента И/И-НЕ 10 через время не менее 5 ТСр срабатывания с момента появления отрицательного фронта на синхровходе DV-триггера. При выполнении условия (4) на выходе тригге- ра на элементе И-ИЛИ 14 сигнал Отказ не сЛормируется. В противном случае, т.е. при выполнении условия (6), на его выходе будет сформирован сигнал Отказ одного или нескольких логических элементов второй ступени DV-триг гера.

, 13 режиме Установка О (таблица, п. 5) по D-входу с приходом положительного фронта синхросигнала на выходе элемента И-НЕ устанавливается сигнал .логической 1, а на выходе элемента И-НЕ 2 - сигнал логического О, который через время 3 Тср ера11 15&4 батывания с момента появления положительного фронта синхроимпульса приведет к Формированию на выходе элемента 4 сигнала логической 1м. Через время 4 Tcp на выходе элемента И-ИЕ 3 будет сформирован сигнал логического 0м. Контроль правильности срабатывания логических элементов первой ступени в этом случае будет проведен на входах третьей и четвер той структур И элемента И-ИЛИ 14 сигналом сравнения с выхода элемента И/И-НЕ 10, который будет сформирован через время не менее 4 TCp срабаты- вания элементов И 15 НЕ 9 и самого элемента И/И-НЕ 10. При выполнении условий (2 и 3) сигнал Отказ на выходе триггера на элементе И-ИЛИ 14 не появится; в противном случае он будет сформирован, сигнализируя об отказе одного или нескольких логических элементов первой ступени DV-триг- гера.

Функционирование и контроль пра- вильности срабатывания логических элементов второй ступени производится следующим образом.

При появлении на синхровходе DV- триггера отрицательного фронта синх- росигнала состояние основного триггера (первой ступени) будет передано во вторую ступень по следующей логической ветви: через 3 TCf на выходе элемента И-НЕ 6 будет сформирован сигнал логического через время 4 Т-с„ на выходе элемента И-НЕ 8 - сигнал ло--ииеской 1 и через время

5 Т

ор

на выходе элемента И-НЕ 7

сигнал логического О. Контроль правильности срабатывания будет произведен сигналом сравнения с прямого выхода элемента И/И-НВ 10, который будет сформирован также через время 5 Тср срабатывания элементов И 15, НС 9 и самого элемента И/И-НЕ 11). При выполнении условия (4) сигнал Отказ на выходе триггера на элементе И-ИЛИ 14 сформирован не будет. В противном случае, т.е. при выпол- нении условия (6) на его выходе формируется сигнал Отказ, сигнализируя об отказе одного или нескольких логических элементов второй ступени DV-триггера,

В режиме хранения (таблица 1, п,7 т.е. при наличии нулевого i этенциала на синхровходе DV-триггера, с выходов элементов И-НЕ 1 и 2 на входы

12

элементов И-НЕ 3 и 4 поступают сигналы логической 1м, подтверждая предыдущее состояние триггера первой ступени. С выходов элементов И-НЕ 5 и 6 на входы элементов И-НЕ 7 и 8 также поступают сигналы логической 1, подтверждая предыдущее состояние триггера второй ступени.

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом.

Через время 2 Тср срабатывания элементов И 15 и НЕ 9 производится сравнение состояний в точке А с состоянием на прямом выходе DV-триггера и в точке А с состоянием сигнала на инверсном выходе DV-триггера. Такое же сравнение производится через врем 5 Tcf с момента появления сигнала логического О на синхровходе DV- триггера стробом сравнения с выхода (инверсного) элемента И/И-НЕ 10.

Функционирование и контроль правильности срабатывания логических элементов структуры DV-триггера в остальных режимах его функционирова ния (таблица 1, пга. 2, 3 и 6) производится аналогичным образом.

Формула изобретения

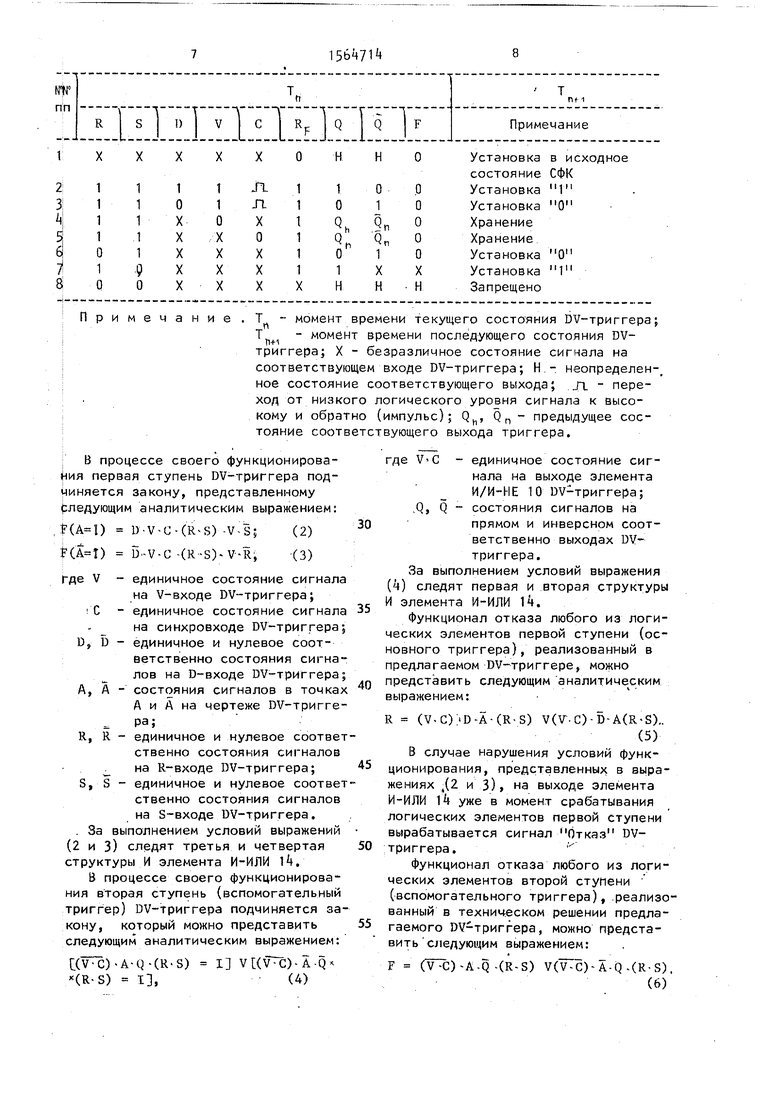

DV-триггер, содержащий D-, V-, С-входы, шину установки, выходную шину Отказ, восемь элементов И-НЕ, четыре элемента НЕ, элемент И и элемент И-ИЛИ, D-вход соединен с первым входом первого элемента И-НЕ, выход которого соединен с первыми входами второго и третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, выходы третьего и четвертого элементов И-НЕ соединены соответственно с вторыми входами четвертого и третьего элементов И-НЕ и соединены соответственно с первыми входами пятого и шестого элементов И-НЕ, выходы которых соединены соответственно с первыми входами седьмого и восьмого элементов И-НЕ, выходы которых соединены соответственно с прямым и инверсным выходами, соединены соответственно с вторыми входами восьмого и седьмого элементов И-МЕ- и соединены соответственно с первыми входами первой, второй структур И элемента И-ИЛИ„ вторые входы первой, второй структур И которого соединены соответственно с выходами четвертого и третьего элементов И-НЕ и соединены соответственно с первыми входами третьей и четвертой структур И элемента И-ИЛИ, выход которого соединен с выходной шиной Отказ и с первым входом пятой структуры И элемента И-ИЛИ, второй вход пятой структуры И которого соединен с шиной ус- тановки, второй вход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ и соединен с входом первого элемента НЕ, выход которого соединен с вторыми входами пято- го, шестого элементов И-НЕ и с третьими входами первой, второй структур И элемента И-ИЛИ, вторые входы третьей и четвертой структур И которого соединены соответственно с входом и выходом второго элемента НЕ, вход которого соединен с D-входом, V-вход соединен с первым входом элемента И, четвертый вход первой и третий вход третьей структур И элемента И-ИЛИ соединены соответственно с четвертым входом второй и с третьим входом четвертой структур И элемента И-ИЛИ, отличающийся тем, что, с целью расширения функциональ- ных возможностей, в него введены R-, S-входы, элемент И/И-НЕ с временем срабатывания не менее 3 Тср, где Тср - среднее время срабатывания логического элемента, в качестве тре-

0 5 0 5

0

5

тьего, четвертого элементов НЕ используются элементы НЕ с временем срабатывания не менее 2 Тср , а в элемент И-ИЛИ введены шестая и седьмая структуры И, первые входы которых соединены соответственно с выходами третьего и четвертого элементов НЕ, входы которых соединены соответственно с S- и R-входами, соединены соответственно с третьими входами третьего и четвертого элементов И-НЕ, соединены соответственно с третьими входами седьмого и восьмого элементов И-НЕ и соединены соответственно с вторым и третьим входами элемента И, четвертый вход и выход которого соединены соответственно с С-входом и с входом первого элемента НЕ„ выход которого соединен с входами элемента И/И-НЕ, прямой и инверсный выходы которого соединены соответственно с четвертым входом первой и с третьим входом третьей структур И элемента И-ИЛИ, вторые входы шестой и седьмой структур И которого соединены соответственно с выходами четвертого и третьего элементов И-НЕ, S-вход соединен с пятыми входами первой, второй и с четвертыми входами третьей и четвертой структур 1 элемента И-ИЛИ, шестые входы первой, второй и пятые входы третьей, четвертой структур И которого соединены с R- входом.

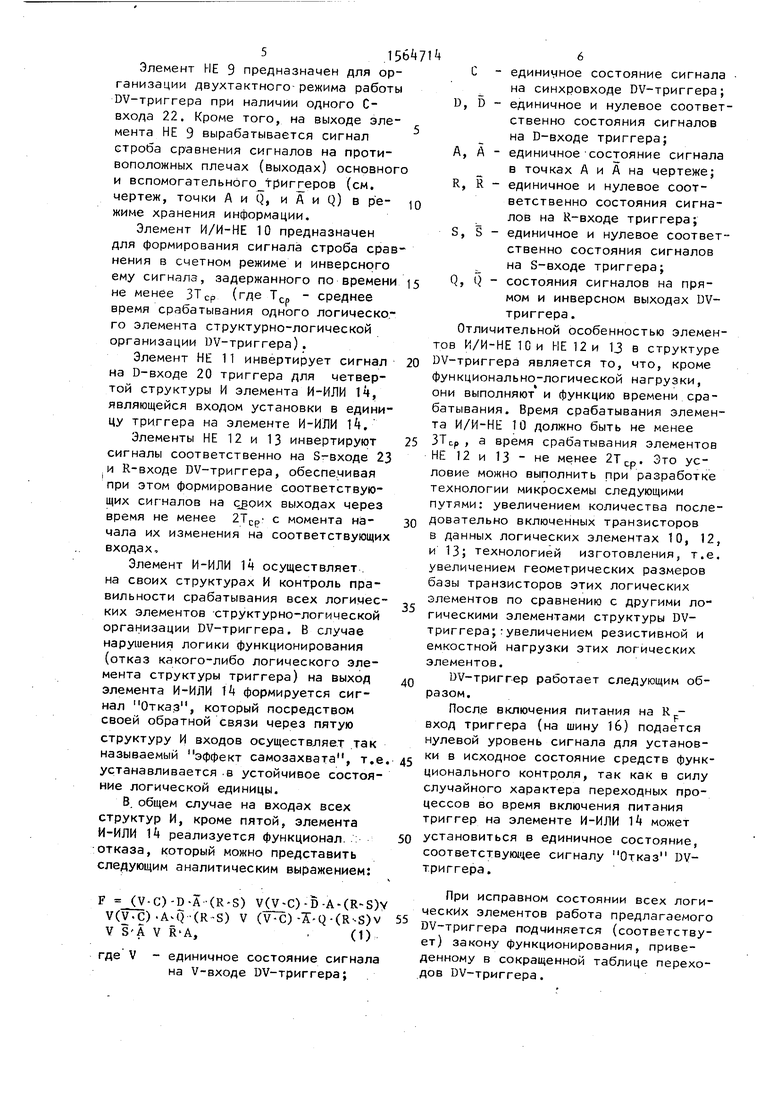

| название | год | авторы | номер документа |

|---|---|---|---|

| ДV-триггер | 1989 |

|

SU1629963A1 |

| Резервированный RS-триггер | 1989 |

|

SU1629962A1 |

| DV-триггер | 1987 |

|

SU1465936A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| IK-триггер | 1988 |

|

SU1557667A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

Изобретение относится к имульсной технике и может быть использовано в устройствах автоматики и вычислительной техники при разработке счетчиков, регистров, делителей частоты, распределителй импульсов с повышенной достоверностью функционирования. Цель изобретения - расширение функциональных возможностей - достигается за счет введения входа S 23, входа R 24, элемента И/И-НЕ 10. Устройство также содержит элементы И-НЕ 1-8, элементы НЕ 9, 11, 12, 13, элемент И-ИЛИ 14, элемент И 15, шину 16 установки, выходную шину 17, прямой 18, инверсный 19 выходы, вход D 20, вход V 21 и вход C 22. В DV-триггере дополнительно обеспечивается реализация и контроль асинхронного режима функционирования. 1 ил., 1 табл.

Авторы

Даты

1990-05-15—Публикация

1988-07-12—Подача