Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления блоками памяти, используемых в составе процессора цифровой вычислительной машины.

Цель изобретения - повышение быстродействия устройства.

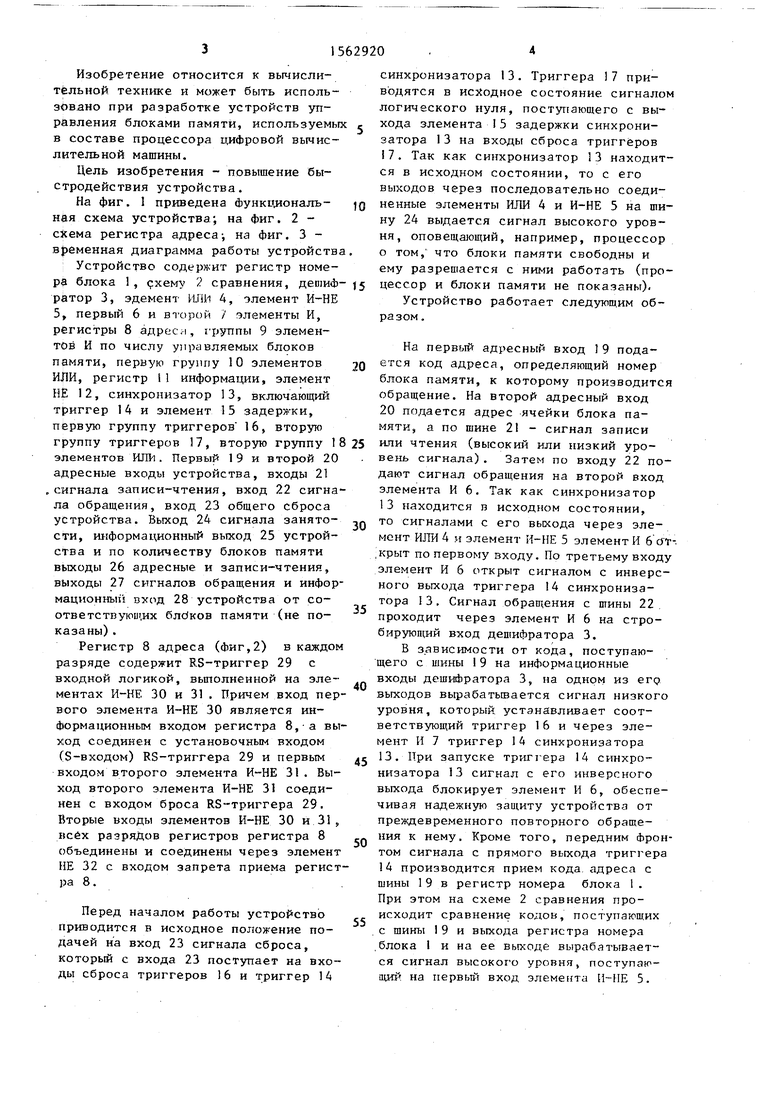

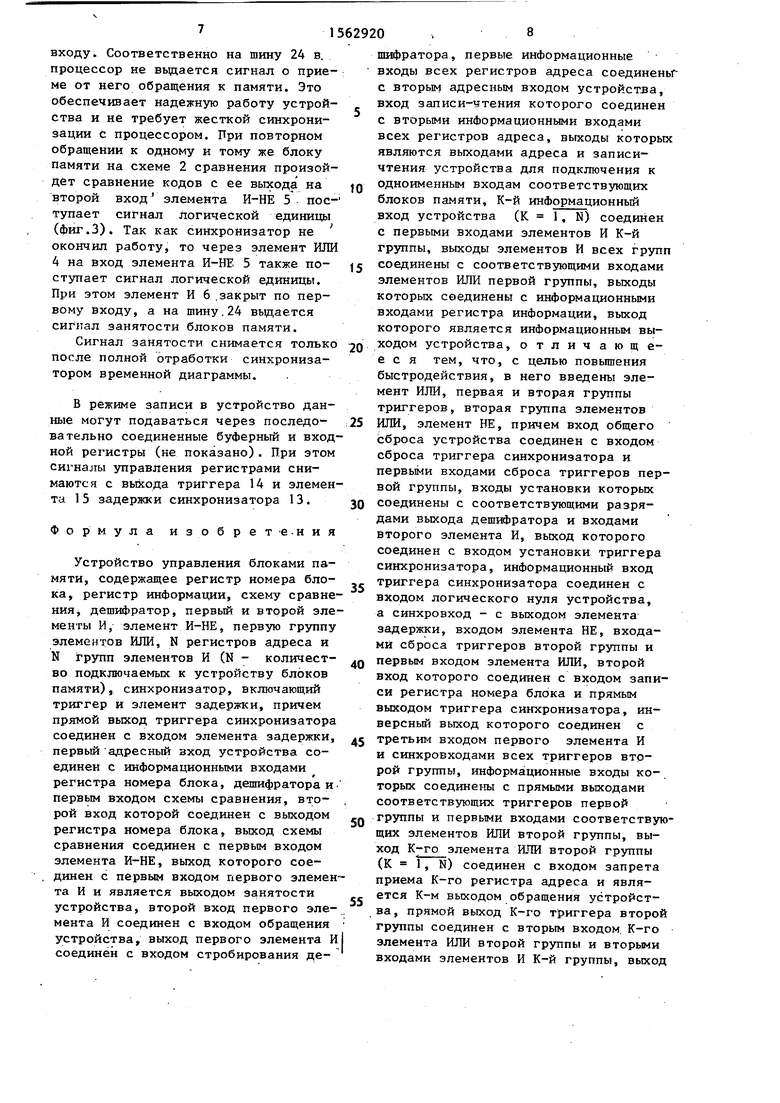

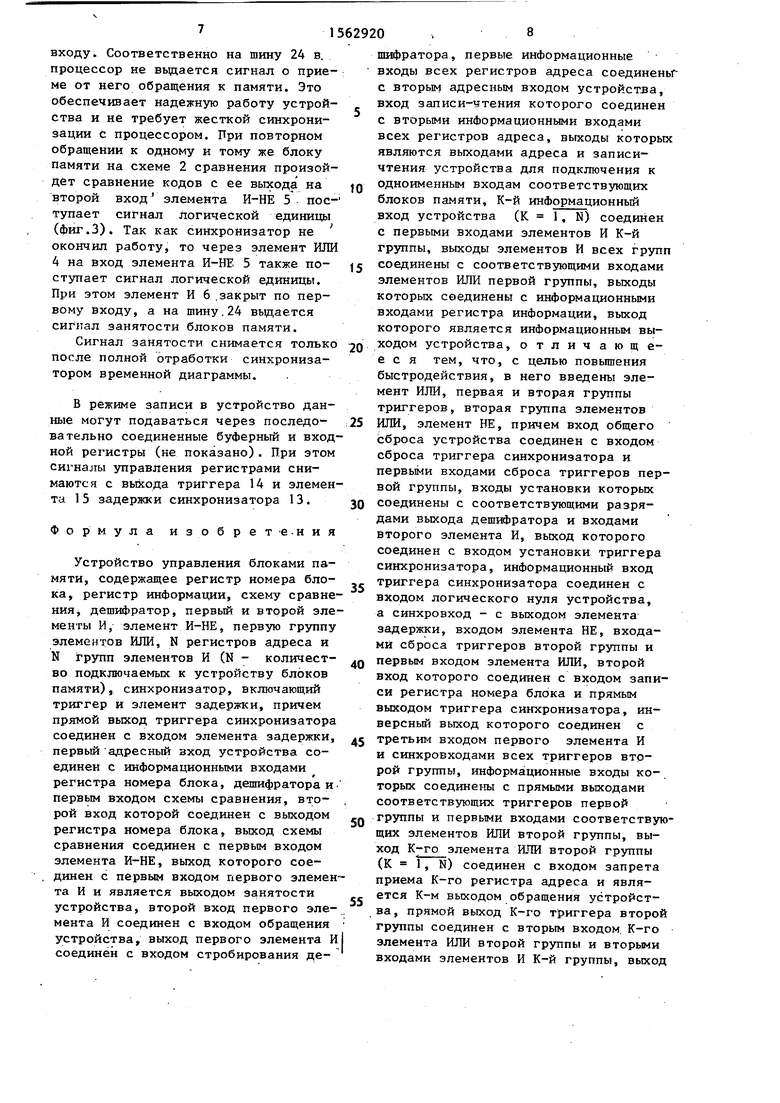

На фиг. 1 приведена функционалъ- ная схема устройства; на фиг. 2 - схема регистра адреса; на фиг. 3 - временная диаграмма работы устройства

Устройство содержит регистр номера блока 1, схему сравнения, дешиф- ратор 3, эдемен-i ШШ 4, элемент И-НЕ 5, первый 6 и второй / элементы И, регистры 8 адрес,I, группы 9 элементов И по числу управляемых блоков памяти, первую группу 10 элементов ИЛИ, регистр i1 информации, элемент НЕ 12, синхронизатор 13, включающий триггер 14 и элемент 15 задержки, первую группу триггеров 16, вторую группу триггеров 17, вторую группу 18 элементов ИЛИ. Первый 19 и второй 20 адресные входы устройства, входы 21 „сигнала записи-чтения, вход 22 сигнала обращения, вход 23 общего сброса устройства. Выход 24 сигнала занято- сти, информационный выход 25 устройства и по количеству блоков памяти выходы 26 адресные и записи-чтения, выходы 27 сигналов обращения и информационный вход 28 устройства от соответствующих бликов памяти (не показаны) .

Регистр 8 адреса (Фиг,2) в каждом разряде содержит RS-триггер 29 с входной логикой, выполненной на эле- ментах И-НЕ 30 и 31. Причем вход первого элемента И-НЕ 30 является информационным входом регистра 8, а выход соединен с установочным входом (S-входом) RS-триггера 29 и первым входом второго элемента 31. Выход второго элемента И-НЕ 31 соединен с входом броса RS-триггера 29. Вторые входы элементов И-НЕ 30 и 31 „ всех разрядов регистров регистра 8 объединены и соединены через элемент НЕ 32 с входом запрета приема регистра 8.

Перед началом работы устройство приводится в исходное положение подачей на вход 23 сигнала сброса, который с входа 23 поступает на входы сброса триггеров 16 и триггер 14

5 0 5 Q

Q

5

5

синхронизатора 13. Триггера 17 приводятся в исходное состояние сигналом логического нуля, поступающего с выхода элемента 15 задержки синхронизатора 13 на входы сброса триггеров 17. Так как синхронизатор 13 находится в исходном состоянии, то с его выходов через последовательно соединенные элементы ИЛИ 4 и И-НЕ 5 на шину 24 выдается сигнал высокого уровня, оповещающий, например, процессор о том, что блоки памяти свободны и ему разрешается с ними работать (процессор и блоки памяти не показаны).

Устройство работает следующим обра зом.

На первый адресный вход 19 подастся код адреса, определяющий номер блока памяти, к которому производится обращение. На второй адресный вход 20 подается адрес ячейки блока памяти, а по шине 21 - сигнал записи или чтения (высокий или низкий уровень сигнала). Затем по входу 22 подают сигнал обращения на второй вход элемента И 6. Так как синхронизатор

13находится в исходном состоянии, то сигналами с его выхода через элемент ИЛИ 4 ч элемент И-НЕ 5 элемент И 6 открыт по первому входу. По третьему входу элемент И 6 открыт сигналом с инверсного выхода триггера 14 синхронизатора 13. Сигнал обращения с шины 22 проходит через элемент И 6 на стро- бирующий вход дешифратора 3.

В зависимости от кода, поступающего с шины 19 на информационные входы дешифратора 3, на одном из его выходов вырабатывается сигнал низкого уровня, который устанавливает соответствующий триггер 16 и через элемент И 7 триггер 14 синхронизатора 13. При запуске трип ера 14 синхронизатора 13 сигнал с его инверсного выхода блокирует элемент И 6, обеспечивая надежную защиту устройства от преждевременного повторного обращения к нему. Кроме того, передним Фронтом сигнала с прямого выхода триггера

14производится прием кода адреса с шины 19 в регистр номера блока 1 . При этом на схеме 2 сравнения происходит сравнение кодов, поступающих с шины 19 и выхода регистра номера блока 1 и на ее выходе вырабатывается сигнал высокого уровня, поступаю- ций на первый вход элемента И-НЕ 5.

входу. Соответственно на шину 24 в. процессор не выдается сигнал о приеме от него обращения к памяти. Это обеспечивает надежную работу устройства и не требует жесткой синхронизации с процессором. При повторном обращении к одному и тому же блоку памяти на схеме 2 сравнения произойдет сравнение кодов с ее выхода на второй вход элемента И-НЕ 5 пос- тупает сигнал логической единицы (фиг.З). Так как синхронизатор не окончил работу, то через элемент ИЛИ 4 на вход элемента И-НЕ 5 также поступает сигнал логической единицы. При этом элемент И 6 .закрыт по первому входу, а на шину.24 вьщается сигнал занятости блоков памяти.

Сигнал занятости снимается только после полной отработки синхронизатором временной диаграммы.

В режиме записи в устройство данные могут подаваться через последовательно соединенные буферный и входной регистры (не показано). При этом сигналы управления регистрами снимаются с выхода триггера 14 и элемента 15 задержки синхронизатора 13.

Формула изобрете-ния

10

15

20

25

Устройство управления блоками памяти, содержащее регистр номера блока, регистр информации, схему сравнения, дешифратор, первый и второй элементы И, элемент И-НЕ, первую группу элементов ИЛИ, N регистров адреса и N групп элементов И (N - количество подключаемых к устройству блоков памяти), синхронизатор, включающий триггер и элемент задержки, причем прямой выход триггера синхронизатора соединен с входом элемента задержки, первый адресный вход устройства соединен с информационными входами регистра номера блока, дешифратора и первым входом схемы сравнения, второй вход которой соединен с выходом регистра номера блока, выход схемы сравнения соединен с первым входом элемента И-НЕ, выход которого соединен с первым входом первого элемента И и является выходом занятости устройства, второй вход первого элемента И соединен с входом обращения устройства, выход первого элемента И соединен с входом стробирования де1562920 v8

шифратора, первые информационные входы всех регистров адреса соединены с вторым адресным входом устройства, вход записи-чтения которого соединен с вторыми информационными входами всех регистров адреса, выходы которых являются выходами адреса и записи- чтения устройства для подключения к одноименным входам соответствующих блоков памяти, К-й информационный вход устройства (К 1, N) соединен с первыми входами элементов И К-й группы, выходы элементов И всех групп соединены с соответствующими входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами регистра информации, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены элемент ИЛИ, первая и вторая группы триггеров, вторая группа элементов ИЛИ, элемент НЕ, причем вход общего сброса устройства соединен с входом сброса триггера синхронизатора и первыми входами сброса триггеров первой группы, входы установки которых соединены с соответствующими разрядами выхода дешифратора и входами второго элемента И, выход которого соединен с входом установки триггера синхронизатора, информационный вход триггера синхронизатора соединен с входом логического нуля устройства, а синхровход - с выходом элемента задержки, входом элемента НЕ, входами сброса триггеров второй группы и первым входом элемента ИЛИ, второй вход которого соединен с входом записи регистра номера блока и прямым выходом триггера синхронизатора, инверсный выход которого соединен с третьим входом первого элемента И и синхровходами всех триггеров второй группы, информационные входы ко-. торых соединены с прямыми выходами соответствующих триггеров первой группы и первыми входами соответствующих элементов ИЛИ второй группы, выход К-го элемента ИЛИ второй группы (К 1, N) соединен с входом запрета приема К-го регистра адреса и является К-м выходом обращения устройст30

35

40

4S

50

55

ва, прямой выход К-го триггера второй группы соединен с вторым входом К-го элемента ИЛИ второй группы и вторыми входами элементов И К-й группы, выход

шифратора, первые информационные входы всех регистров адреса соединены с вторым адресным входом устройства, вход записи-чтения которого соединен с вторыми информационными входами всех регистров адреса, выходы которых являются выходами адреса и записи- чтения устройства для подключения к одноименным входам соответствующих блоков памяти, К-й информационный вход устройства (К 1, N) соединен с первыми входами элементов И К-й группы, выходы элементов И всех групп соединены с соответствующими входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами регистра информации, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены элемент ИЛИ, первая и вторая группы триггеров, вторая группа элементов ИЛИ, элемент НЕ, причем вход общего сброса устройства соединен с входом сброса триггера синхронизатора и первыми входами сброса триггеров первой группы, входы установки которых соединены с соответствующими разрядами выхода дешифратора и входами второго элемента И, выход которого соединен с входом установки триггера синхронизатора, информационный вход триггера синхронизатора соединен с входом логического нуля устройства, а синхровход - с выходом элемента задержки, входом элемента НЕ, входами сброса триггеров второй группы и первым входом элемента ИЛИ, второй вход которого соединен с входом записи регистра номера блока и прямым выходом триггера синхронизатора, инверсный выход которого соединен с третьим входом первого элемента И и синхровходами всех триггеров второй группы, информационные входы ко-. торых соединены с прямыми выходами соответствующих триггеров первой группы и первыми входами соответствующих элементов ИЛИ второй группы, выход К-го элемента ИЛИ второй группы (К 1, N) соединен с входом запрета приема К-го регистра адреса и является К-м выходом обращения устройст5

ва, прямой выход К-го триггера второй группы соединен с вторым входом К-го элемента ИЛИ второй группы и вторыми входами элементов И К-й группы, выход

На его втором входе сигнал такж имеет высокий уровень, так как синхрнизатор 13 запущен.

На выходе элемента И-НЕ 5 вырабатывается сигнал низкого уровня, который закрывает элемент И 6 по первому входу, а по шине 24 оповещает процес ор о приеме от него сигнала обращени и занятости блоков памяти. При этбм процессор (не показан) может снять сигнал обращения и начать формирование нового кода адреса.

При отсутствии сигнала запрета приема на входе регистра 8 адреса с выхода элемента НЕ 32 выдается сигнал высокого уровня логической единииы, который открывает элементы И-НЕ 30 и 31 по второму входу. При этом адрес с шины 20 и сигнал записи-чтения с шины 21 проходят через элементы И-НЕ 30 на S-входы, а через элементы И-НЕ 30 и 31 - на R-входы RS-триг- геров 29 регистра 8. Триггера 29 регистра 8 повторяют код, поступающий на вход регистра 8, который с их выходов поступает на соответствующий выход 26 устройства и далее на адресный вход и вход записи-чтения соответствующего блока памяти.

При запуске триггера 16 сигнал с егр прямого выхода поступает на информационный вход триггера 17, а через элемент ИЛИ 18 - на вход запрета приема регистра 8 адреса. При этом сигнал с выхода элемента НЕ 32 меняет свое значение и закрывает элементы И-НЕ 30 и 31 по второму входу, фиксируя значение кода адреса и сигнал записи-чтения в триггерах 29 регистра 8 и запрещая их изменение при изменении кода адреса на шине 20 и сигнала записи-чтения на шине 21 .

Кроме того, сигнал с выхода элемента ИЛИ 18 поступает на выход 27 и далее на вход обращения соответствующего блока памяти.

При запуске триггера J4 синхронизатора J 3 сигнал с его прямого выхода поступает на вход элемента J 5 задержки. Время задержки на нем выбрано примерно равным половине времени выборки (записи). Сигнал с выхода элемента 15 задержки поступает на синхро- вход триггера 14, информационный вход которого соединен с нулевой шиной. Передним фронтом сигнала с выхода элемента 15 задержки триггер 14 сбрасывается и открывает элемент И 6. При

0

5

0

этом синхронизатор 13 готов для прие- ема следующего сигнала обращения.

При появлении на выходе элемента 15 задержки сигнала (логическая единица) прекращается сброс триггеров 17. Передним фронтом сигнала с инверсного выхода триггера 14 синхронизатора 13 производится прием кода в триггер 37 из триггера 16. Из возбужденного триггера 16 в триггер 17 принимается логическая единица, при этом с инверсного выхода триггера 17 поступает сигнал логического нуля на

5 сброс RS-триггера 16. При сбросе триггера 16 сигнал обращения на шину 27 и сигнал запрета приема в регистр 8 формируется далее по длительности от сигнала, поступающего с прямого выхода триггера 17 на второй вход элемента ИЛИ 18. Одновременно этот же сигнал с прямого выхода триггера 17 поступает на вторые входы элементов И соответствующей группы 9 и открывает их для прохождения с шины 28 считанной информации из возбужденного блока памяти на входы элементов ИЛИ группы 10, С их выхода считанные данные поступают на информационные входы ре0 гистра 11 информации.

Задним фронтом сигнала с выхода элемента НЕ 12 производится прием данных в регистр 11 и передача их на шину 25 устройства.

Подача на устройство нового значения адреса возможна после установки триггера 54 синхронизатора 13. Одновременно при этом блокируется изменение кода адреса в возбужденном регистре адреса установкой соответствующего триггера Ib. При подаче нового кода адреса к другому блоку памяти на схеме 2 сравнения не происходит и на выходе этой схемы вырабатывается сиг5 нал логического нуля, который через элемент И-НЕ 5 открывает по первому входу элемент И 6 и выдает сигнал по шине 24 о незанятости соответствующего блока памяти, т.е. разрешение на обращение к устройству со стороны, например, процессора. Однако при выставлении процессором сигнала обращения на шину 22 устройства послед- . нее воспримет этот сигнал толькр после отработки временного интервала элементом 15 задержки и сбросом соответственно триггера 14 синхронизатора 13 (фиг.З), сигнал с которого открывает элемент И 6 по третьему

5

0

0

элемента НЕ оединен с входом записи регистра информации, а выход элемента ИЛИ соединрн с вторым входом элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления блоками памяти, используемых в составе процессора цифровой вычислительной машины. Цель изобретения - повышение быстродействия устройства. Устройство содержит регистр 1 номера блока, схему 2 сравнения, дешифратор 3, элемент ИЛИ 4, элемент И-НЕ 5, первый 6, второй 7 элементы И, регистр 8 адреса, группу 9 элементов И по числу управляемых блоков памяти, первую группу 10 элементов ИЛИ, регистр 11 информации, элемент НЕ 12, синхронизатор 13, включающий триггер 14 и элемент 15 задержки, первую группу триггеров 16, вторую группу триггеров 17, вторую группу 18 элементов ИЛИ. Устройство обеспечивает возможность смены адреса и сигнала записи-чтения сразу после приема им сигнала обращения. 3 ил.

Обращ 22

Адрес

20,19

Тгп Зл-m задержки 15

вых или 18 Обращеик1-шбП

дых ИЛИ 1Ј

Обращениек7-увл

Выход 25

Выход

Фиг. 2

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления блоками памяти | 1985 |

|

SU1298799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-06—Подача