(21 ) 4461566/24-24

(22) 15.07.88

(46) ОУ.Об.РО.Бюл, Р 21

(71)Харьковский политехнический институт им. В.И.Ленина

(72)А.В.Куклов, Я.В.Никитин, В.И.Август, И.С.Зыков и Н.А.Иванюк

(53)681.327.6 (088.8)

(56)Авторское свидетельство СССР №1092569, кл. G 11 С 29/00, 1984.

Авторское свидетельство СССР №1256099, кл. О 11 С 29/00, 1986.

(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может быть использовано при отладке и функциональном контроле блоков памяти. Целью изобретения является повышение быстродействия устройства и расширение области его применения за счет увеличения

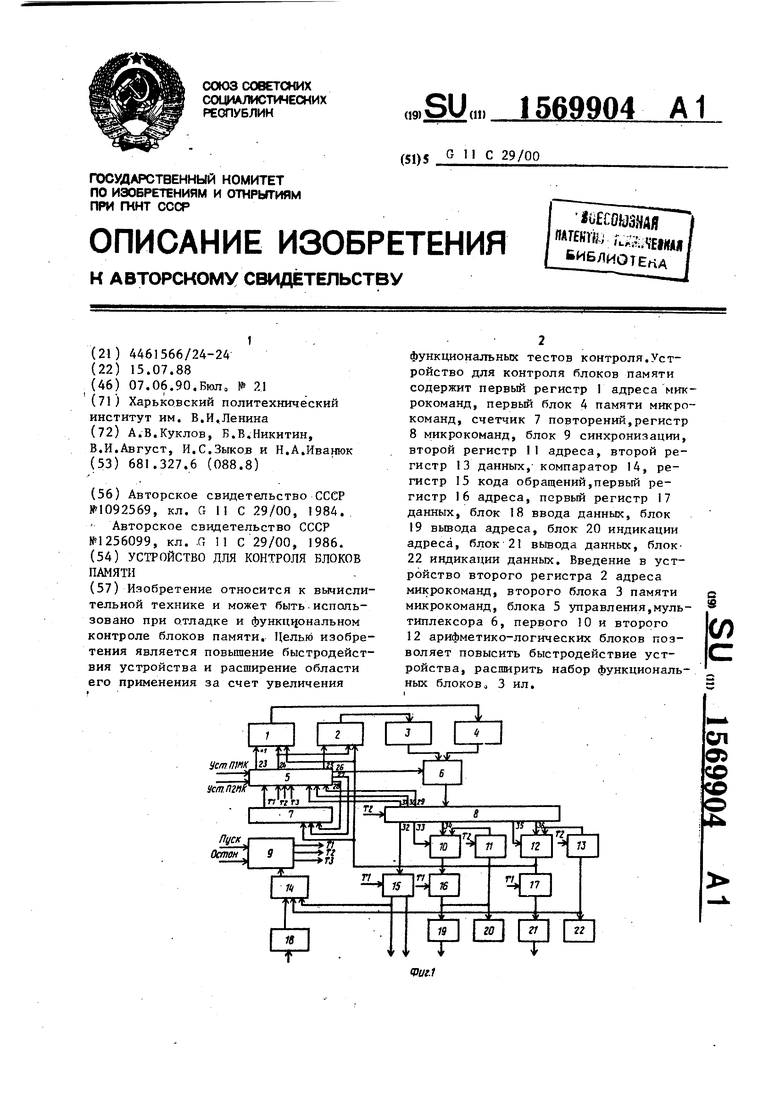

функциональных тестов контроля.УСТРОЙСТВО для контроля блоков памяти содержит первый регистр I адреса микрокоманд, первый блок 4 памяти микрокоманд, счетчик 7 повторений,регистр 8 микрокоманд, блок 9 синхронизации, второй регистр 11 адреса, второй регистр 13 данных, компаратор 14, регистр 15 кода обращений,первый регистр 16 адреса, первый регистр 17 данных, блок 18 ввода данных, блок 19 вывода адреса, блок 20 индикации адреса, блок 21 вывода данных, блок 22 индикации данных. Введение в устройство второго регистра 2 адреса микрокоманд, второго блока 3 памяти микрокоманд, блока 5 управления,мультиплексора 6, первого 10 и второго 12 арифметико-логических блоков позволяет повысить быстродействие устройства, расширить набор функциональных блоковj 3 ил.

с S

(Л

Изобретение относится к вычислительной технике и может быть использовано при отладке и функциональном контроле блоков памяти.

Цель изобретения - повышение быстродействия устройства и расширение области применения устройства за счет увеличения функциональных тестов контроля.

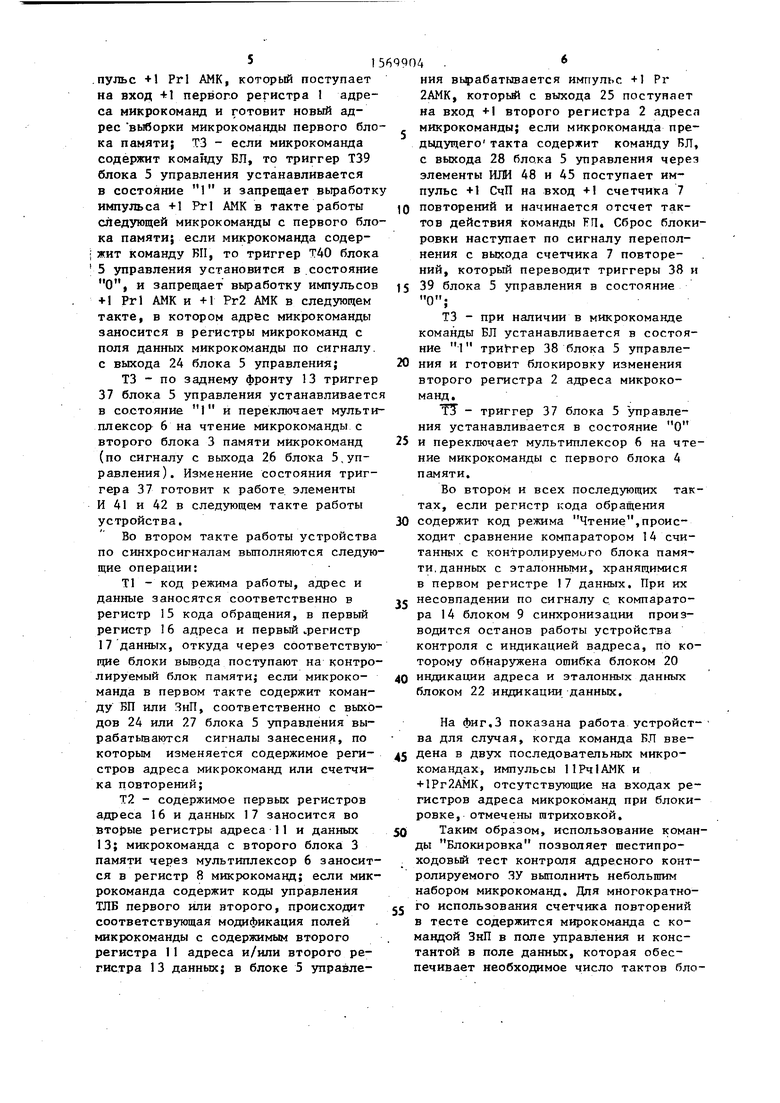

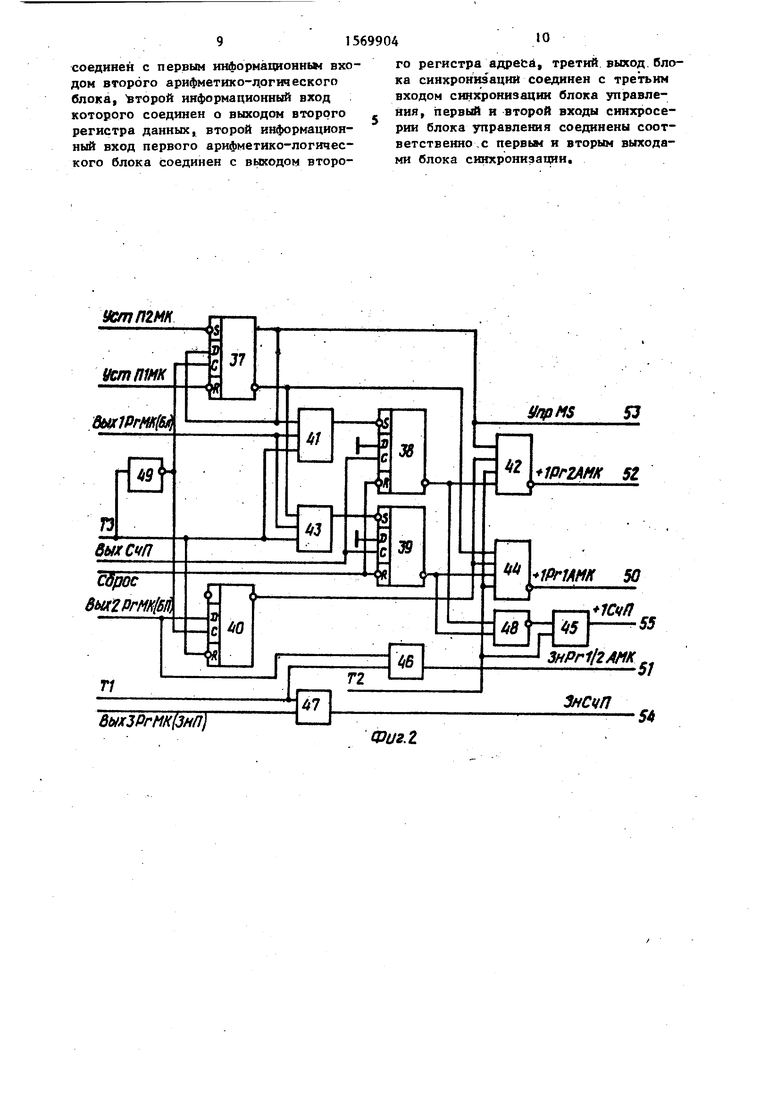

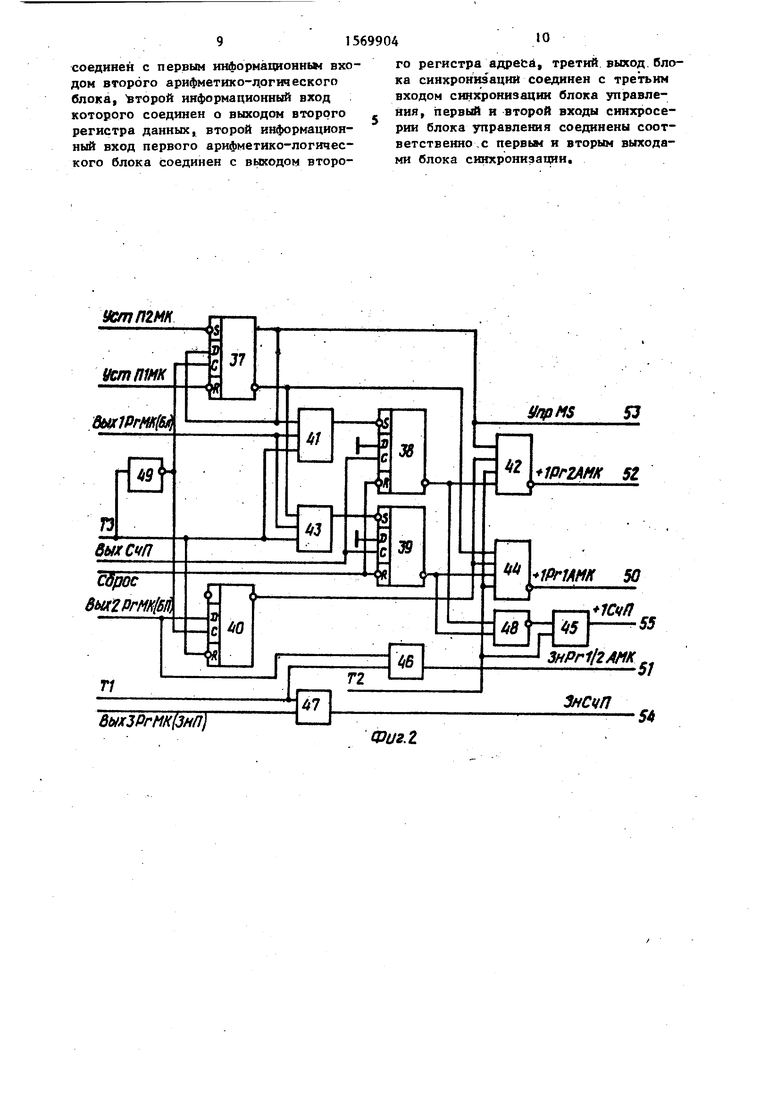

На фиг.1 представлена структурная схема устройства для контроля блоков памяти; на фиг.2 - принципиальная схема блока управления; на фиг.З - временная диаграмма работы устройства.

Устройство для контроля блоков памяти (фиг.1) содержит первый 1 и второй 2 регистры адреса микрокоманд, второй 3 и первый 4 блоки памяти и микрокоманд, блок 5 управления,мультиплексор 6, счетчик 7 повторений,регистр 8 микрокоманд, блок 9 синхронизации, первый арифметико-логический блок 10, второй регистр 11 адреса, второй арифметико-логический блок 12, второй регистр 13 данных, компаратор 14, регистр 15 кода обращений,первый регистр 16 адреса, Первый регистр 17 данных, блок 18 ввода данных, блок 19 вывода адреса, блок 20 индикации адреса, блок 21 вывода данных,блок 22 индикации данных, выходы 23-36 блока управления и регистра микрокоманд. Блок управления (фиг.2) содержит четыре триггера 37-40, семь элементов И 41-47, два элемента ИЛИ 48 и 49, выходы 50-55.

Блок памяти служит для повышения частоты контроля в два раза, реализован как и первый блок памяти на микросхемах 132PV5, тип микросхем определяется требуемой частотой контроля. Второй регистр адреса микрокоманд служит для выработки адреса второй памяти микрокоманд, реализова на микросхемах серии 530ИЕ17. В первом и втором регистрах адреса микрокоманд использованы стандартные входы счетчиков и регистров: информационный, записи и счетный +1. Мультиплексор служит для поочередного считывания микрокоманд с первого и второго блоков памяти микрокоманд и реализован на мультиплексорах серии 530КП11, первый и второй арифметико- логические блоки (MIR) служат для модификации адреса или данных при записи, в контролируемое устройство

0

5

0

5

0

5

0

5

и при чтении из него, АЛБ реализованы на микросхемах 530 серии 5300ИШ.

Блок управления реализован на микросхемах серии 530.

Устройство для контроля,блоков памяти работает следующим образом.

Перед пуском контроля проводится установка в исходное состояние: обнуляются регистр микрокоманд, первый и второй регистр адреса и данных,заносятся требуемые тесты в виде набора микрокоманд в первый и второй блоки памяти микрокоманд, устанавливаются в О состояние триггеры 38 и 39, а также устанавливается триггер 37, состояние которого определяет номер блока памяти микрокоманд, с которого по пуску начинается считывание первой микрокоманды. В состав микрокоманды входят четыре поля: адреса, данных, режима работы контролируемого устройства, поле управления. Поле режима контролируемого блока памяти содержит коды считывания, коды сигналов обращения: записи (ЗП) или чтения (Чт) и выбора кристалла (ВК). Поле адреса и данных содержит адрес ячейки контролируемого блока памяти и данные, которые либо записываются по заданному адресу при записи, либо используются как эталонные при сравнении со считанной информацией при чтении,, Поле управления содержит один или несколько независимых -кодов операций, определяющих режим работы отдельных блоков устройства контроля.

По сигналу пуска начинают вырабатываться импульсы синхронизации Т1 - ТЗ, задающие моменты занесения инсЪормации в блоки устройства контроля в каждом такте его работы. На фиг.З приведена временная диаграмма работы устройства при наличии в поле управления микрокоманды команд: Блокировка (БЛ), Безусловный переход (ВП), Занесение кода в счетчик повторений (ЗнП).

В первом такте работы устройства при установке начала работы с первого блока памяти (триггер 37 в состоянии О) ую синхросигналам выполняются следующие операции:

Т2 - микрокоманда с первого блока 4 памяти через мультиплексор 6 заносится в регистр 8 микрокоманд; в блоке 5 управления вырабатывчется импульс +1 Prl AMK, который поступает на вход +1 первого регистра I адреса микрокоманд и готовит новый адрес выборки микрокоманды первого блока памяти; ТЗ - если микрокоманда содержит команду БЛ, то триггер Т39 блока 5 управления устанавливается в состояние 1 и запрещает выработку импульса +1 Prl AMK в такте работы следующей микрокоманды с первого блока памяти; если микрокоманда содержит команду fill, то триггер Т40 блока 5 управления установится в состояние О, и запрещает выработку импульсов +1 Prl AMK и +1 Pr2 AMK в следующем такте, в котором адрес микрокоманды заносится в регистры микрокоманд с поля данных микрокоманды по сигналу с выхода 24 блока 5 управления;

ТЗ - по заднему фронту 13 триггер 37 блока 5 управления устанавливается в состояние 1 и переключает мультиплексор 6 на чтение микрокоманды с второго блока 3 памяти микрокоманд (по сигналу с выхода 26 блока 5 управления). Изменение состояния триггера 37 готовит к работе элементы И 41 и 42 в следующем такте работы устройства.

Во втором такте работы устройства по синхросигналам выполняются следующие операции:

Т1 - код режима работы, адрес и данные заносятся соответственно Р регистр 15 кода обращения, в первый регистр 16 адреса и первый „регистр 17 данных, откуда через соответствующие блоки вывода поступают на контролируемый блок памяти; если микрокоманда в первом такте содержит команду БП или ЯнП, соответственно с выходов 24 или 27 блока 5 управления вырабатываются сигналы занесения, по которым изменяется содержимое регистров адреса микрокоманд или счетчика повторений;

Т2 - содержимое первых регистров адреса 16 и данных 17 заносится во вторые регистры адреса 11 и данных 13; микрокоманда с второго блока 3 памяти через мультиплексор 6 заносится в регистр 8 микрокоманд; если микрокоманда содержит коды управления ТЛБ первого или второго, происходит соответствующая модификация полей микрокоманды с содержимым второго регистра 11 адреса и/или второго регистра 13 данных; в блоке 5 управле0

5

ния вьрабатывается импульс +1 Рг 2АМК, который с выхода 25 поступает на вход -И второго регистра 2 адреса микрокоманды; если микрокоманда предыдущего1 такта содержит команду БЛ, с выхода 28 блока 5 управления через элементы ИЛИ 48 и 45 поступает импульс +1 СчП на вход +1 счетчика 7 повторений и начинается отсчет тактов действия команды FF1. Сброс блокировки наступает по сигналу переполнения с выхода счетчика 7 повторений, который переводит триггеры 38 и 39 блока 5 управления в состояние

ТЗ - при наличии в микрокоманде команды БЛ устанавливается в состояние 1 триггер 38 блока 5 управле- 0 ния и готовит блокировку изменения второго регистра 2 адреса микрокоманд.

ТЗ - триггер 37 блока 5 управления устанавливается в состояние О и переключает мультиплексор 6 на чтение микрокоманды с первого блока 4 памяти.

Во втором и всех последующих тактах, если регистр кода обращения содержит код режима Чтение,происходит сравнение компаратором 14 считанных с контролируемого блока памяти данных с эталонными, хранящимися в первом регистре 17 данных. При их несовпадении по сигналу с компаратора 14 блоком 9 синхронизации производится останов работы устройства контроля с индикацией вадреса, по которому обнаружена ошибка блоком 20 индикации адреса и эталонных данных блоком 22 индикации данных.

5

0

5

5

0

На фиг.З показана работа устройства для случая, когда команда БЛ введена в двух последовательных микрокомандах, импульсы 11Рч1АМК и +1Рг2АМК, отсутствующие на входах регистров адреса микрокоманд при блокировке, отмечены штриховкой.

Таким образом, использование команды Блокировка позволяет тестипро- ходовый тест контроля адресного контролируемого ЯУ выполнить небольшим набором микрокоманд. Для многократного использования счетчика повторений в тесте содержится мирокоманда с командой ЗнП в поле управления и константой в поле данных, которая обеспечивает необходимое число тактов блокировхи в зависимости от емкости контролируемой памяти. Для многократного повторения теста по 17 адресу первого блока памяти занесена микроко- манда с БП и нулевым адресом перехода в поле данных. Чтобы обеспечить переход на микрокоманду нулевого ад- ресс. первого блока памяти, необходима холостая команда по 17 адресу вто- рого блока памяти. Но так как переход осуществляется на микрокоманду с блокировкой, то в холостую микрокоманду введена команда занесения в.счетчик повторений ЯнП для выполнения первой операции теста запись кода О

Формула изобретения

Устройство для контроля блоков памяти, содержащее первый регистр адреса микрокоманд, первый блок памяти микрокоманд, регистр /микрокоманд, первый и второй регистры адреса,первый и второй регистр л данных, регистр кода обращений, компаратор,счетчик повторений, блок синхронизации,причем выход первого регистра адреса микрокоманд соединен с адресным входом первого блока памяти микрокоманд, четвертый выход регистра микрокоманд соединен с информационным входом регистра кода обращения, выход которого соединен с управляющим входом компаратора и является выходом задания режима устройства, выход первого регистра адреса соединен с информационным входом второго регистра адреса и является адресным выходом устройства, выход первого регистра данных соединен с информационным входом второго регистра данных, с первым информационным входом компаратора и является информационным выходом устройства, второй информационный вход ком- паратора является информационным входом устройства, выход компаратора соединен с управляющим входом блока синхронизации, входы пуска и останова которого являются одноимен- ными входами устройства, первый выход блока синхронизации соединен с управляющими входами регистра кода обращения, первого регистра адреса и первого регистра данных, второй выход блока синхронизации соединен с управляющими входами регистра микрокоманд, второго регистра адреса и второго регистра данных, отличающеес я тем, что, с целью повышения быстродействия устройства и .расширения области применения устройства за счет увеличения числа функциональных тестов контроля, в него введены второй регистр адреса микрокоманд, второй блок памяти микрокоманд, мультиплексор, блок управления, первый и второй арифметико-логические блоки,причем выход второго регистра адреса микрокоманд соединен с адресным входом второго блока памяти микрокоманд,вы- ход которого соединен с вторым информационным входом мультиплексора, первый информационный вход которого соединен с выходом первого блока памяти микрокоманд, управляющий вход мультиплексора соединен с четвертым выходом блока управления, первый выход которого соединен со счетным входом первого регистра адреса микрокоманд, вход записи которого соединен с одноименным входом второго регистра адреса микрокоманд и вторым выходом блока управления, третий выход которого соединен со счетным входом второго регистра адреса микрокоманд, информационный вход которого соединен с одноименными входами первого регистра адреса микрокоманд и счетчика повторений, с информационным входом первого регистра данных и выходом второго арифметико-аналогового блока, управляющий вход которого соединен с седьмым выходом регистра микрокоманд, информационный вход которого соединен с выходом мультиплексора, шестой выход блока управления соединен со счетным входом счетчика повторений, вход записи которого соединен с пятым выходом блока управления, первый и второй установочные входы являются одноименными входами устройства, выход переполнения счетчика повторений соединен с входом сброса блокировки блока управления,первый вход блокировки которого соединен с первым выходом регистра микрокоманд, второй выход которого соединен с вторым входом блокировки блока управления, вход разрешения записи которого соединен с третьим выходом регистра микрокоманд, пятый выход которого соединен с управляющим входом первого арифметико-логического блока, первый информационный вход которого соединен с шестым выходом регистра микрокоманд, восьмой выход которого

соединен с первым информационна входом второго арифметико-догического блока, второй информационный вход которого соединен о выходом второго регистра данных, второй информационный вход первого арифметико-логического блока соединен с выходом второго регистра адреса, третий выход блока синхронизации соединен с третьим входом синхронизации блока управления, первый и второй входы синхросе- рии блока управления соединены соответственно с первым и вторым выходами блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1092569A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке и функциональном контроле блоков памяти. Целью изобретения является повышение быстродействия устройства и расширение области его применения за счет увеличения функциональных тестов контроля. Устройство для контроля блоков памяти содержит первый регистр 1 адреса микрокоманд, первый блок 4 памяти микрокоманд, счетчик 7 повторений, регистр 8 микрокоманд, блок 9 синхронизации, второй регистр 11 адреса, второй регистр 13 данных, компаратор 14, регистр 15 кода обращений, первый регистр 16 адреса, первый регистр 17 данных, блок 18 ввода данных, блок 19 вывода адреса, блок 20 индикации адреса, блок 21 вывода данных, блок 22 индикации данных. Введение в устройство второго регистра 2 адреса микрокоманд, второго блока 3 памяти микрокоманд, блока 5 управления, мультиплексора 6, первого 10 и второго 12 арифметико-логических блоков позволяет повысить быстродействие устройства, расширить набор функциональных блоков. 3 ил.

у&ппгмк

усттмк

J7

вЫХ1РгМК№

4/

43

тз

4J

быхСчП

Сброс

6ых2РгМК{бП

40

77

U1

ВыхЗРгМК(ЗнЩ

Л

УпрМ5

57

k

ЮГ2АМК 51

39

Ы

+1РГ1АМК 50

ЬВ

+1СчП

45

55

Т2

46

toPrtfrWK

51

ЭнСчП

54

Фиг.1

Ј

5Ј.

«йк «

Ш%1

3

Ј

5Ј.

§1

Авторы

Даты

1990-06-07—Публикация

1988-07-15—Подача