I

;

Изобретение относится к вычислительной технике и может быть применено для быстрого преобразования чисел из десятичной системы счисления в двоичную.Целью изобретения является повышение быстродействия. Для этого, в преобразователе двоично-десятичного кода в двоичный, содержащем сдвиговый регистр 1, блоки 2 памяти, блоки 3, 5 суммирования, промежуточный регистр 4, выходы регистра 4 соединены с входами блока 3. 1 ил.

м

Ё

О

ел со

GJ

00 XI

т

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные.

Целью изобретения является повышение быстродействия.

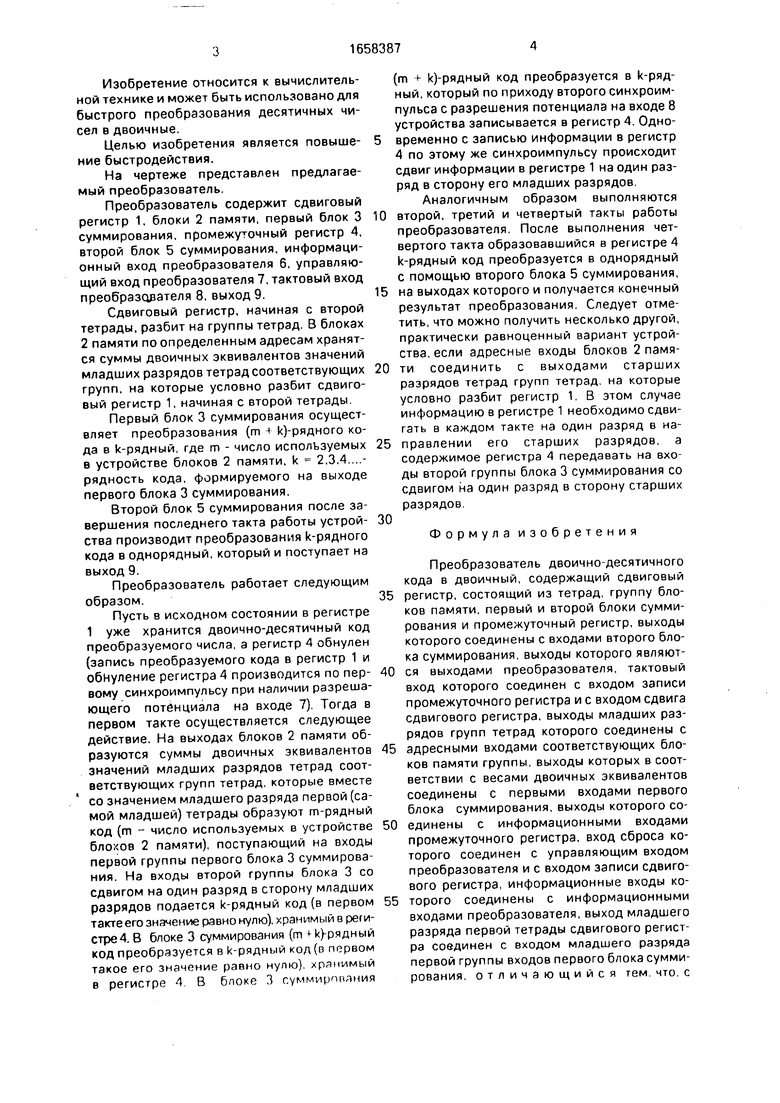

На чертеже представлен предлагаемый преобразователь.

Преобразователь содержит сдвиговый регистр 1, блоки 2 памяти, первый блок 3 суммирования, промежуточный регистр 4, второй блок 5 суммирования, информационный вход преобразователя 6, управляющий вход преобразователя 7, тактовый вход преобразователя 8, выход 9.

Сдвиговый регистр, начиная с второй тетрады, разбит на группы тетрад. В блоках 2 памяти по определенным адресам хранятся суммы двоичных эквивалентов значений младших разрядов тетрад соответствующих групп, на которые условно разбит сдвиговый регистр 1, начиная с второй тетрады.

Первый блок 3 суммирования осуществляет преобразования (m к)-рядного кода в k-рядный, где т - число используемых в устройстве блоков 2 памяти, k 2,3,4....- рядность кода, формируемого на выходе первого блока 3 суммирования.

Второй блок 5 суммирования после завершения последнего такта работы устройства производит преобразования k-рядного кода в однорядный, который и поступает на выход 9.

Преобразователь работает следующим образом.

Пусть в исходном состоянии в регистре 1 уже хранится двоично-десятичный код преобразуемого числа, а регистр 4 обнулен (запись преобразуемого кода в регистр 1 и обнуление регистра 4 производится по первому синхроимпульсу при наличии разрешающего потенциала на входе 7). Тогда в первом такте осуществляется следующее действие. На выходах блоков 2 памяти образуются суммы двоичных эквивалентов значений младших разрядов тетрад соответствующих групп тетрад, которые вместе со значением младшего разряда первой (самой младшей) тетрады образуют гл-рядный код (т - число используемых в устройстве блоков 2 памяти), поступающий на входы первой группы первого блока 3 суммирования. На входы второй группы блока 3 со сдвигом на один разряд в сторону младших разрядов подается k-рядный код (в первом такте его значение равно нулю), хранимый в реги- стре4. В блоке 3 суммирования (т к)-рядный код преобразуется в k-рядный код (в первом такое его значение равно нулю), хранимый в регистре 4 В блоке 3 суммирования

(т + к)-рядный код преобразуется в k-рядный, который по приходу второго синхроимпульса с разрешения потенциала на входе 8 устройства записывается в регистр 4. Одновременно с записью информации в регистр 4 по этому же синхроимпульсу происходит сдвиг информации в регистре 1 на один разряд в сторону его младших разрядов.

Аналогичным образом выполняются

второй, третий и четвертый такты работы преобразователя, После выполнения четвертого такта образовавшийся в регистре 4 k-рядный код преобразуется в однорядный с помощью второго блока 5 суммирования,

на выходах которого и получается конечный результат преобразования. Следует отметить, что можно получить несколько другой, практически равноценный вариант устройства, если адресные входы блоков 2 памяти соединить с выходами старших разрядов тетрад групп тетрад, на которые условно разбит регистр 1. В этом случае информацию в регистре 1 необходимо сдвигать в каждом такте на один разряд в направлении его старших разрядов, а содержимое регистра 4 передавать на входы второй группы блока 3 суммирования со сдвигом на один разряд в сторону старших разрядов.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий сдвиговый

регистр, состоящий из тетрад, группу блоков памяти, первый и второй блоки суммирования и промежуточный регистр, выходы которого соединены с входами второго блока суммирования, выходы которого являются выходами преобразователя, тактовый вход которого соединен с входом записи промежуточного регистра и с входом сдвига сдвигового регистра, выходы младших разрядов групп тетрад которого соединены с

адресными входами соответствующих блоков памяти группы, выходы которых в соответствии с весами двоичных эквивалентов соединены с первыми входами первого блока суммирования, выходы которого соединены с информационными входами промежуточного регистра, вход сброса которого соединен с управляющим входом преобразователя и с входом записи сдвигового регистра, информационные входы которого соединены с информационными входами преобразователя, выход младшего разряда первой тетрады сдвигового регистра соединен с входом младшего разряда первой группы входов первого блока суммирования, отличающийся тем. что, с

целью повышения быстродействия, в нем ны с второй группой входов первого блока выходы промежуточного регистра соедине- суммирования.

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

Авторы

Даты

1991-06-23—Публикация

1988-05-16—Подача