Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные.

Целью изобретения является упрощение преобразователя.

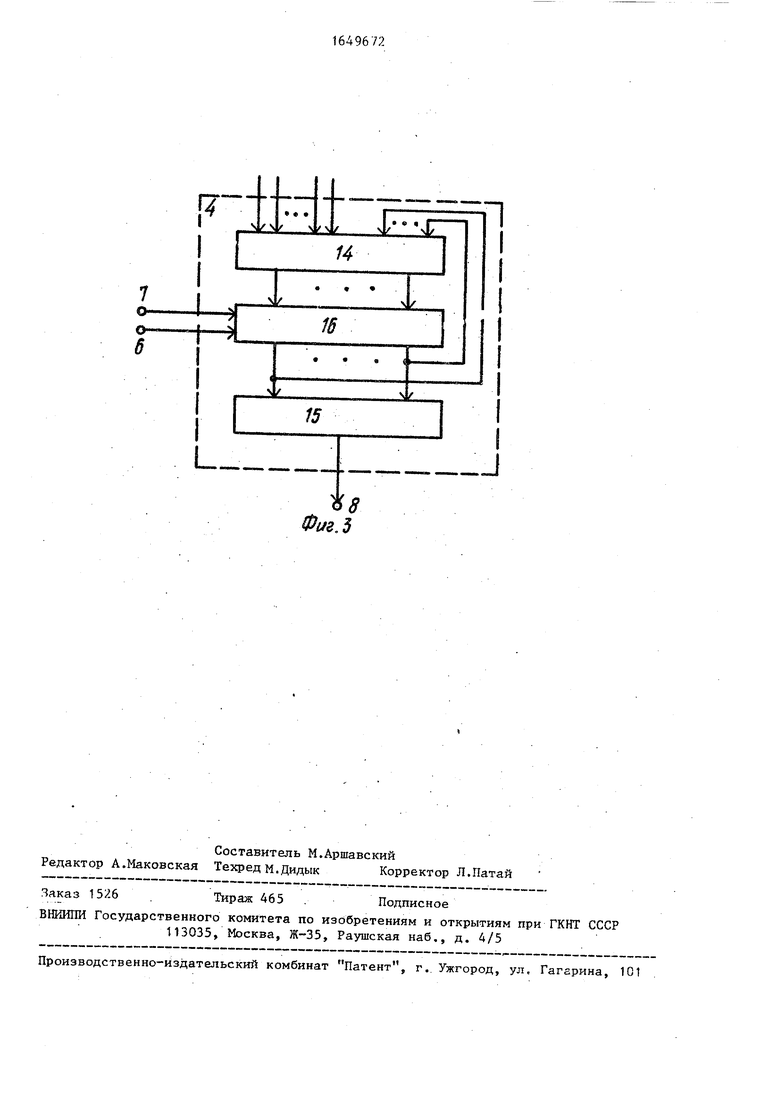

На фиг. 1 приведена структурная схема предлагаемого преобразователя двоично-десятичного кода в двоичный; на фиг. 2 - схема узла преобразования j на фиг. 3 - схема блока накопления .

Преобразователь двоично-десятичного кода в двоичный (фиг. 1) содержит группу 1 блоков ) + преобразования параллельного двоично-десятичного кода в последовательный двоичный, блоки 3.j-3m памяти, блок 4 накопления, информационный вход 5 преобразователя, управляющий 6 и тактовый 7 входы преобразователя, выход 8 преобразователя .

Елок 2j преобразования Јj - (mk+ H)f (фиг. 2) содержит коммутатор 9 j , регистр 10J и делитель на два 11j (вы- ходом младшего разряда регистра 10 является выход , а выходом делителя на два It: - выход 13,) .

Клок 4 накопления (фиг.З) содержит первый 14 и второй 15 узлы суммирования, регистр 16.

Блок / предназначен для преобразования соответствующих тетрад исходного двоично-десятичного кода (, 3...) в двоичный код. Преобразование может быть осуществлено различными методами, в частности методом последовательного деления преобразуемого кода на два (именно этот метод и предполагается на фиг. 2). Коммутатор 9 пропускает информацию или с входа 5 или с выхода 13j делителя 11.

В блоках 3,-Зт эквивалентов по определенным адресам хранятся суммы

&

Ј СО Ф ГС

двоичных Элвивалегтов значений разрядов, формируемых в каждом такте на выходах соответствующих блоков 2 преобразования,с

Блок 4 предназначен для суммирования и накопления информации, поступающей в каждом такте с выходов блоков эквивалентов и младшего блока тк-н преобразования. Блок состоит из 1 первого узла 14 суммирования, осуществляющего преобразование (m+q)-рядного кода в q-рядный (,3,4... - рядность кода, формируемого на выходе первого узла 14 суммирования), регист-1 ра 16, предназначенного для хранения результата, формируемого в каждом такте на выходах первого узла 14 суммирования в q-рядном коде и второго узла 15 суммирования, который производит пре- 2 образование q-рядногокода в однорядный после завершения последнего такта работы устройства.

Преобразователь работает следующим образом,( 2

Пусть в исходном состоянии в регистрах К -10ткч., блоков 24-2ткч. преобразования группы 1 уже хранится двоично-десятичный код преобразуемого в двоичную систему десятичного числа, -J а регистр 16 блока 4 накопления обнулен (запись информации в регистры Ю,,- и обнуление регистра 16 производится по первому синхроимпульсу при «аличии разрешающих потенциалов на входах 6,7 устройства). Тогда в первом такте на выходах блоков , эквивалентов образуются суммы двоичных эквивалентов значений разрядов, сформированных ка выходах соответствующих k блоков 2 преобразования, которые вместе со значением разряда младшего блока 2ткл, преобргпования образуют т-рядный код (разряд блока (к-м не увеличивает рядность кода), поступаю- щий на информационный вход блока 4 накопления, являющийся второй группой входов его первого узла 14 суммирования. На входы первой группы входов узла 14 подается содержимое регистра 16 в q- рядном коде (в первом такте оно равно нулю) со сдвигом на один разряд в сторону старших разрядов. В узле 14 (m+q)-рядный код преобразуется вq-рядный, который в конце такта записывается -з регистр 16 блока 4 накопления. Одновременно с работой блоков и блока 4 накопления в блпках /. ,,-2 тк.ц осуществляется следующий цикл преобразования соответствующих групп тетрад в двоичный код, в результате чего после завершения такта на выходах блоков 2/)-2mk4, преобразования будут присутствовать очередные разряды двоичных кодов преобразуемых групп тетрад. Запись информации в регистры l -l mfc+1 блоков .mlcttH в регистр 16 блока 4 осуществляется по одному и тому же синхроимпульсу при наличии разрешающего потенциала на входе 7 устройства. На этом первый такт работы заканчивается и аналогичным образом выполняется следующий такт. Общее число тактов равно fnlogJO (п - число тетрад исходного двоично- десятичного кода, преобразуемых в одном блоке 2).

После выполнения JnloR21)Ј тактов работы преобразователя образовавшийся в регистре 16 q-рядный код преобразуется в однорядный с помощью второго узла 15 суммирования, на выходе которого и получается конечный результат преобразования, поступающий на выход 8 устройства.

Формула изобретения

1. Преобразователь двоично-десятичного кода в двоичный, содержащий группу из m блоков памяти (,2, . . .) и блок накопления, выходы которого являются выходами преобразователя, управляющий вход которого соединен с входом сброса блока накопления, информационные входы которого соединены с выходами блоков памяти группы в соответствии с весами двоичных эквивалентов, тактовый вход преобразователя соединен с входом записи блока накопления, отличающийся тем, что, с целью упрощения преобразователя, он содержит группу из (mk+1) блоков преобразования параллельного двоично-десятичного кода в последовательный двоичный, где k - число адресных входов одного блока памяти, причем адресные входы 1-го блока памяти () соединены с выходами блоксь преобразования параллельного двоично-десятичного кода в последовательный двоичный с Ј(i-1)k+lj-ro по Ј(i-1) групп, выход (rok+1)-r блока преобразования параллельного двоично-десятичного кода в последовательный двоичный код соединен с входом младшего разряда информационного

к

вход блока накопления5 информационные входы преобразователя соединены с информационными входами блоков преобразования параллельного двоично-де сятичного кодл в последовательный двоичный, входы коммутации которых соединены с управляющим входом преоб разователя, тактовый вход которого соединен с входами записи преобразователей параллельного двоично-десятичного кода в последовательный двоичный .

2. Преобразователь по п. отличающийся тем, что в нем блок преобразования параллельного двоично-десятичного кода в последовательный двоичный содержит регистр,

делитель на два и коммутатор, первый информационный вход которого является информационным входом блока преобразования параллельного двоично-десятичного кода в последовательный двоичный, выход коммутатора соединен с информационным входом регистра, выход которого соединен с входом делителя на два, выход которого соединен с вторым информационным входом коммутатора, выход младшего разряда регистра является выходом блока преобразования параллельного двоичного кода в последовательный двоичный, вход записи и коммутации которого соединены соответственно с входом записи регистра и управляющим входом коммутатора.

10

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1662004A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1658387A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого преобразования чисел из десятичной системы счисления в двоичную. Цель изобретения - упрощение, что достигается путем введения в устройство группы из (mk+1) блоков преобразования, каждый из которых содержит регистр, делитель на два и коммутатор с соответствующими связями. 1 з.п. ф-лы, 3 ил.

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР по заявке N 4403204/24-24, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1988-12-21—Подача