о о го о о N

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные,

Целью изобретения является повышение быстродействия.

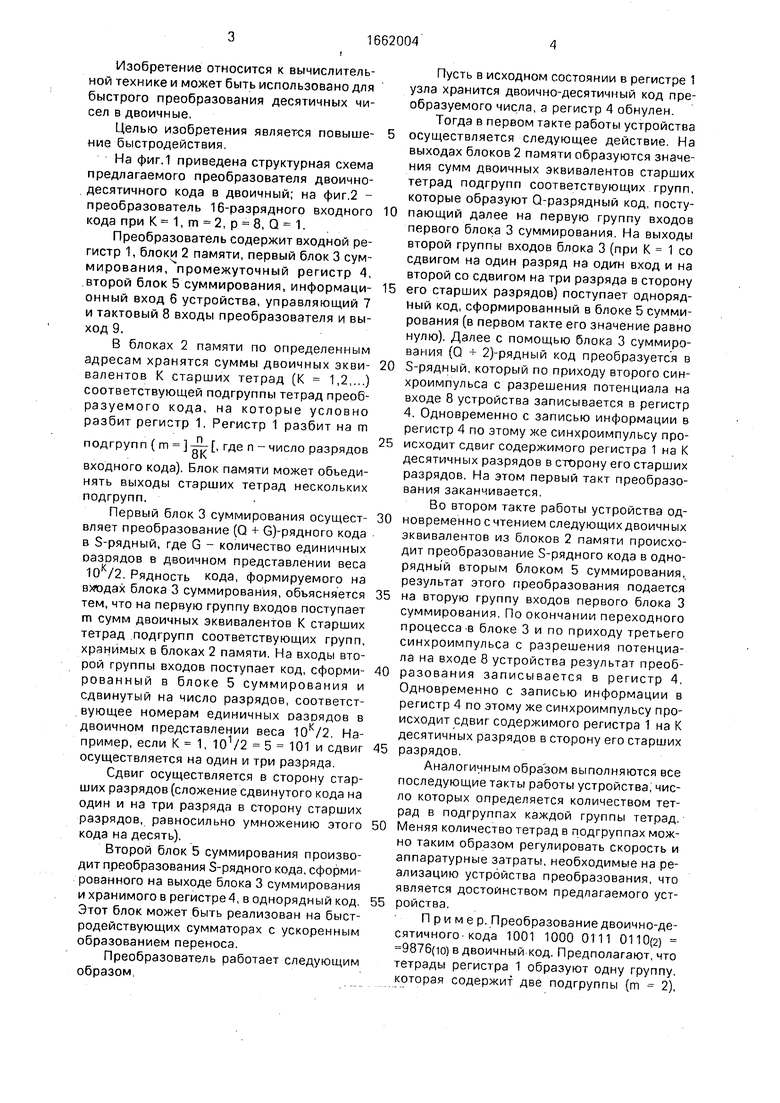

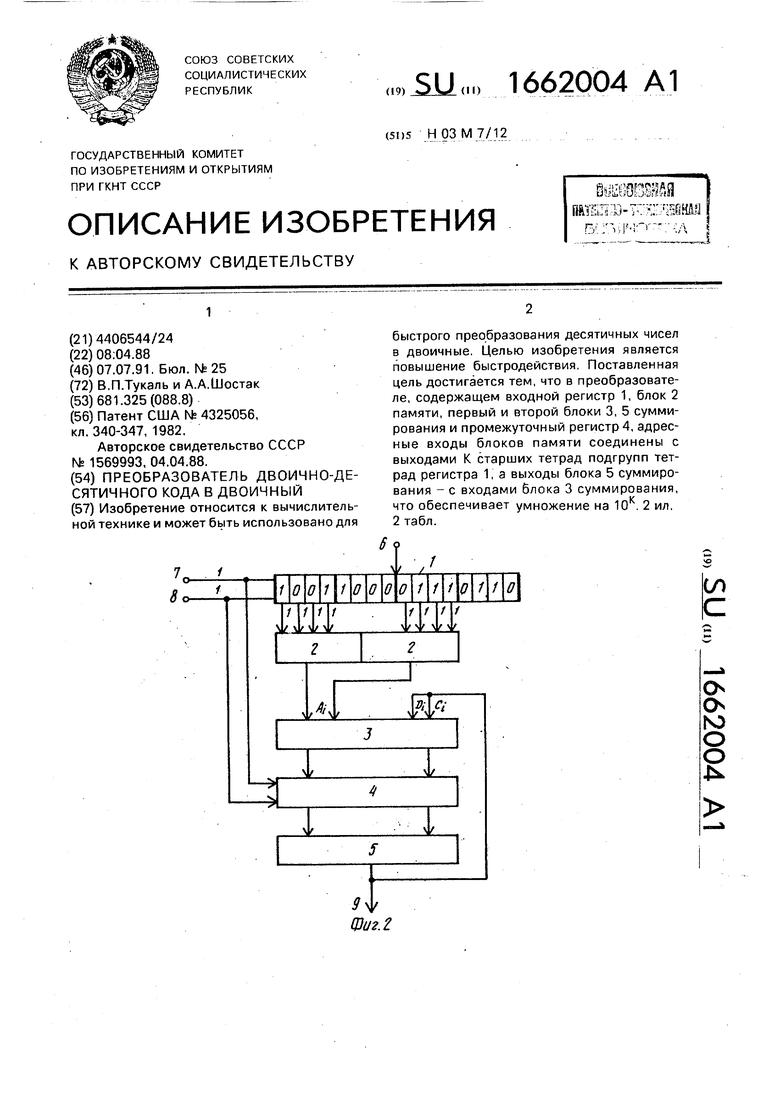

На фиг.1 приведена структурная схема предлагаемого преобразователя двоично- десятичного кода в двоичный; на фиг.2 - преобразователь 16-разрядного входного кода при ,т 2, р 8, 0 1.

Преобразователь содержит входной регистр 1, блоки 2 памяти, первый блок 3 суммирования, промежуточный регистр А, второй блок 5 суммирования, информационный вход б устройства, управляющий 7 и тактовый 8 входы преобразователя и выход 9.

В блоках 2 памяти по определенным адресам хранятся суммы двоичных эквивалентов К старших тетрад (К 1,2,...) соответствующей подгруппы тетрад преобразуемого кода, на которые условно разбит регистр 1. Регистр 1 разбит на m

подгрупп ( m , где п -число разрядов 8К

входного кода). Блок памяти может объединять выходы старших тетрад нескольких подгрупп.

Первый блок 3 суммирования осуществляет преобразование (Q + С)-рядного кода в S-рядный, где G - количество единичных оазоядов в двоичном представлении веса 10к/2. Рядность кода, формируемого на входах блока 3 суммирования, обьясняется тем, что на первую группу входов поступает m сумм двоичных эквивалентов К старших тетрад подгрупп соответствующих групп, хранимых в блоках 2 памяти. На входы второй группы входов поступает код, сформированный в блоке 5 суммирования и сдвинутый на число разрядов, соответствующее номерам единичных оазрядое в двоичном представлении веса 10к/2. Например, если К 1, 101/2 5 101 и сдвиг осуществляется на один и три разряда.

Сдвиг осуществляется в сторону старших разрядов (сложение сдвинутого кода на один и на три разряда в сторону старших разрядов, равносильно умножению этого кода на десять).

Второй блок 5 суммирования производит преобразования S-рядного кода, сформированного на выходе блока 3 суммирования ихранимого в регистре4, в однорядный код. Этот блок может быть реализован на быстродействующих сумматорах с ускоренным образованием переноса.

Преобразователь работает следующим образом

Пусть в исходном состоянии в регистре 1 узла хранится двоично-десятичный код преобразуемого числа, а регистр 4 обнулен. Тогда в первом такте работы устройства

осуществляется следующее действие. На выходах блоков 2 памяти образуются значения сумм двоичных эквивалентов старших тетрад подгрупп соответствующих групп, которые образуют Q-разрядный код, посту0 пающий далее на первую группу входов первого блока 3 суммирования. На выходы второй группы входов блока 3 (при К 1 со сдвигом на один разряд на один вход и на второй со сдвигом на три разряда в сторону

5 его старших разрядов) поступает однорядный код, сформированный в блоке 5 суммирования (в первом такте его значение равно нулю). Далее с помощью блока 3 суммирования (Q + 2)-рядный код преобразуется в

0 S-рядный, который по приходу второго синхроимпульса с разрешения потенциала на входе 8 устройства записывается в регистр 4. Одновременно с записью информации в регистр 4 по этому же синхроимпульсу про5 исходит сдвиг содержимого регистра 1 на К десятичных разрядов в сторону его старших разрядов. На этом первый такт преобразования заканчивается.

Во втором такте работы устройства од0 новременно с чтением следующих двоичных эквивалентов из блоков 2 памяти происходит преобразование S-рядного кода в однорядный вторым блоком 5 суммирования, результат этого преобразования подается

5 на вторую группу входов первого блока 3 суммирования. По окончании переходного процесса в блоке 3 и по приходу третьего синхроимпульса с разрешения потенциала на входе 8 устройства результат преоб0 разования записывается в регистр 4. Одновременно с записью информации в регистр 4 по этому же синхроимпульсу происходит сдвиг содержимого регистра 1 на К десятичных разрядов в сторону его старших

5 разрядов.

Аналогичным образом выполняются все последующие такты работы устройства, число которых определяется количеством тетрад в подгруппах каждой группы тетрад.

0 Меняя количество тетрад в подгруппах можно таким образом регулировать скорость и аппаратурные затраты, необходимые на реализацию устройства преобразования, что является достоинством предлагаемого уст5 ройства.

Пример. Преобразование двоично-десятичного кода 1001 1000 0111 0110(2) 9876(ю) в двоичный код. Предполагают, что тетрады регистра 1 образуют одну группу, которая содержит две подгруппы (т 2),

каждая из которых содержит по две тетрады. Результат на выходе первого блока 3 суммирования формируется в 2-рядном коде (S 2),

Структурная схема такого устройства приведена на фиг.2. В регистре 1 преобразуемого кода указано значение исходного кода. Группа блоков 2 памяти в данном случае может быть объединена в один блок памяти с одной группой выходов. Пример приведен для такой реализации.

Значение разрядов, подаваемых в 1-м такте на адресные входы блока 2 памяти, приведено в табл.1.

Процесс преобразования в устройстве двоично-десятичного кода 1001 1000 0111 0110 в двоичный код приведен в табл.2.

Формула изобретения Преобразователь двоично-десятичного кода в двоичный, содержащий входной регистр, состоящий из тетрад, объединенных

в m подгрупп (m - , где п - разрядность оК

входного кода, а К - целое число); группу из Q 4 mK/p блоков памяти, где р - число

адресных входов блока памяти первый и второй блоки суммирования и промежуточный регистр информационные входы которого соединены с выходами первого блока суммирования, первая группа входов которого соединена с выходами соответствующих блоков памяти группы, выходы второго блока суммирования являются выходами преобразователя, информационные входы которого соединены с информационными входами входного регистра, вход записи которого соединен с управляющим входом преобразователя и входом сброса промежуточного регистра, вход записи которого соединен с тактовым входом преобразователя и входом сдвига входного регистра, отличающийся тем, что с целью повышения быстродействия, в нем адресные входы блока памяти группы соединены с выходами К старших тетрад соответствующих подгрупп входного регистра, выходы второго блока суммирования соединены с вторыми входами первого блока суммирования со сдвигом на R разрядов в сторону старших разрядов, где R - номера единичных разрядов в двоичном представлении веса 10к/2

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1658387A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1649672A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования десятичных чисел в двоичные. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в преобразователе, содержащем входной регистр 1, блоки 2 памяти, первый и второй блоки 3, 5 суммирования и промежуточный регистр 4, адресные входы блоков памяти соединены с выходами K старших тетрад подгрупп тетрад регистра 1, а выходы блока 5 суммирования соединены с входами блока 3 суммирования, что обеспечивает умножение на 10K. 2 ил. 2 табл.

Таблица 2

i9

Фиг.1

О

I

| Патент США № 4325056, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

Авторы

Даты

1991-07-07—Публикация

1988-04-08—Подача