5.1 USSSli

i (Л

Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных машин.

Цель изобретения - расширение фунциональных возможностей за счет увеличения количества типов формируе-. мой маски.

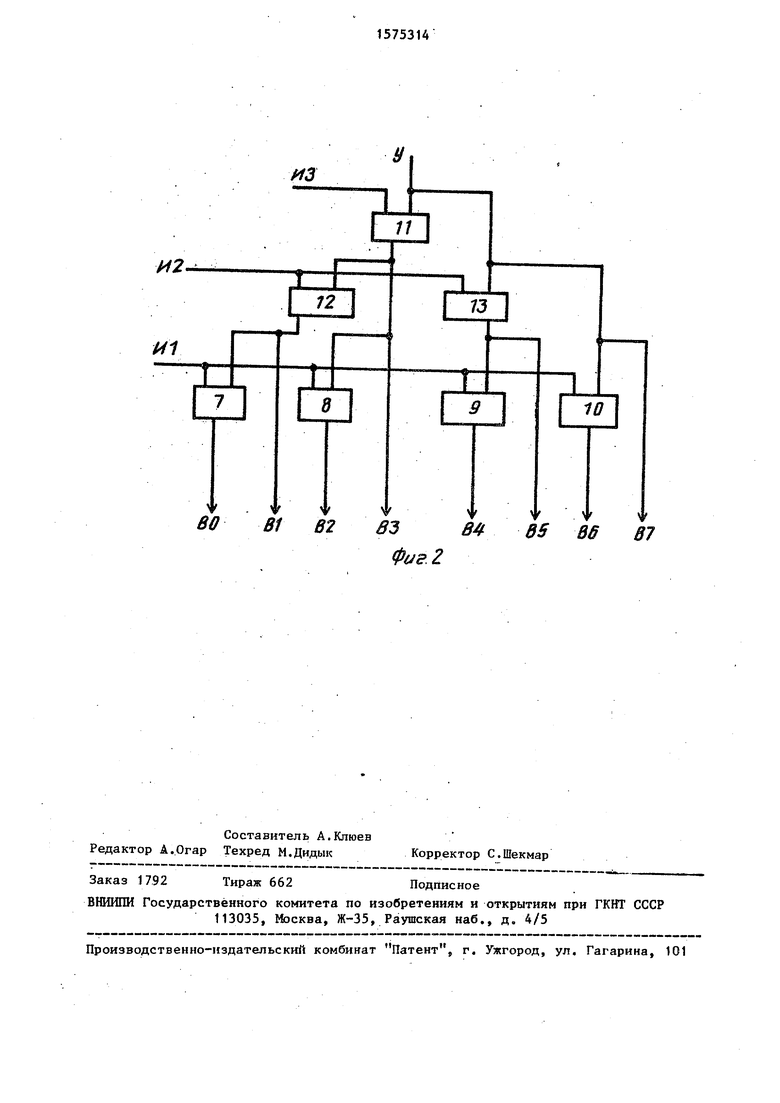

На фиг.1 представлена схема устройства для формирования маски, на фиг.2 - схема преобразователя двоичного кода в единичный код.

Устройство (фиг.1) содержит пре-- образователь 1,двоичного кода в единичный код, первую группу преобразователей 2.1-2.8 двоичного кода в единичный код, вторую группу преобразователей 3.1 - 3,64 двоичного кода в единичный код, третью группу преобразователей 4.1-4.512 двоичного кода в единичный Код,, группу информационных входов 5.1-5.4 устройства и группу выходов 6 устройства.

Преобразователь 1 (2-4) двоичного кода в единичный код (фиг. 2) содержит с первого по седьмой элементы И 7-13.

Устройство для формирования маски (фиг.1) работает следующим образом.

На каждый.из входов 5.1-5.4 поступают соответствующие три разряда инверсного двенадцатиразрядного кода, задающего тип и значение формируемой маски. С входов 5.1-5.4 эти значения поступают на информационные входы соответственно преобразо-- вателя 1, преобразователей 2.1-2.8 группы, преобразователей 3.1-3.64 группы и преобразователей 4.1-4.512 группы. С выходов преобразователей 4.1-4.512 группы 4096-разрядная йас- ка поступает на группу выходов 6 устройства.Преобразователи (фиг.2) формируют на выходах разрядов ВО-В7 выхода в зависимости от значений на входе Y, разрешения и входах разрядов И1, И2, ИЗ информационного входа следующие значения4;.

ВО Y ИЗ И2 ИЬ В4 Y И2 И1 В1 Y ИЗ И2 В5 Y И2

82 Y ИЗ И1 В6 Y И1

83 Y ИЗ В7 Y Изобретение обеспечивает также

сокращение аппаратурных затрат по сравнению с известным устройством.

0

5

0

5

0

5

0

5

Формула изобретения

1. Устройство для формирования маски, содержащее преобразователь двоичного кода в единичный код, с первого по четвертый преобразователи двоичного кода в единичный код первой группы, с первого по шестнадцатый преобразователи двоичного , кода в единичный код второй группы, с первого, по шестьдесят четвертый преобразователи двоичного кода в единичный код третьей группы, причем с первого по четвертый информационные входы группы устройства соединены соответственно с информационными входами преобразователя двоичного кода в единичный код, с первого по четвертый преобразователей дврич- ного кода в единичный код первой группы, с первого по шестнадцатый преобразователей двоичного кода в единичный код второй группы, с первого по шестьдесят четвертый преобразователей двоичного кода в единичный код третьей группы, -выходы разрядов с первого по шестьдесят четвертый преобразователей двоичного кода в единичный код третьей группы являются соответственно с первого по пятьсот двенадцатый выходами группы устройства, выходы с первого по четвертый разрядов выхода преобразователя двоичного кода в единичный код соединены с входами разрешения соответствующих преобразователей двоичного кеда в единичный код первой группы, выход К-го (К 1-4) разряда выхода первого преобразователя двоичного кода в единичный код р-й группы (,2) соединен с входом разрешения К-го преобразователя двоичного кода в единичный код (р+1)-й группы, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения количества типов формируемой маски, оно содержит с пятого по восьмой преобразователи двоичного кода в единичный код первой группы, с семнадцатого по шестьдесят четвертый преобразователи двоичного кода в единичный код второй группы, с шестьдесят пятого по пятьсот двенадцатый преобразователи двоичного кода в единичный код третьей группы, причем вход логической единицы устройства соединен с входом разрешения преобразователя двоичного

51575314

кода в единичный код, выходы с пятот

го по восьмой разрядов выхода которого соединены с входами разрешения со- ответсгвующих преобразователей двоичного кода в единичный код первой группы, информационные входы котррых соединены с вторым информационным входом группы устройства, третий и четвертый информационные входы группы которого соединены с информационными входами соответственно с семнадцатого по шестьдесят четвертый преобразователей двоичного кода в единичный код второй группы и с шестьдесят пятого по пятьсот двенадцатый преобразователей двоичного кода в единичный код третьей группы, выходы разрядов которых являются соответственно с пятьсот тринадцатого по четыре тысячи девяносто шестой выходами группы устройства, выход (К+4)-го разряда выхода первого преобразователя двоичного кода в единичный код р-й группы соединен с входом разре- шения (К+4)-го преобразователя двоичного кода в единичный код (р+1)-й группы, выход n-го разряда выхода (п 1-8) i-го (i 2-8) преобразователя двоичного кода в единичный код р-й группы соединен с входом разрешения (8(i-1)+n)-ro преобразователя двоичного кода в единичный код (р-Н)-й группы.

5 0

5

0

2. Устройство по п. 1, о т л и - чающееся тем, преобразователь двоичного кода в единичный код содержит с первого по седьмой элементы И. причем вход первого разряда информационного входа преобразователя двоичного кода в единичный код соединен с первыми входами с первого по четвертый элементов И, вторые входы которых соединены соответственно с выходами шестого, пятого и седьмого элементов И и с входом разрешения преобразователя двоичного кода в единичный код, вход второго разряда информационного входа кото- рого соединен с первыми входами шестого и седьмого элементов И, вторые входы которых соединены соответственно с выходом пятого элемента И и с первым входом пятого элемента И второй вход которого соединен с входом третьего разряда информационного входа преобразователя двоичного кода в единичный код, вход разрешения которого соединен с первым входом пятого элемента И, выходы первого, шестого, второго, пятого, третьего, седьмого, четвертого элементов И и второй вход четвертого элемента И являются выходами разрядов выхода преобразователя двоичного кода в единичный код.

ВО 81 62 8384 BS В6 В7

Фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для уплотнения @ -разрядного двоичного кода | 1982 |

|

SU1048471A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Преобразователь кода азимута | 1990 |

|

SU1755276A1 |

| Устройство для уплотнения информации | 1984 |

|

SU1211716A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Устройство для деления | 1988 |

|

SU1635183A1 |

| Преобразователь относительного нулевого кода в двоичный | 1987 |

|

SU1478336A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для сортировки массивов чисел | 1988 |

|

SU1624440A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения процессора. Изобретение по сравнению с известными устройствами расширяет функциональные возможности за счет увеличения количества типов формируемой маски. Устройство содержит преобразователь 1 двоичного кода в единичный код, первую группу преобразователей 2.1-2.8 двоичного кода в единичный код, вторую группу преобразователей 3.1-3.64 двоичного кода в единичный код и третью группу преобразователей 4.1-4.512 двоичного кода в единичный код с соответствующими связями. 1 з.п. ф-лы, 2 ил.

| Устройство для многоуровневой коммутации процессоров и блоков памяти | 1983 |

|

SU1213474A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования кода маски | 1984 |

|

SU1262573A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-06-30—Публикация

1988-04-27—Подача