Изобретение относится к вычислительной технике и предназначено для использования в специализированных вычислительных устройствах.

Цель изобретения - повышение достоверности работы устройства.

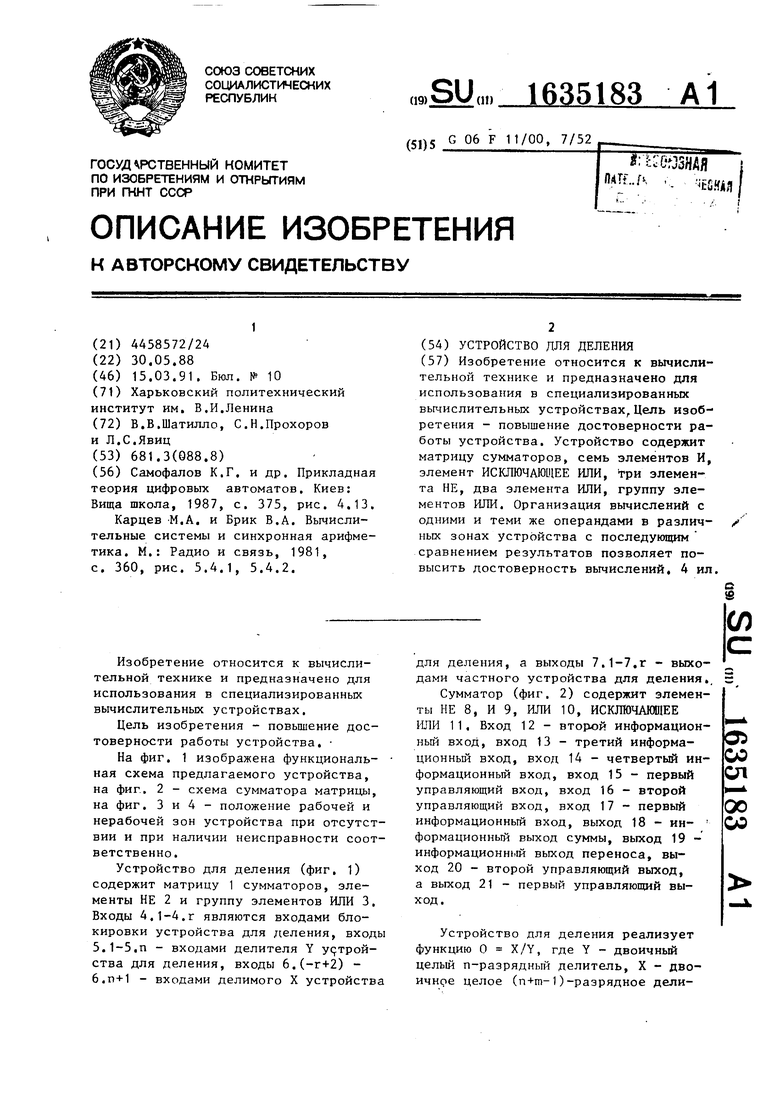

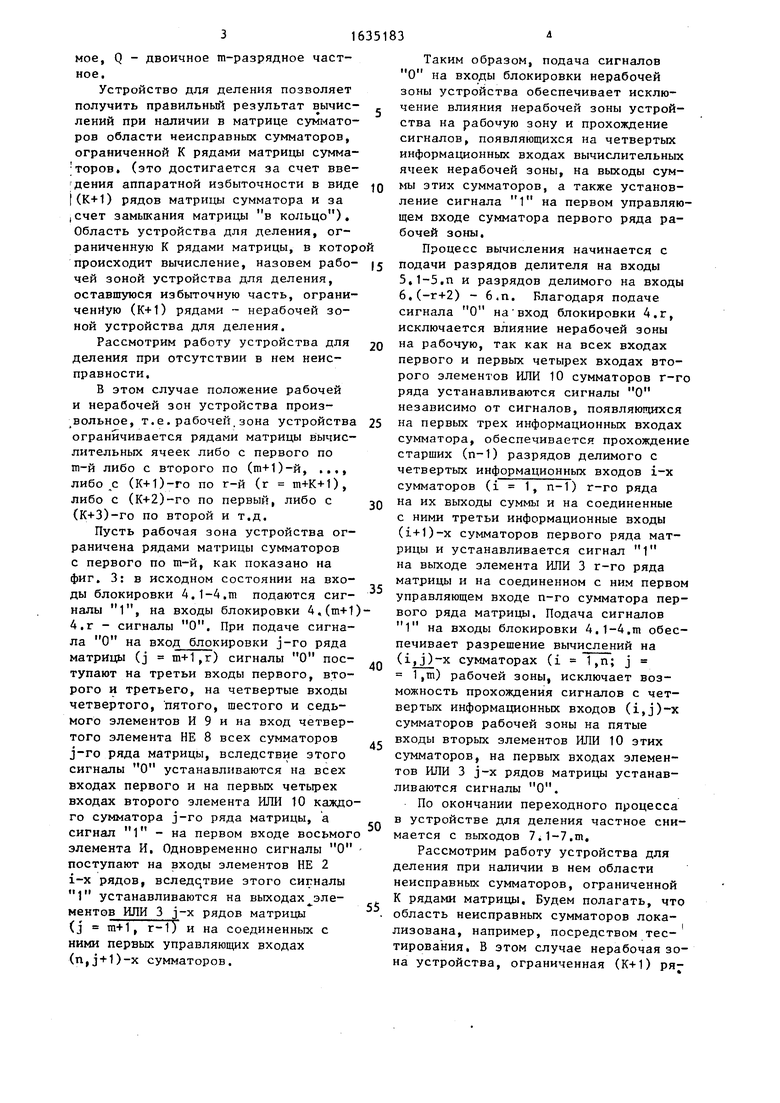

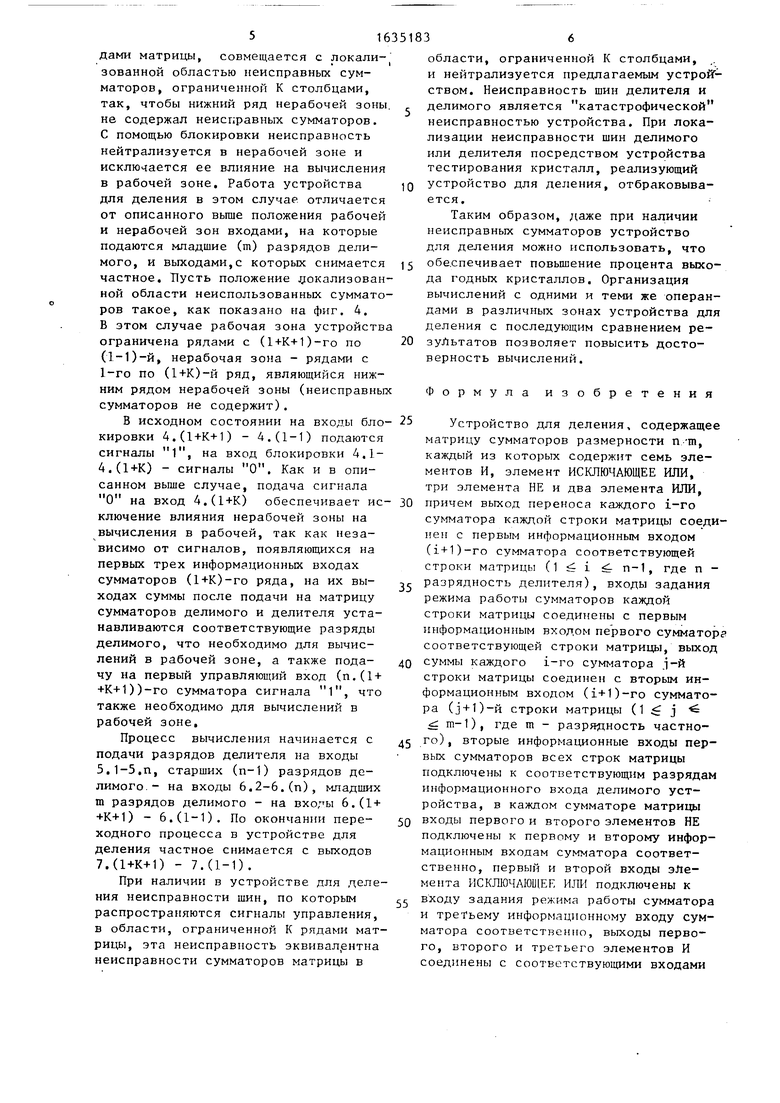

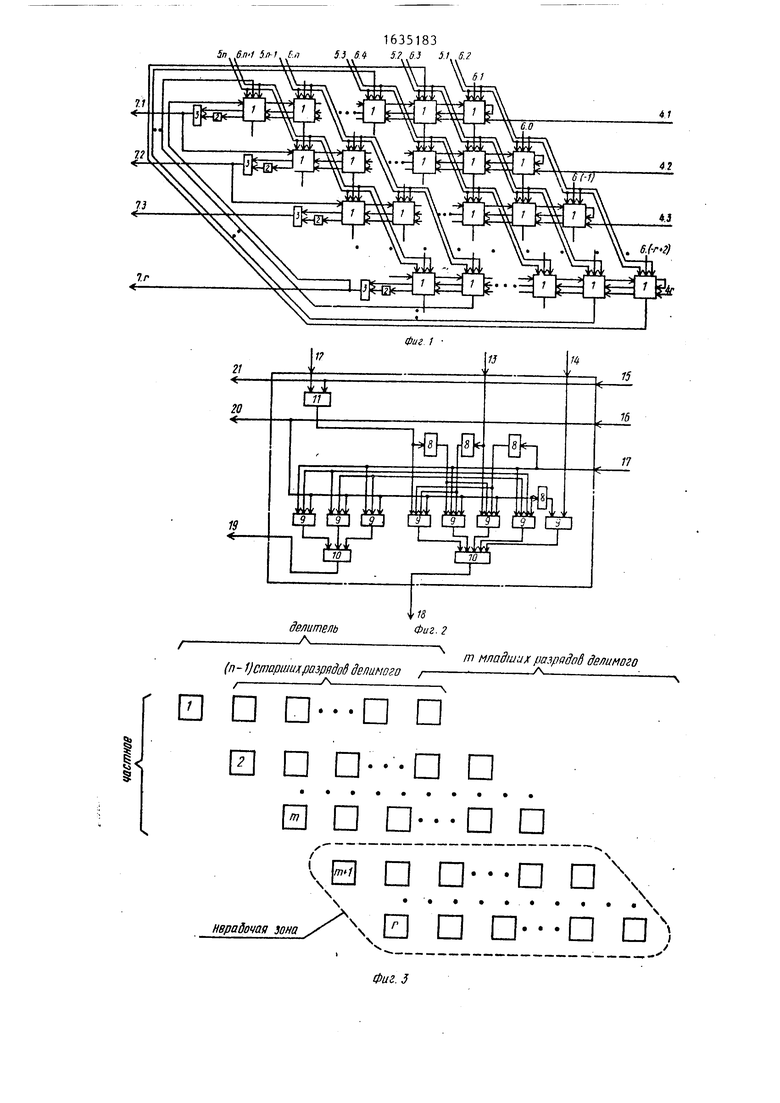

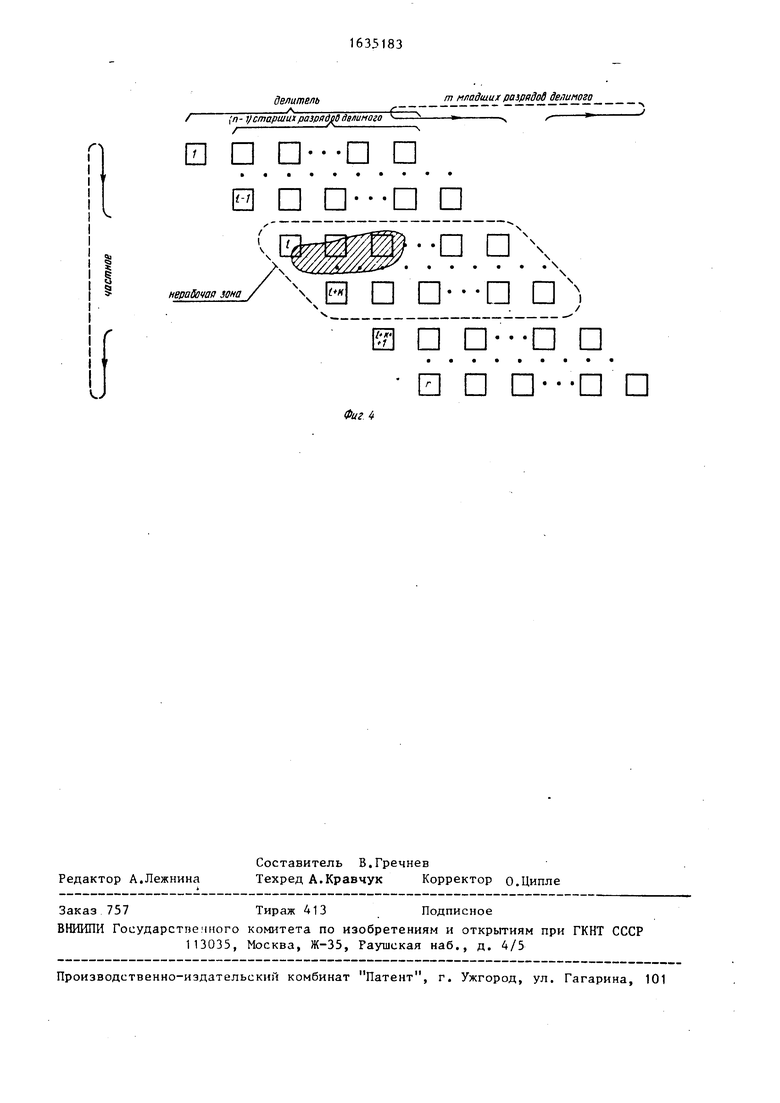

На фиг. 1 изображена функциональная схема предлагаемого устройства, на фиг. 2 - схема сумматора матрицы, на фиг. 3 и 4 - положение рабочей и нерабочей зон устройства при отсутствии и при наличии неисправности соответственно.

Устройство для деления (фиг. 1) содержит матрицу 1 сумматоров, элементы НЕ 2 и группу элементов ИЛИ 3. Входы 4.1-4.г являются входами блокировки устройства для деления, входы 5.1-5.П - входами делителя Y устройства для деления, входы 6.(-г+2) - б.п+1 - входами делимого X устройства

для деления, а выходы 7.1-7.г - выходами частного устройства для деления.. Сумматор (фиг. 2) содержит элементы НЕ 8, И 9, ИЛИ 10, ИСКЛЮЧАЮШЕЕ ИЛИ 11, Вход 12 - второй информационный вход, вход 13 - третий информационный вход, вход 14 - четвертый информационный вход, вход 15 - первый управляющий вход, вход 16 - второй управляющий вход, вход 17 - первый информационный вход, выход 18 - ин- формационный выход суммы, выход 19 - информационный выход переноса, выход 20 - второй управляющий выход, а выход 21 - первый управляющий выход.

Устройство для деления реализует функцию 0 X/Y, где Y - двоичный целый n-разрядный делитель, X - двоичное целое (n+m-1)-разрядное делиосо

ел

00

оо

мое, Q - двоичное m-разрядное частное.

Устройство для деления позволяет получить правильный результат вычис- лений при наличии в матрице сумматоров области неисправных сумматоров, ограниченной К рядами матрицы сумма- торов, (это достигается за счет введения аппаратной избыточности в виде j(K-H) рядов матрицы сумматора и за (счет замыкания матрицы в кольцо). Область устройства для деления, ограниченную К рядами матрицы, в котор происходит вычисление, назовем рабо- чей зоной устройства для деления, оставшуюся избыточную часть, ограниченную (К+1) рядами - нерабочей зоной устройства для деления.

Рассмотрим работу устройства для деления при отсутствии в нем неисправности.

В этом случае положение рабочей и нерабочей зон устройства произвольное, т.е. рабочей.зона устройства ограничивается рядами матрицы вычислительных ячеек либо с первого по m-й либо с второго по (т+1)-й, ..., либо с (К+1)-го по r-й (г т+К+1),

ЛИбО С (К+2)-ГО ПО ПерВЫЙ, ЛИбо С

(К+3)-го по второй и т.д.

Пусть рабочая зона устройства ограничена рядами матрицы сумматоров с первого по m-й, как показано на фиг. 3: в исходном состоянии на входы блокировки 4.1-4.т подаются сиг

налы 1, на входы блокировки 4,(т+1 4.г - сигналы О. При подаче сигнала О на вход блокировки j-ro ряда

матрицы (j m+1,r) сигналы О поступают на третьи входы первого, второго и третьего, на четвертые входы четвертого, пятого, шестого и седьмого элементов И 9 и на вход четвертого элемента НЕ 8 всех сумматоров j-ro ряда матрицы, вследствие этого сигналы О устанавливаются на всех входах первого и на первых четырех входах второго элемента ИЛИ 10 каждого сумматора j-ro ряда матрицы, а сигнал 1 - на первом входе восьмог элемента И, Одновременно сигналы О поступают на входы элементов НЕ 2 1-х рядов, вследствие этого сигналы 1 устанавливаются на выходах эле- ментов ИЛИ 3 j-x рядов матрицы (j m+1, г-1) и на соединенных с ними первых управляющих входах (n,j+1)-x сумматоров.

5 Q 5

0

5

Q

5

0

45

0

5

Таким образом, подача сигналов О на входы блокировки нерабочей зоны устройства обеспечивает исключение влияния нерабочей зоны устройства на рабочую зону и прохождение сигналов, появляющихся на четвертых информационных входах вычислительных ячеек нерабочей зоны, на выходы суммы этих сумматоров, а также установление сигнала 1 на первом управляющем входе сумматора первого ряда рабочей зоны.

Процесс вычисления начинается с подачи разрядов делителя на входы 5.1-5.П и разрядов делимого на входы 6,(-г+2) - 6,п. Благодаря подаче сигнала О на вход блокировки 4. г, исключается влияние нерабочей зоны на рабочую, так как на всех входах первого и первых четырех входах второго элементов ИЛИ 10 сумматоров г-го ряда устанавливаются сигналы О независимо от сигналов, появляющихся на первых трех информационных входах сумматора, обеспечивается прохождение старших (п-1) разрядов делимого с четвертых информационных входов 1-х сумматоров (i 1, п-1) r-го ряда на их выходы суммы и на соединенные с ними третьи информационные входы (i+1)-x сумматоров первого ряда матрицы и устанавливается сигнал 1 на выходе элемента ИЛИ 3 r-го ряда матрицы и на соединенном с ним первом управляющем входе n-го сумматора первого ряда матрицы. Подача сигналов 1 на входы блокировки 4.1-4.т обеспечивает разрешение вычислений на (i, сумматорах (i 1,n; j 1,m) рабочей зоны, исключает возможность прохождения сигналов с четвертых информационных входов (i,j)-x сумматоров рабочей зоны на пятые входы вторых элементов ИЛИ 10 этих сумматоров, на первых входах элементов ИЛИ 3 j-x рядов матрицы устанавливаются сигналы О.

По окончании переходного процесса в устройстве для деления частное снимается с выходов 7.1-7.т.

Рассмотрим работу устройства для деления при наличии в нем области неисправных сумматоров, ограниченной К рядами матрицы. Будем полагать, что область неисправных сумматоров локализована, например, посредством тес- тирования, В этом случае нерабочая зона устройства, ограниченная (К+1) рядами матрицы, совмещается с локализованной областью неисправных сумматоров, ограниченной К столбцами, так, чтобы нижний ряд нерабочей зоны не содержал неисправных сумматоров. С помощью блокировки неисправность нейтрализуется в нерабочей зоне и исключается ее влияние на вычисления в рабочей зоне. Работа устройства для деления в этом случае отличается от описанного выше положения рабочей и нерабочей зон входами, на которые подаются младшие (т) разрядов делимого, и выходами,с которых снимается

частное. Пусть положение локализованной области неиспользованных сумматоров такое, как показано на фиг. 4. В этом случае рабочая зона устройства ограничена рядами с (1+К+1)-го по (1-1)-й, нерабочая зона - рядами с 1-го по (1+К)-й ряд, являющийся нижним рядом нерабочей зоны (неисправных сумматоров не содержит).

В исходном состоянии на входы бло- кировки 4.(1+К+1) - 4.(1-1) подаются сигналы 1, на вход блокировки 4.1- 4.(1+К) - сигналы 0м. Как и в описанном выше случае, подача сигнала

О на вход 4.(1+К) обеспечивает ис- 30 причем выход переноса каждого 1-го

15

10

20

51836

области, ограниченной К столбцами, . и нейтрализуется предлагаемым устройством. Неисправность шин делителя и делимого является катастрофической неисправностью устройства. При локализации неисправности шин делимого или делителя посредством устройства тестирования кристалл, реализующий устройство для деления, отбраковывается.

Таким образом, даже при наличии неисправных сумматоров устройство для деления можно использовать, что обеспечивает повышение процента выхода годных кристаллов. Организация вычислений с одними и теми же операндами в различных зонах устройства для деления с последующим сравнением результатов позволяет повысить достоверность вычислений.

Формула изобретения

Устройство для деления, содержащее матрицу сумматоров размерности n -m, каждый из которых содержит семь элементов И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента НЕ и два элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

| Устройство для деления | 1984 |

|

SU1257637A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Устройство для деления | 1989 |

|

SU1667057A1 |

| СПОСОБ ДЕЛЕНИЯ ЦЕЛЫХ ДВОИЧНЫХ ЧИСЕЛ БЕЗ ОСТАТКА НАЧИНАЯ С МЛАДШИХ РАЗРЯДОВ | 2012 |

|

RU2498393C1 |

| Однородная вычислительная структура для @ разложения матриц | 1984 |

|

SU1249531A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

Изобретение относится к вычислительной технике и предназначено для использования в специализированных вычислительных устройствах,. Цель изобретения - повышение достоверности работы устройства. Устройство содержит матрицу сумматоров, семь элементов И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента НЕ, два элемента ИЛИ, группу элементов ИЛИ. Организация вычислений с одними и теми же операндами в различных зонах устройства с последующим сравнением результатов позволяет повысить достоверность вычислений, 4 ил.

ключение влияния нерабочей зоны на вычисления в рабочей, так как независимо от сигналов, появляющихся на первых трех информационных входах сумматоров (1+К)-го ряда, на их выходах суммы после подачи на матрицу сумматоров делимого и делителя устанавливаются соответствующие разряды делимого, что необходимо для вычислений в рабочей зоне, а также подачу на первый управляющий вход (п.(1+ +К+1))-го сумматора сигнала 1, что также необходимо для вычислений в рабочей зоне.

Процесс вычисления начинается с подачи разрядов делителя на входы 5.1-З.п, старших (п-1) разрядов делимого - на входы 6.2-6.(п), младших m разрядов делимого - на вхо,пы 6.(1 + +К+1) - 6.(1-1). По окончании переходного процесса в устройстве для деления частное снимается с выходов 7.Ц+К+1) - 7.(1-1).

При наличии в устройстве для деления неисправности шин, по которым распространяются сигналы управления, в области, ограниченной К рядами матрицы, эта неисправность эквивалентна неисправности сумматоров матрицы в

сумматора каждой строки матрицы соединен с первым информационным входом (i+1)-ro сумматора соответствующей строки матрицы ( п-1, где n разрядность делителя), входы задания режима работы сумматоров каждой строки матрицы соединены с первым информационным входом первого сумматора соответствующей строки матрицы, выход

суммы каждого 1-го сумматора строки матрицы соединен с вторым информационным входом (1+1)-го сумматора (j + O-й строки матрицы (1 j т-1), где т - разрядность частного), вторые информационные входы первых сумматоров всех строк матрицы подключены к соответствующим разрядам информационного входа делимого устройства, в каждом сумматоре матрицы

входы первого и второго элементов НЕ подключены к первому и второму информационным входам сумматора соответственно, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к

входу задания режима работы сумматора и третьему информационному входу сумматора соответственно, выходы первого, второго и третьего элементов И соединены с соответствующими входами

первого элемента ИЛИ, выходы четвертого, пятого, шестого и седьмого элементов И соединены с соответствующими входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ подключены к выходам переноса и суммы сумматора соответственно, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом третьего элемента НЕ и первыми входами первого и второго элементов И, второй вход первого элемента И и первый вход третьего элемента И подключены к первому информационному входу сумматора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом четвертого элемента И, выход третьего элемента НЕ соединен с первыми входами пятого и шестого элементов И,вторые входы второго,тре тьего и шестого элементов И и первый вход седьмого элемента И подключены к второму формационному входу сумматора, выход второго элемента НЕ соединен с втрым входом четвертого элемента И и вторым входом пятого элемента И, выход первого элемента НЕ соединен с третьими входами четвертого и шестого элементов И, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входо седьмого элемента И, третьи входы пятого и седьмого элементов И подключены к второму информационному входу сумматора, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены К+1 строк сумматоров (1 К п),группа элементов ИЛИ, в каждый сумматор матрицы введены четвертый элемент НЕ и восьмой эле- мент И, причем выходы переноса 1-го сумматора каждой t-й строки матрицы соединены с первыми информационными входами (i+O-ro сумматора t-й строки матрицы (m+1 t т + К+1), входы задания режима работы всех сумматоров каждой t-й строки матрицы соединены с первым информационным входом первого сумматора t-й строки матрицы, выход суммы каждого 1-го сумматора 1-й строки матрицы соединен с вторым информационным входом (i+1)-ro сумматора (1+1)-й строки

матрицы (m+1 1 m+К), вторые информационные входы первых сумматоров каждой t-й строки матрицы подключены к соответствующим разрядам входа делимого устройства, выходы суммы каждого 1-го сумматора последней строки матрицы соединены с вторыми информационными входами (i+1)-ro сумматора первой строки матрицы, выход переноса последнего сумматора каждой строки матрицы соединен с первым входом соответствующего элемента ИЛИ группы, выход которого подключен к соответствующему разряду выхода частного устройства, выход каждого р-го элемента ИЛИ группы (1 - р - Ј m+К) соединен с входом задания режима работы последнего сумматора (р+1)-й строки матрицы, выход (т+К+ +1)-го элемента ИЛИ группы соединен с входом задания режима работы последнего сумматора первой строки матрицы, входы блокировки сумматоров каждой строки матрицы и вход соответствующего элемента НЕ группы подключены к соответствующему разряду входа блокировки устройства, выходы элементов НЕ группы соединены с вторыми входами соответствующих элементов ИЛИ группы, третьи информационные входы сумматоров каждого столбца матрицы объединены и подключены к соответствующим разрядам входа делителя устройства, четвертые информационные входы сумматоров каждого столбца матрицы объединены и подключены к соответствующим разрядам входа делимого устройства, в каждом суммато- ре матрицы выход четвертого элемента НЕ соединен с первым входом восьмого элемента И, выход которого соединен с соответствующим входом второго элемента ИЛИ, вход четвертого элемента НЕ и второй вход восьмого элемента И подключены соответственно к входу блокировки и четвертому информационному входу устройств а, третьи входы первого, второго и треть его элементов И и четвертые входы четвертого, пятого, шестого и седьмого элементов И подключены к входу задания режима работы сумматора.

1635183 5п 6п-1 5Я-1 toS3 64 5 63

i. y i i i . - Vl.. . ..--

делитель

/V

(n-1) старших разрядов Земного л

п

1

т

D

нерабочая зона

(

i

4Г

/т младших разрядаб делимого

П---П П

т клавших разрадод делимого

н п п---п п ш п D---D п

| Самофалов К.Г | |||

| и др | |||

| Прикладная теория цифровых автоматов | |||

| Киев: Вища школа, 1987, с | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Карцев -М.А | |||

| и Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-03-15—Публикация

1988-05-30—Подача