с +

2 а dx j (х . + X ;, ) .+

+ b (3 X . ,

В первом шаге имеем Xg О, X , ЛХ, и у, с + b /Зх

Во втором шаге имеем

X.dX,, Х2

у с +.айх + ЬДх , + а лх

+ Л-к)+ ЛХ,) + Ъ и

Xfl

55

с + а СДх + 4 i j) + + b (Дх , + ЛХ,)

- --, Лх

1

40

Тогда имеем следующее.

В такте 4 на вход 13 поступает

/Зх, 1 и

45

SM4: а -н -|- Ь;

SM6: SM4 + RC5 -I, а +

+ -i-b

+ Ь;

SM9: SM6 + RG11

Ь) + с а (-1-) 4- ь-1- с .

По сигналу 21 RG5:

4- а

+ - Ъ, RG1 1 : - а + -|- b с .

В.такте 5 по сигналу 20 в регистрах 2 и 11 происходит сдвиг, RG2:

1

-2-, RG11: 2( а -н - b + с).

В такте 6 на вход 13 поступает ЛУ 1 и SM4: -- RG2 + RG5

. -I- а + - а - -|- Ь;

-2- (2- а - Ь) + с - а.(-1-) - b-I- ч- с.

По сигналу 21 RG11:

1 т- b + с, RG5:

1

--- а - 1

- -2- а + -5- Ъ.

В такте 5 - сдвиг, RG2: --- а, R(J11: 2(-|- а. - -1- b + с).

В такте 6ЛХ2 О, элемент И 15

по-прежнему открыт и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1986 |

|

SU1388848A1 |

| Устройство для цифровой двумерной свертки | 1986 |

|

SU1363250A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Цифровой генератор функций | 1989 |

|

SU1656511A1 |

| Цифровой фильтр | 1986 |

|

SU1354393A1 |

| Генератор случайного марковского процесса | 1985 |

|

SU1278842A1 |

| Интерполятор | 1986 |

|

SU1383396A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство для вычисления двумерной свертки | 1989 |

|

SU1619303A1 |

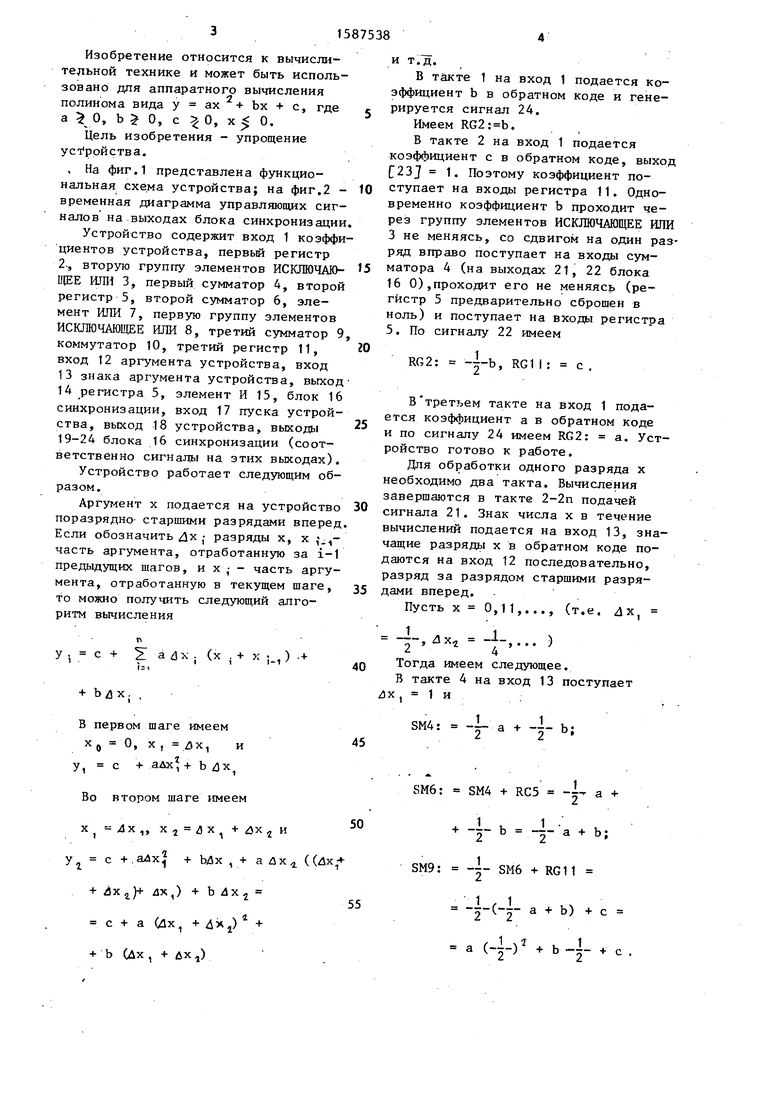

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых вычислительных машин. Целью изобретения является упрощение устройства. Эта цель достигается тем, что в устройство, содержащее три регистра 2, 5, 11, три сумматора 4, 6, 9, блок 16 синхронизации, коммутатор 10, введены две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 8, элемент ИЛИ 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент И 15. 2 ил.

SM6:

RG5 + SM4 -1- а.+ - Ъ +

-I- f а . -1- Ь .

((-Г -Ь- -Ь Ь; SM9: - SM6 + RG11 2( а(-1 +

. -1-) . Ь(-1- . -I-) .

с).

В такте 7 опять происходит сдвиг и т.д. Если некторьш разряд х равен нулю, то сигнал 21 через элемент И 15 не проходит и содержимое регистров 5, 11 не меняется.

Пусть ,00... (т.е. х - -0,11...), тогда в такте 4 на вход 13 поступает Лх, О, но sign х 1, поэтому Лх инвертируется в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и элемент И 15 открыт. Группа элементов ИСКЛЮЧАЮПЩЕ ИЛИ 3 инвертирует число, поступающее из RG2, т.е. меняет знак числа а на обратный. Аналогично меняет знак на обратный суммы из сумматора 6, группа элементов ИСКЛЮЧАКЯЦЕЕ ИЛИ 8. Поэтому имеем

SM4:

4 Т

SM6: SM4 + RG5 J а + - Ы

. --l-a..b;

SM9; - --- SM6 + RG11

SM4: - - RG2 + RG5

20

- - - -Г

25

SM6: RG5 + SM4 i- а + Ъ -тга. - -г- а + --- b -а ((--- +

30

-1-) -ь -1-) Ь;

SM9: - - SM6 + RG11 - а .ж

.((1-.-1-) .-1-).-1-Ь. + 2( а - -1- b Ч с) 2(a(-l-.-l-)-b(-i-.

+ ) с)

45 и- т.д.

По завершении вычислений 2п старших разрядов у считываются из ре гнет-- ра 11, п младших отбрасываются. В случае необходимости возможно сохра-i нение всех Зп разрядов, но разрядность блоков 2, 3, 4, 5, 6, 8, 9, 11 необходимо увеличить на п разрядов.

Устройство можно использовать для вычисления полиномов более высокого порядка. Пусть необходимо вычислить полином

50

у + +

+ а,

Преобразуем его к виду у ( + + а) х + а,х + а Вычисляем значение а.х а,х +

го

+ а., заносим его в регистр 2. В ре- регистры 5 и 11 заносим -х- а и а, ,210

и повторяем ,вычисления. На устройстве можно также выполнять операции сложения, умножения, возведения в квадрат. Формула изобретения

Устройство для вычисления полиномов, содержащее первый регистр, первьй сумматор, выход которого соединен с информационным входом второго регистра, выход которого соединен с первым входом первоцо сумматора, второй и третий сумматоры, первый информационный вход которого соединен с входом третьего резистора, коммутатор, блок синхронизации, первый выход которого соединен с

входами управления сдвигом первого

и третьего регистров, отличающееся тем, что, с целью упрощения устройства, в него введены дае группы элементов ИСКЛЮЧАКШЩЕ ИЛИ элемент. Н, элемент ИЛИ, элемент ИСКЛЮЧАЮГЩЕ ИЛИ, первый вход и выход которого соединен соответственно с входом аргумента устройства и первым входом элемента И, второй вход и выход которого соединены соответственно с вторым выходом блока синхронизации и первым входом элемента ИЛИ, второй вход которого соединен с третьим выходом блока синхронизации, а выход - с входами записи второго и третьего регистров, выход которого является выходом устройства, вход коэффициентов устройства соединен с информационным входом пер- вого регистра и первым информационQ ным входом коммутатора, выход, управляющий вход, второй информационный вход соединены соответств1енно с информационным входом третьего регистра, четвертым выходом блока син5 хронизации и выходом третьего сумматора, второй информационный вход которого соединен с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первые входы которых соединены с выходом второго сумматора, а вторые входы - с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы,, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом знака аргумента устройства, вторые входы и выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединены соответственно с выходом первого регистра и вторым информационным входом первого суммато- , ра, выход которого соединен с первым информационным входом второго сумматора, второй информационный вход которого соединен с выходом второго регистра, вход записи первого реги5 стра соединен с пятым выходом блока синхронизации, шестой выход и вход которого соединены соответственно с вьпсодом готовности данных и пуска устройства.

0

5

0

| Вычислительное устройство | 1981 |

|

SU1016779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор функций | 1973 |

|

SU519696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-06-02—Подача