1

г 9

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1571595A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство для отображения информации на матричном индикаторе | 1989 |

|

SU1783573A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобретения является повышение надежности работы за счет способности устройства блокировать возможное прерывание выборки блока памяти до завершения сеанса обмена с блоком памяти. Устройство содержит группу переключателей 1, регистр 2 адреса, дешифратор 3 адреса, матричный коммутатор 4, элемент ИЛИ-НЕ 7, группу D-триггеров 8. 1 ил.

(Л

с

,

6п

31

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти.

Целью изобретения является повьше- кие надежности работы за счет способности устройства блокировать возможное прерьшание выборки блока памяти . до завершения сеанса обмена с блоком памяти.

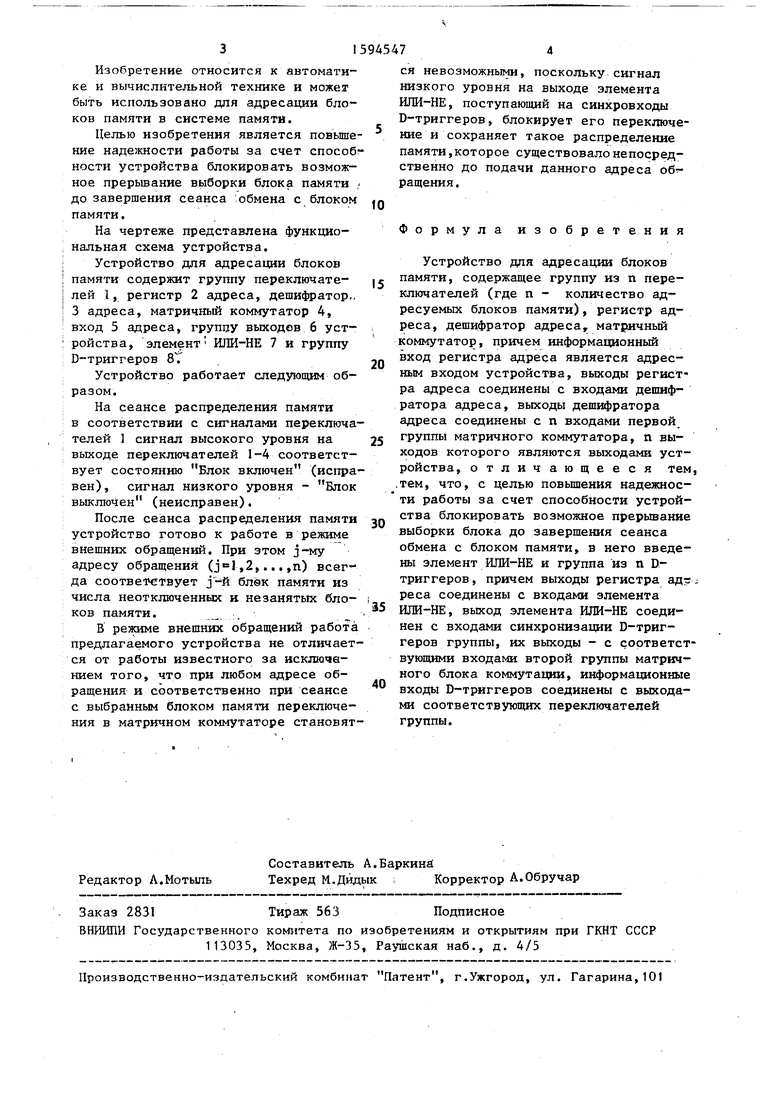

На чертеже представлена функциональная схема устройства.

Устройство для адресации блоков памяти содержит группу переключателей 1, регистр 2 адреса, дешифратор,, 3 адреса, матричный коммутатор 4, вход 5 адреса, групцу выходов 6 устройства, элемент ШШ-НЕ 7 и группу D-триггеров 8V

Устройство работает следующим образом.

На сеансе распределения памяти в соответствии с сигналами переклвтча- телей 1 сигнал высокого уровня на выходе переключателей 1-4 соответствует состоянию Блок включен (исправен) , сигнал низкого уровня - Блок выключен (неисправен).

После сеанса распределения памяти устройство готово к работе в режиме внешних обращений. При этом j-му адресу обращения ( ,2,... ,п) да соотве1Чгтвует j-й блек памяти из числа неотключенных и незанятых блоков памяти.

В режиме внешних обращений работа предлагаемого устройства не отличается от работы известного за исключб - нием того, что при любом адресе обращения и соответственно при сеансе с выбранным блоком памяти переключения в матричном коммутаторе становят594547

ся невозможными, поскольку сигнал низкого уровня на выходе элемента ИЛИ-НЕ, поступающий на синхровходы D-триггеров, блокирует его переключение и сохраняет такое распределение памяти,которое существовало непосредственно до подачи данного адреса ращения.

5

0

5

0

5

0

Формула изобретения

Устройство для адресации блоков памяти, содержащее группу из п переключателей (где п - количество адресуемых блоков памяти), регистр адреса, дешифратор адреса,, матричный коммутатор, причем информационный вход регистра адреса является адресным входом устройства, выходы регистра адреса соединены с входами дешифратора адреса, выходы дешифратора адреса соединены с п входами первой группы матричного коммутатора, п выходов которого являются выходами устройства, отличающееся тем, .тем, что, с целью повьш1ения надежности работы за счет способности устройства блокировать возможное прерывание выборки блока до завершения сеанса обмена с блоком памяти, в него введены элемент ИЛИ-НЕ и группа из п D- триггеров, причем выходы регистра ад:г реса соединены с входами элемента ИЛИ-НЕ, выход элемента ШШ-НЕ соединен с входами синхронизации D-триггеров группы, их выходы - с соответствующими входами второй группы матричного блока коммутации, информационные входы D-триггеров соединены с выходами соответствующих переключателей группы.

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-09-26—Подача