Фиг.-/

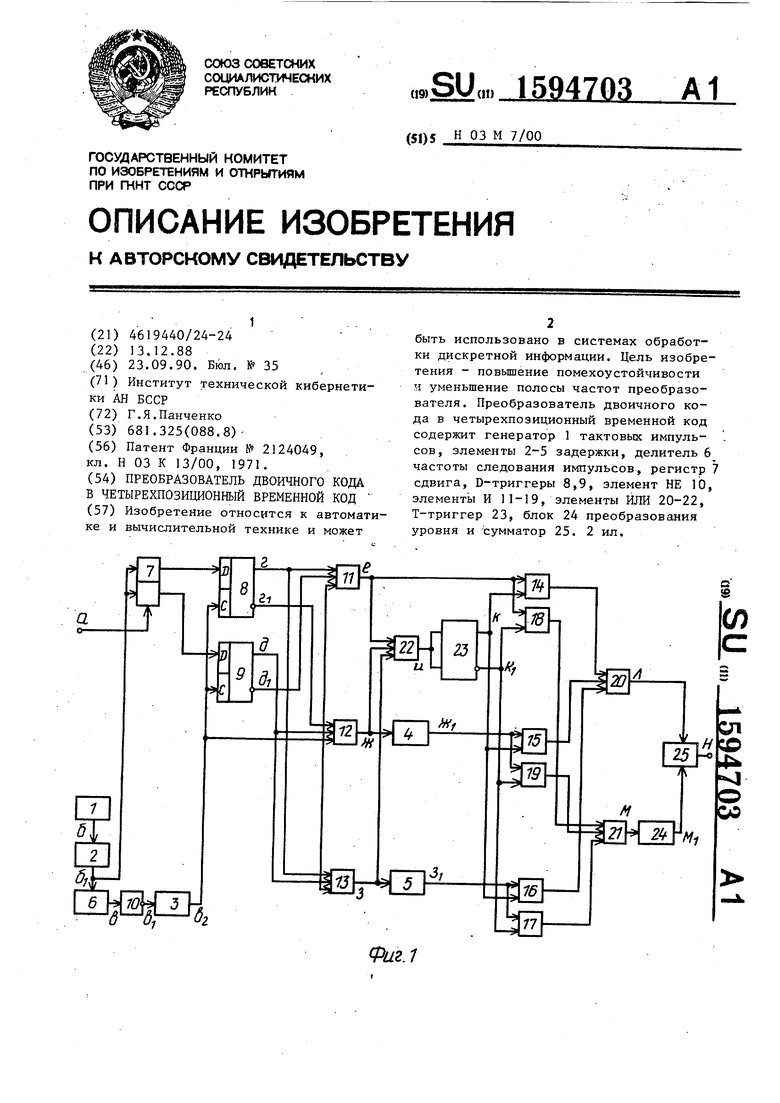

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки дискретной информации, Цель изобретения - повышение помехустойчивости и уменьшение полосы частот преобразователя.

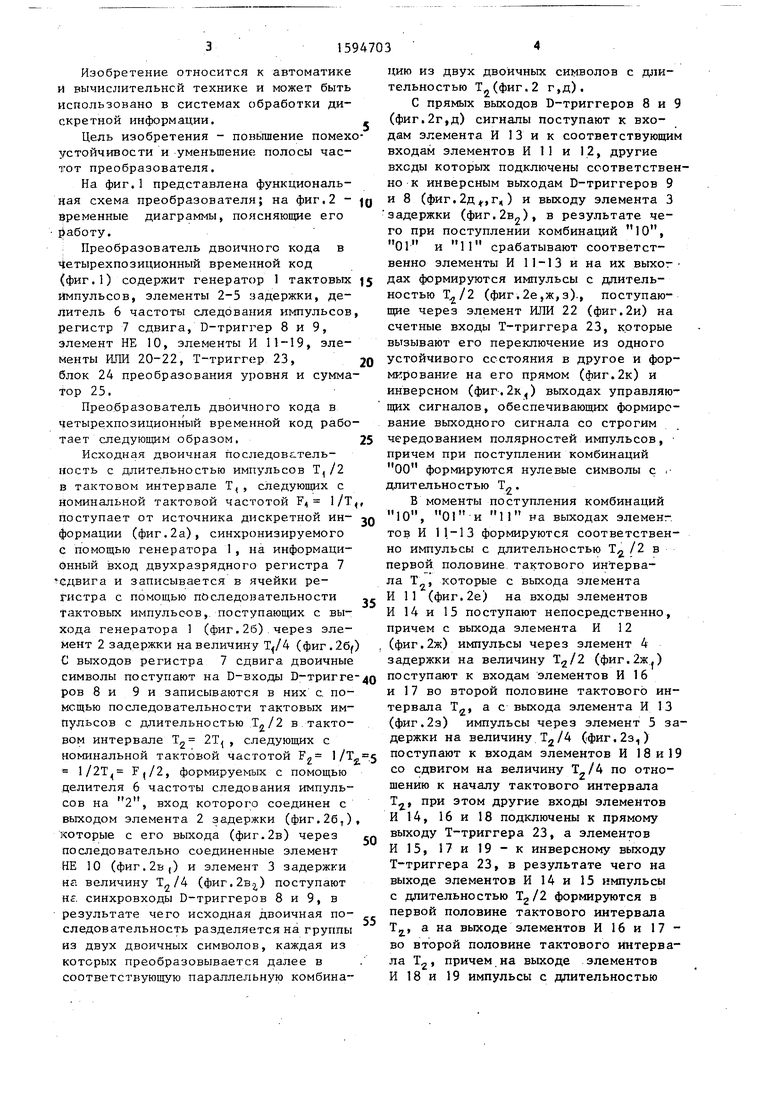

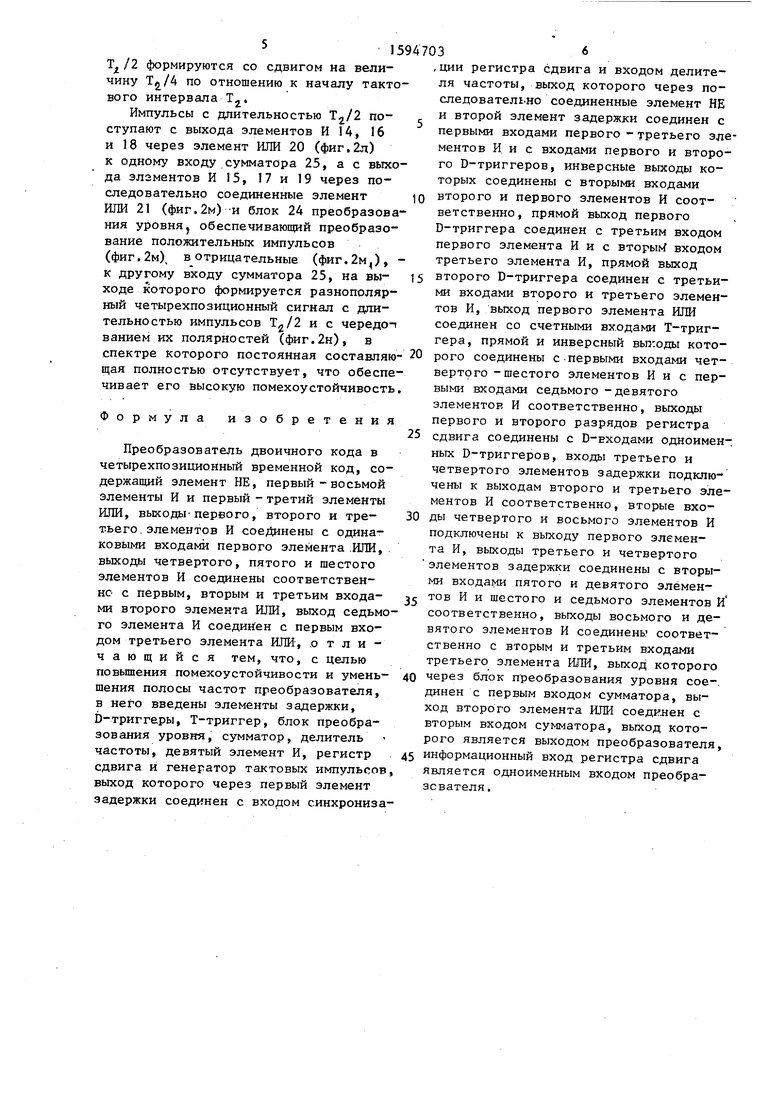

На фиг.1 представлена функциональная схема преобразователя; на фиг.2 - временные диаграммы, поясняющие его работу,

Преобразователь двоичного кода в Четырехпозиционный временной код (фиг,1) содержит генератор 1 тактовых импульсов, элементы 2-5 задержки, делитель 6 частоты следования импульсов регистр 7 сдвига, D-триггер 8 и 9, элемент НЕ 10, элементы И 11-19, элементы ИЛИ 20-22, Т-триггер 23, блок 24 преобразования уровня и сум:ма тор 25.

Преобразователь двоичного кода в четырехпозиционный временной код работает следующим образом.

Исходная двоичная последов.тель- ность с длительностью импульсов Т,/2 в тактовом интервале Т,, следуюпщх с номинальной тактовой частотой Рц l/T поступает от источника дискретной ин- формации (фиг,2а), синхронизируемого е помощью генератора 1, на информационный вход двухразрядного регистра 7 Сдвига и записывается в ячейки регистра с помощью последовательности taKTOBbix импульсов, поступающих с выхода генератора 1 (фиг,26) через элемент 2 задержки на величину (фиг,2б С выходов регистра 7 сдвига двоичные символы поступают на D-входы В-тригге ров 8 и 9 и записываются в них с, по- мсщью последовательности тактовых им- Пульсов с длительностью в тактовом интервале 1 2Т , следующих с номинальной тактовой частотой 7 1/Т 1/2Т F(/2, формируемых с помощью делителя 6 частоты следования импульсов на 2, вход которого соединен с выходом элемента 2 задержки (фиг,26,) которые с его выхода (фиг.2в) через последовательно соединенные элемент НЕ 10 (фиг.2в,) и элемент 3 задержки на величину (фиг.2в.2) поступают Не. синхровходы D-триггеров 8 и 9, в результате чего исходная двоичная последовательность разделяется на группы из двух двоичных символов, каждая из которых преобразовывается далее в соответствующую параллельную комбина

д ,5 п

5

цию из двух двоичных символов с длительностью Т2(фиг.2 г,д).

С прямых выходов D-триггеров 8 и 9 (фиг.2г,д) сигналы поступают к входам элемента И 13 и к соответствующим входам элементов И 11 и 12, другие входы которых подключены ссответствен- но к инверсным выходам D-триггеров 9 и 8 (фиг,2д,г, ) и выходу элемента 3 задержки (фиг.2в2), в результате чего при поступлении комбинаций 10, 01 и 11 срабатывают соответственно элементы И 11-13 и на их выхог дах формируются импульсы с длительностью (фиг,2е,ж,з)., поступающие через элемент ИЛИ 22 (фиг,2и) на счетные входы Т-триггера 23, которые вызывают его переключение из одного устойчивого состояния в другое и формирование на его прямом (фиг.2к) и инверсном (фиг.2к,) выходах управляющих сигналов, обеспечивающих формирование выходного сигнала со строгим чередованием полярностей импульсов, причем при поступлении комбинаций 00 формируются нулевые символы с .- длительностью Т.

В моменты поступления комбинаций 10, 01 и П на выходах элемен-. тов и 11-13 формируются соответственно импульсы с длительностью Т /2 в первой половине тактового интервала Т , которые с выхода элемента И 11 (фиг.2е) на входы элементов И 14 и 15 поступают непосредственно, причем с выхода элемента И 12 (фиг,2ж) импульсы через элемент 4 задержки на величину (фиг.2ж.) поступают к входам элементов И 16 и 17 во второй половине тактового интервала Tg, ас вьтода элемента И 13 (фиг,2з) импульсы через элемент 5 задержки на величину Tj/4 (фиг.2з,) поступают к входам элементов И 18 и 19 со сдвигом на величину Т /4 по отношению к началу тактового интервала Т, при этом другие входы элементов И 14, 16 и 18 подключены к прямому выходу Т-триггера 23, а элементов И I5, 17 и 19 - к инверсному выходу Т-триггера 23, в результате чего на выходе элементов И 14 и 15 импульсы с длительностью Т2/2 формируются в первой половине тактового интервала Tj, а на выходе элементов И 16 и 17 - во второй половине тактового интервала причем на выходе элементов И 18 и 19 импульсы с длительностью

T.J /2 формируются со сдвигом на величину по отношению к началу такто15

вого интервала Т,

Импульсы с длительностью поступают с выхода элементов И 14, 16 и 18 через элемент ИЛИ 20 (фиг.2л) к одному входу сумматора 25, а с выхода элэментов И 15, 17 и 19 через последовательно соединенные элемент ИЛИ 21 (фиг.2м) -и блок 24 преобразования уровняJ обеспечивающий преобразование положительных импульсов (фиг.2мХ неотрицательные (фиг. 2м,), - к другому входу сумматора 25, на вы- ходе которого формируется разнополяр- ный четырехпозиционный сигнал с длительностью импульсов Т2/2 и с чередо-i ванием их полярностей (фиг.2н), в спектре которого постоянная составляю- щая полностью отсутствует, что обеспечивает его высокую помехоустойчивость.

4

Формула изобретения

Преобразователь двоичного кода в четырехпозиционный временной код, содержащий элемент НЕ, первый - восьмой элементы И и первый - третий элементы ИЛИ, выходы-первого, второго и третьего, элементов И соединены с одинаковыми входами первого элемента .ИЛИ, выходы четвертого, пятого и щестого элементов И соединены соответственно с первым, вторым и третьим входами второго элемента РШИ, выход седьмого элемента И соединен с первым входом третьего элемента ИЛИ-, .отличающийся тем, что, с целью повьшения помехоустойчивости и умень- щения полосы частот преобразователя, в него введены элементы задержки, Ь-триггеры, Т-триггер, блок преобразования уровня, сумматор, делитель - частоты, девятый элемент И, регистр сдвига и генератор тактовых импульсов выход которого через первый элемент задержки соединен с входом синхронизато1594703

ю|520

,ции регистра сдвига и входом делителя частоты, выход которого через последовательно соединенные элемент НЕ и второй элемент задержки соединен с первыми входами первого - третьего элементов И и с входами первого и второго D-триггеров, инверсные выходы которых соединены с вторыми входами второго и первого элементов И соот- ветственно, прямой выход первого D-триггера соединен с третьим входом первого элемента И и с вторы входом третьего элемента И, прямой выход второго D-триггера соединен с третьими входами второго и третьего элементов И, выход первого элемента ИЛИ соединен со счетными входами Т-триг- гера, прямой и инверсный вьп:оды которого соединены с-первыми входами четвертого -шестого элементов И и с первыми входами седьмого -девятого элементов И соответственно, выходы первого и второго разрядов регистра сдвига соединены с D-входами одноименных D-триггеров, входы третьего и четвертого элементов задержки подключены к выходам второго и третьего элементов И соответственно, вторые входы четвертого и восьмого элементов И подключены к выходу первого элемента И, выходы третьего и четвертого элементов задержки соединены с вторыми входами пятого и девятого элементов И и шестого и седьмого элементов И соответственно, выходы восьмого и девятого элементов И соединены соответственно с вторым и третьим входами третьего элемента ИЛИ, выход которого через блок преобразования уровня сое-. дивен с первым входом сумматора, выход второго элемента ИЛИ соединен с вторым входом сумматора, выход которого является выходом преобразователя, 5 информационный вход регистра сдвига является одноименным входом преобразователя.

25

30

5

0

hhh Р h

III

h p h n h рН|гК

п;гтт-1 п nln П|П-Г1| .t

eiP

72/2

h-l

P

im im ir

t

h-L

P

bi

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в четырех-позиционный временной код | 1990 |

|

SU1757104A1 |

| Преобразователь двоичного кода в восьмипозиционный временной код | 1990 |

|

SU1730725A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки дискретной информации. Цель изобретения - повышение помехоустойчивости и уменьшение полосы частот преобразователя. Преобразователь двоичного кода в четырехпозиционный временной код содержит генератор 1 тактовых импульсов, элементы 2-5 задержки, делитель 6 частоты следования импульсов, регистр 7 сдвига, D-триггеры 8,9, элемент НЕ 10, элементы И 11-19, элементы ИЛИ 20-22, Т-триггер 23, блок 24 преобразования уровня и сумматор 25. 2 ил.

2f 7

e ж 3

1

1 и

H

Л

;

H

Fb

г/г

tf

J

J

-

ё

ijT/

Авторы

Даты

1990-09-23—Публикация

1988-12-13—Подача