Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных отказоустойчивых вычислительных комплексов.

Цель изобретения - повышение надежности за счет обеспечения скользящего резерва каналов системы.

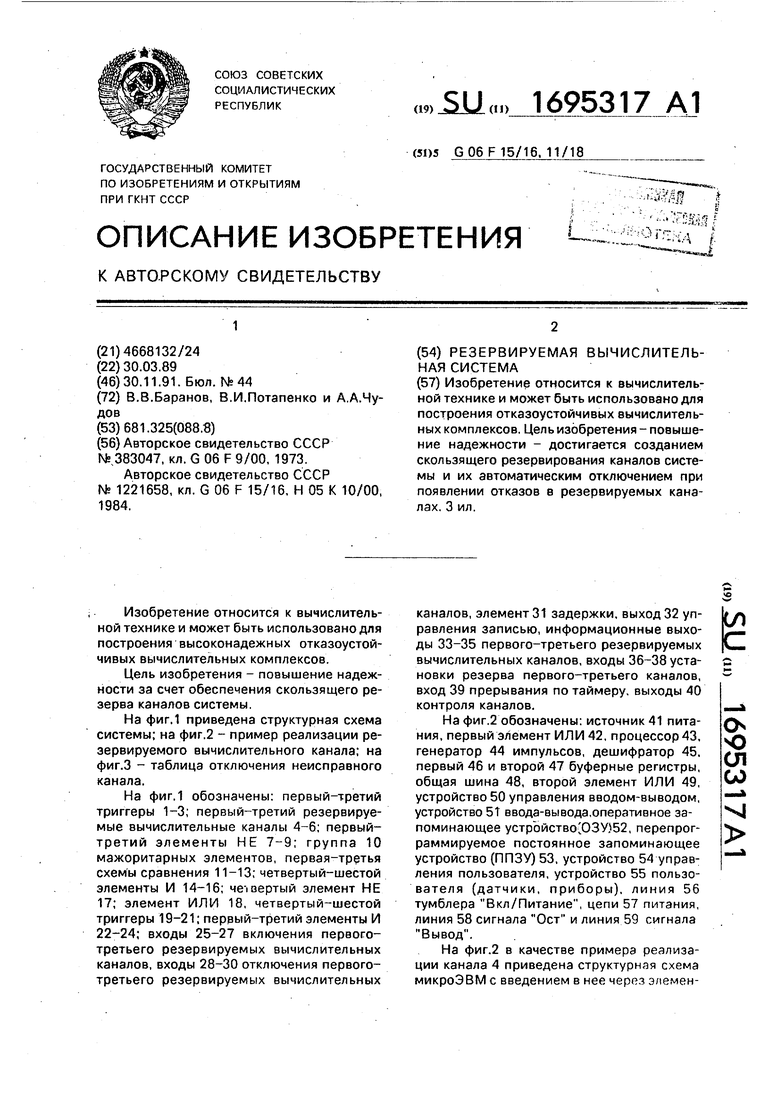

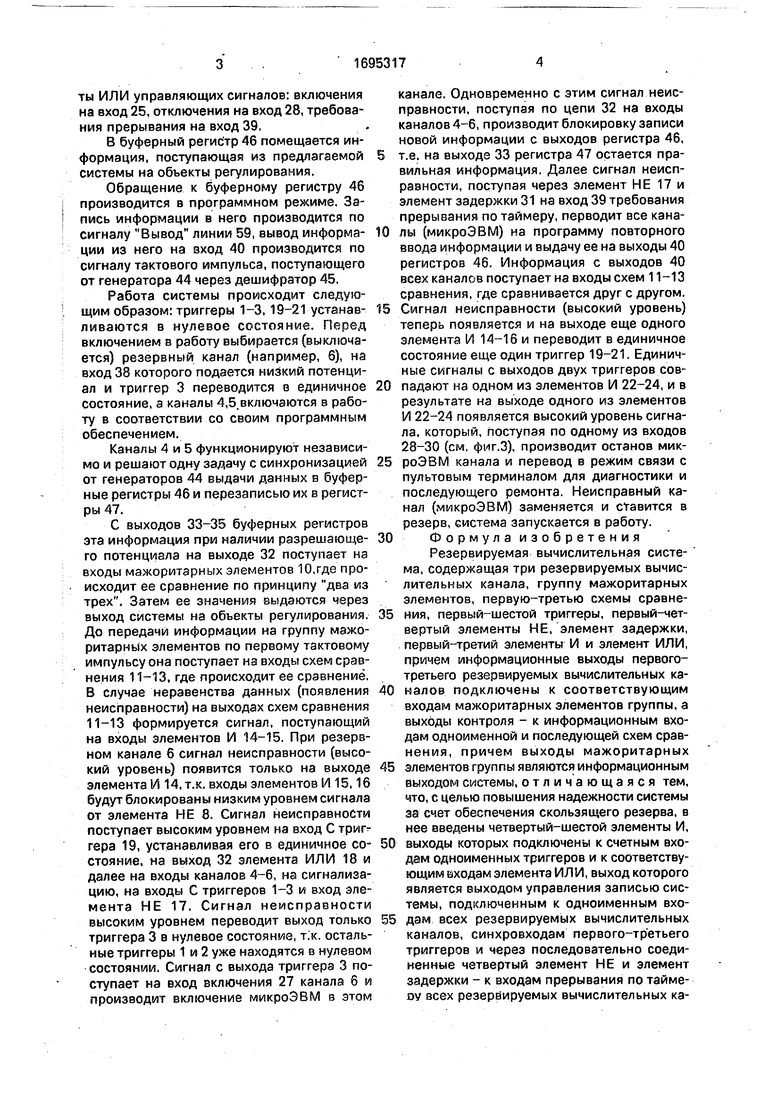

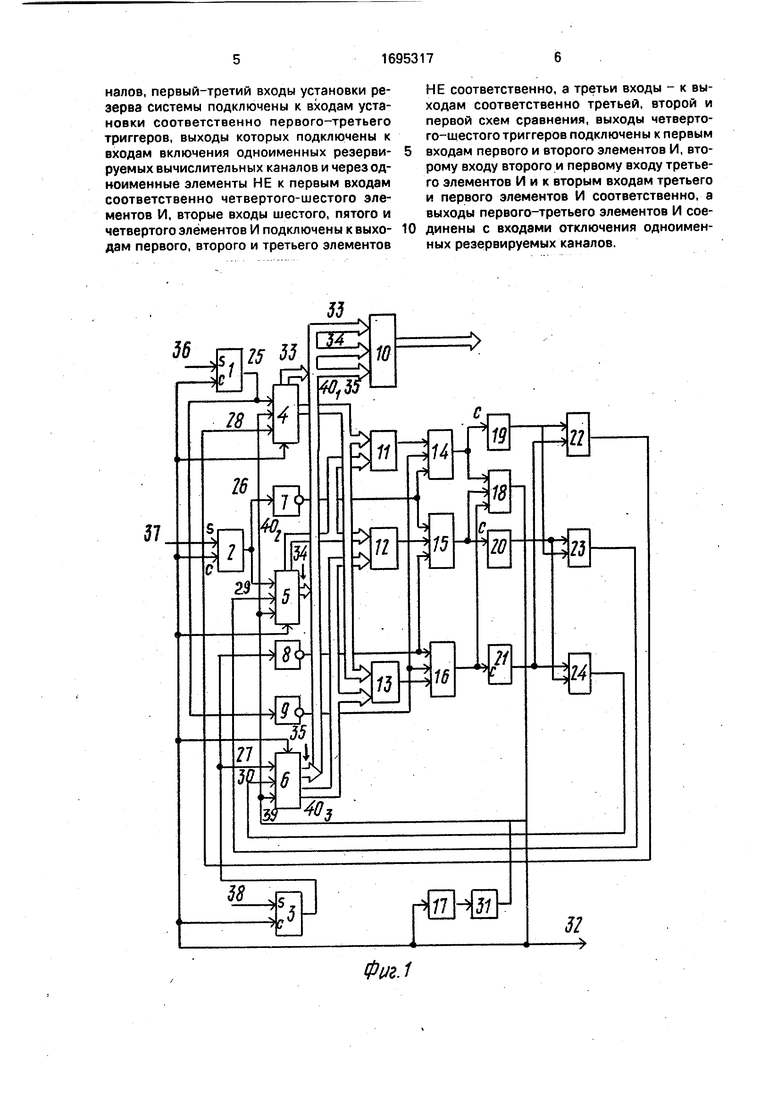

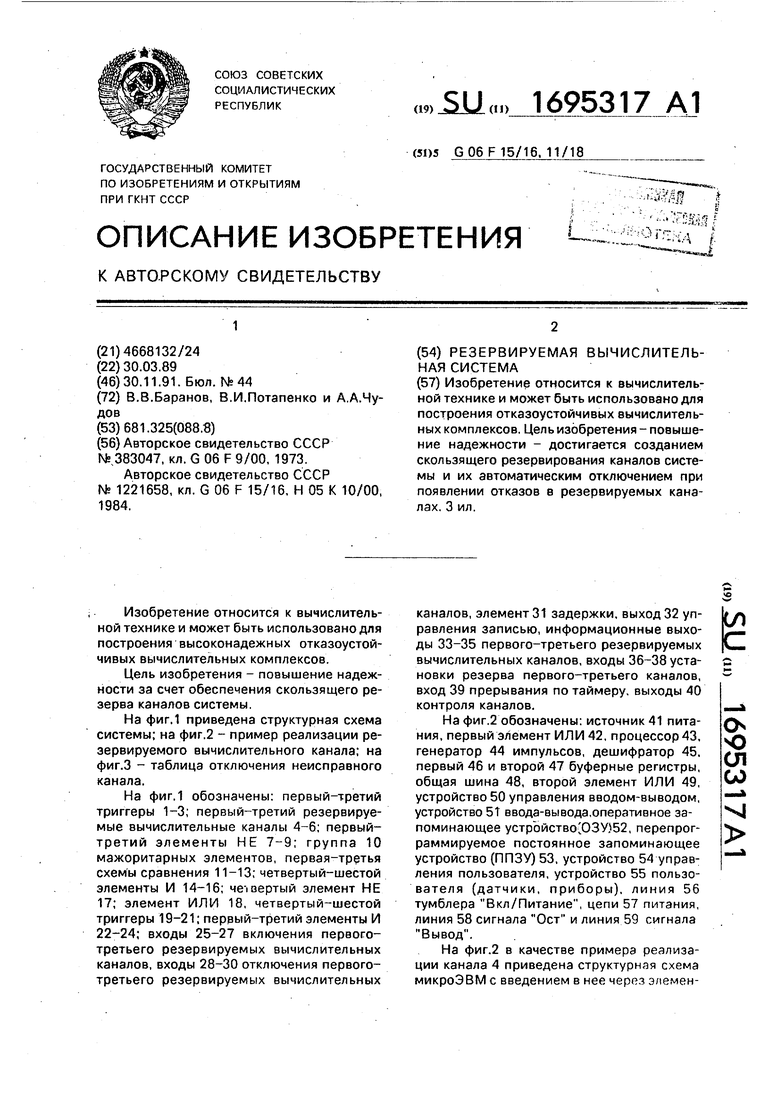

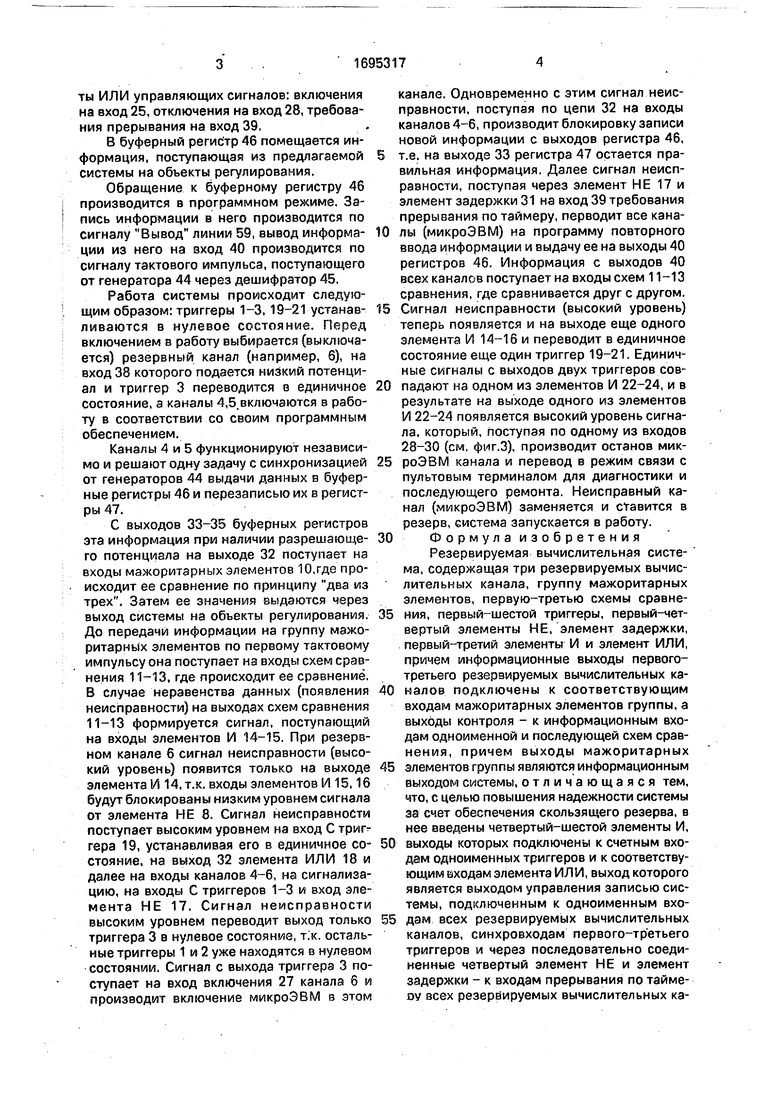

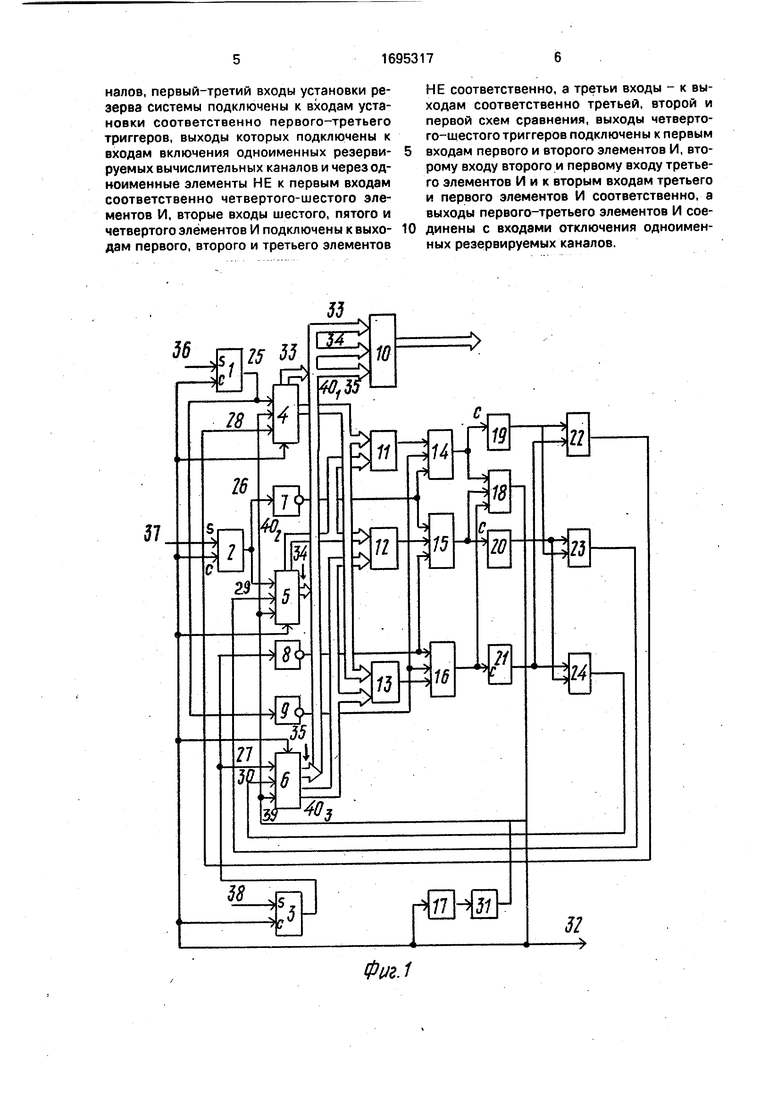

На фиг.1 приведена структурная схема системы; на фиг.2 - пример реализации резервируемого вычислительного канала; на фиг.З - таблица отключения неисправного канала.

На фиг.1 обозначены: первый-третий триггеры 1-3; первый-третий резервируемые вычислительные каналы 4-6; первый- третий элементы НЕ 7-9; группа 10 мажоритарных элементов, первая-третья схемы сравнения 11-13; четвертый-шестой элементы И 14-16; четвертый элемент НЕ 17; элемент ИЛИ 18, четвертый-шестой триггеры 19-21; первый-третий элементы И 22-24; входы 25-27 включения первого- третьего резервируемых вычислительных каналов, входы 28-30 отключения первого- третьего резервируемых вычислительных

каналов, элемент 31 задержки, выход 32 управления записью, информационные выходы 33-35 первого-третьего резервируемых вычислительных каналов, входы 36-38 установки резерва первого-третьего каналов, вход 39 прерывания по таймеру, выходы 40 контроля каналов.

На фиг.2 обозначены: источник 41 питания, первый элемент ИЛИ 42, процессор 43, генератор 44 импульсов, дешифратор 45, первый 46 и второй 47 буферные регистры, общая шина 48, второй элемент ИЛИ 49, устройство 50 управления вводом-выводом, устройство 5Т ввода-вывода,оперативное запоминающее устройствоЈ)ЗУ}52, перепрограммируемое постоянное запоминающее устройство (ППЗУ) 53, устройство 54 управления пользователя, устройство 55 пользователя (датчики, приборы), линия 56 тумблера Вкл/Питание, цепи 57 питания, линия 58 сигнала Ост и линия 59 сигнала Вывод.

На фиг.2 в качестве примера реализации канала 4 приведена структурная схема микроЭВМ с введением в нее через элеменOs

о ел

00

ч

ты ИЛИ управляющих сигналов: включения на вход 25, отключения на вход 28, требования прерывания на вход 39.

В буферный регистр 46 помещается информация, поступающая из предлагаемой системы на объекты регулирования.

Обращение к буферному регистру 46 производится в программном режиме. Запись информации в него производится по сигналу Вывод линии 59, вывод информации из него на зход 40 производится по сигналу тактового импульса, поступающего от генератора 44 через дешифратор 45.

Работа системы происходит следующим образом: триггеры 1-3,19-21 устанавливаются в нулевое состояние. Перед включением в работу выбирается (выключается) резервный канал (например, 6), на вход 38 которого подается низкий потенциал и триггер 3 переводится в единичное состояние, а каналы 4,5.включаются в работу в соответствии со своим программным обеспечением.

Каналы 4 и 5 функционируют независимо и решают одну задачу с синхронизацией от генераторов 44 выдачи данных в буферные регистры 46 и перезаписью их в регистры 47,

С выходов 33-35 буферных регистров эта информация при наличии разрешающего потенциала на выходе 32 поступает на входы мажоритарных элементов 10,где происходит ее сравнение по принципу два из трех. Затем ее значения выдаются через выход системы на объекты регулирования. До передачи информации на группу мажо- ритарнУх элементов по первому тактовому импульсу она поступает на входы схем сравнения 11-13, где происходит ее сравнение. В случае неравенства данных (появления неисправности) на выходах схем сравнения 11-13 формируется сигнал, поступающий на входы элементов И 14-15. При резервном канале 6 сигнал неисправности (высокий уровень) появится только на выходе элемента И 14, т.к. входы элементов И 15,16 будут блокированы низким уровнем сигнала от элемента НЕ 8. Сигнал неисправности поступает высоким уровнем на вход С триггера 19, устанавливая его в единичное состояние, на выход 32 элемента ИЛИ 18 и далее на входы каналов 4-6, на сигнализацию, на входы С триггеров 1-3 и вход элемента НЕ 17. Сигнал неисправности высоким уровнем переводит выход только триггера 3 в нулевое состояние, т.к. остальные триггеры 1 и 2 уже находятся в нулевом состоянии. Сигнал с выхода триггера 3 поступает на вход включения 27 канала 6 и производит включение микроЭВМ в этом

канале. Одновременно с этим сигнал неисправности, поступая по цепи 32 на входы каналов 4-6, производит блокировку записи новой информации с выходов регистра 46,

т.е. на выходе 33 регистра 47 остается правильная информация. Далее сигнал неисправности, поступая через элемент НЕ 17 и элемент задержки 31 на вход 39 требования прерывания по таймеру, перводит все кана0 лы (микроЭВМ) на программу повторного ввода информации и выдачу ее на выходы 40 регистров 46. Информация с выходов 40 всех каналов поступает на входы схем 11-13 сравнения, где сравнивается друг с другом.

5 Сигнал неисправности (высокий уровень) теперь появляется и на выходе еще одного элемента И 14-16 и переводит в единичное состояние еще один триггер 19-21. Единичные сигналы с выходов двух триггеров сов0 падают на одном из элементов И 22-24, и в результате на выходе одного из элементов Л 22-24 появляется высокий уровень сигнала, который, поступая по одному из входов 28-30 (см, фиг.З), производит останов мик5 роЭВМ канала и перевод в режим связи с пультовым терминалом для диагностики и последующего ремонта. Неисправный канал (микроЭВМ) заменяется и с авится в резерв, система запускается в работу.

0 Формула изобретения

Резервируемая вычислительная система, содержащая три резервируемых вычислительных канала, группу мажоритарных элементов, первую-третью схемы сравне5 Ния, первый-шестой триггеры, первый-чет- вертый элементы НЕ, элемент задержки, первый-третий элементы И и элемент ИЛИ, причем информационные выходы первого- третьего резервируемых вычислительных ка0 налов подключены к соответствующим входам мажоритарных элементов группы, а выходы контроля - к информационным входам одноименной и последующей схем сравнения, причем выходы мажоритарных

5 элементов группы являются информационным ЁЫХОДОМ системы, отличающаяся тем, что, с целью повышения надежности системы за счет обеспечения скользящего резерва, в нее введены четвертый-шестой элементы И,

0 выходы которых подключены к счетным входам одноименных триггеров и к соответствующим входам элемента ИЛИ, выход которого является выходом управления записью системы, подключенным к одноименным вхо5 дам всех резервируемых вычислительных каналов, синхровходам первого-третьего триггеров и через последовательно соединенные четвертый элемент НЕ и элемент задержки - к входам прерывания по тайме- DV всех резерёируемых вычислительных каналов, первый-третий входы установки резерва системы подключены к входам установки соответственно первого-третьего триггеров, выходы которых подключены к входам включения одноименных резервируемых вычислительных каналов и через одноименные элементы НЕ к первым входам соответственно четвертого-шестого элементов И, вторые входы шестого, пятого и четвертого элементов И подключены к выходам первого, второго и третьего элементов

0

НЕ соответственно, а третьи входы - к выходам соответственно третьей, второй и первой схем сравнения, выходы четвертого-шестого триггеров подключены к первым входам первого и второго элементов И, второму входу второго и первому входу третьего элементов И и к вторым входам третьего и первого элементов И соответственно, а выходы первого-третьего элементов И соединены с входами отключения одноименных резервируемых каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Система обработки информации | 1990 |

|

SU1795468A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Резервированное устройство | 1981 |

|

SU982006A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Резервированное устройство | 1991 |

|

SU1830575A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения отказоустойчивых вычислительных комплексов. Цель изобретения - повышение надежности - достигается созданием скользящего резервирования каналов системы и их автоматическим отключением при появлении отказов в резервируемых каналах. 3 ил.

Фиг.1

| Авторское свидетельство СССР №,383047, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мажоритарно-резервированная управляющая система | 1984 |

|

SU1221658A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-03-30—Подача