И; устро

ной в

Hal

схема

фиг. устро

НИИ, Э.

10 и иия pt

ЦИИ,

с

обраш

обретение относится к запоминающим 1ствам и может ,быть использовано в аппаратуре передачи данных устройств автоматики и вычислительной техники.

Цель изобретения - расширение области применения устройства за счет произволь- (ешней адресации памяти, фиг. 1 представлена функциональная предлагаемого устройства; на фиг. 2 - функциональная схема блока управления; на 3 - временные диаграммы работы 1ства.

Ус-ройство содержит блок 1 управления, комму гатор 2, счетчик 3, первый 4 и второй 5 регистры, первый 6 и второй 7 блоки сравне- темент И 8, адресный выход 9, первый торой 11 синхровходы, вход 12 зада- жима, выход 13 окончания регенера- аяресный вход 14.

:1ыхода 9 поступают строчные адреса ения к динамической памяти, на синхровходы 10 и II поступают синхросигналы соответственно Т1, Т2, на вход 12 - сигнал задания режима внешнего обмена устройства ВО, с выхода 13 поступает сигнал окончания регенерации КР, на вход 14 - строчные адреса внешних обращений AR. С первого выхода схемы 6 сравнения поступает сигнал «Больше, с первого выхода блока 7 сравнения - сигнал «Равно, со второго - «Меньше.

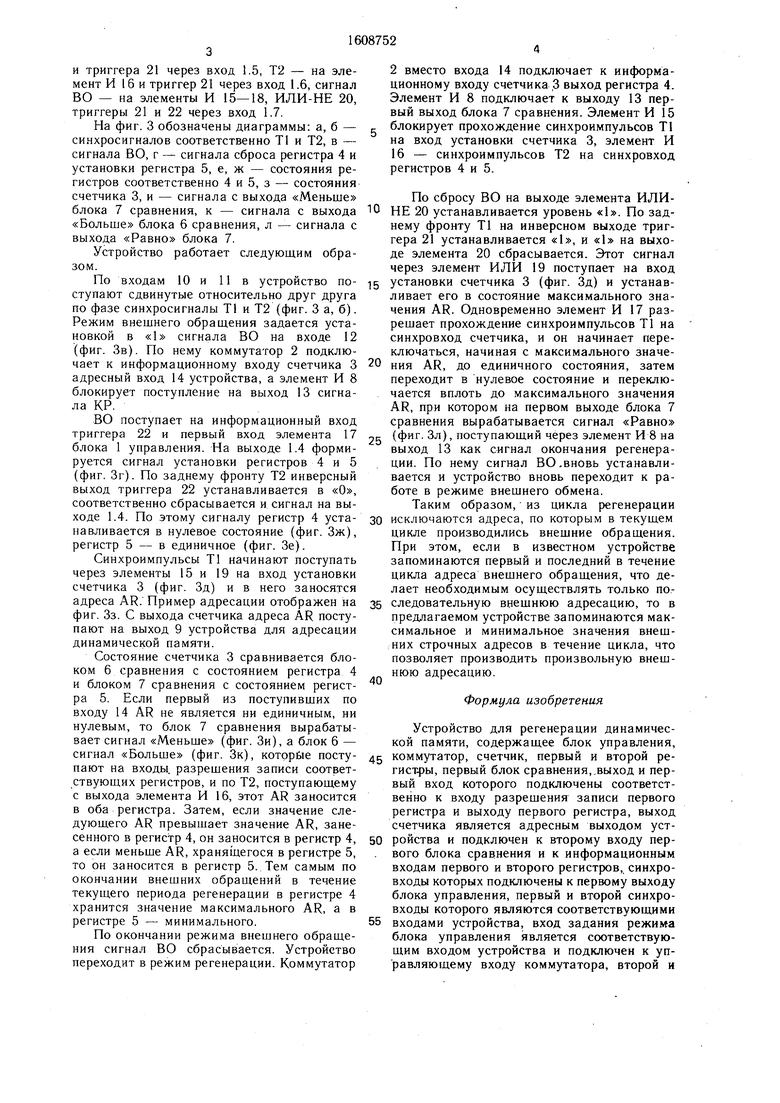

Блок 1 управления содержит (фиг. 2) элементы И 15-18, ИЛИ 19,ИЛИ-НЕ 20 и триггеры 21 и 22. Сигналы модификации счетчика 3 поступают с выхода элемента И 17 через выход 1.1 блока 1 управления, установки счетчика - с элемента ИЛИ 19 через выход 1.2, сигнал на синхровходы регистров 5,4- с элемента И 16 через выход 1.3, на сброс регистра 4 и установку регистра 5 - с элемента И 18 через выход 14. Синхросигнал Т1 поступает на входы элементов И 15 и 17

а

о

00

СП ГС

и триггера 21 через вход 1.5, Т2 - на элемент И 16 и триггер 21 через вход 1.6, сигнал ВО - на элементы И 15-18, ИЛИ-НЕ 20, триггеры 21 и 22 через вход 1.7.

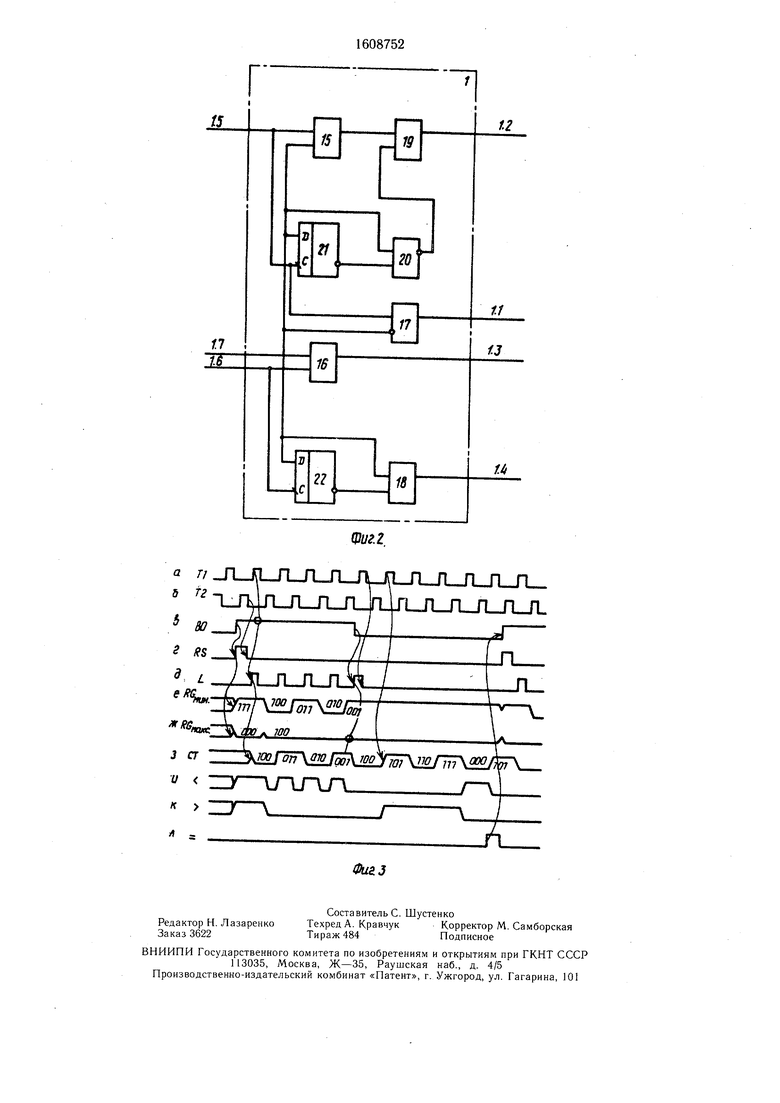

На фиг. 3 обозначены диаграммы: а, б - синхросигналов соответственно Т1 и Т2, в - сигнала ВО, г - сигнала сброса регистра 4 и установки регистра 5, е, ж - состояния регистров соответственно 4 и 5, з - состояния счетчика 3, и - сигнала с выхода «Меньше блока 7 сравнения, к - сигнала с выхода «Больше блока 6 сравнения, л - сигнала с выхода «Равно блока 7.

Устройство работает следуюш.им образом.

По входам 10 и 11

входам 1и и 11 в устройство поступают сдвинутые относительно друг друга по фазе синхросигналы Т1 и Т2 (фиг. 3 а, б). Режим внешнего обращения задается установкой в «1 сигнала ВО на входе 12 (фиг. Зв). По нему коммутатор 2 подключает к информационному входу счетчика 3 адресный вход 14 устройства, а элемент И 8 блокирует поступление на выход 13 сигнала КР.

ВО поступает на информационный вход триггера 22 и первый вход элемента 17 блока 1 управления. На выходе 1.4 формируется сигнал установки регистров 4 и 5 (фиг. Зг). По заднему фронту Т2 инверсный выход триггера 22 устанавливается в «О, соответственно сбрасывается и сигнал на выходе 1.4. По этому сигналу регистр 4 устанавливается в нулевое состояние (фиг. Зж), регистр 5 - в единичное (фиг. Зе).

Синхроимпульсы Т1 начинают поступать через элементы 15 и 19 на вход установки счетчика 3 (фиг. Зд) и в него заносятся адреса AR. Пример адресации отображен на фиг. Зз. С выхода счетчика адреса AR поступают на выход 9 устройства для адресации динамической памяти.

Состояние счетчика 3 сравнивается блоком 6 сравнения с состоянием регистра 4 и блоком 7 сравнения с состоянием регистра 5. Если первый из поступивших по входу 14 AR не является ни единичным, ни нулевым, то блок 7 сравнения вырабатывает сигнал «Меньше (фиг. Зи), а блок 6 - сигнал «Больше (фиг. Зк), которые поступают на входы, разрешения записи соответствующих регистров, и по Т2, поступающему с выхода элемента И 16, этот AR заносится в оба регистра. Затем, если значение следующего AR превышает значение AR, занесенного в регистр 4, он заносится в регистр 4, а если меньше AR, храня1цегося в регистре 5, то он заносится в регистр 5. Тем самым по окончании внешних обращений в течение текущего периода регенерации в регистре 4 хранится значение максимального AR, а в регистре 5 - минимального.

По окончании режима внешнего обращения сигнал ВО сбрасывается. Устройство переходит в режим регенерации. Коммутатор

2 вместо входа 14 подключает к информационному входу счетчика ,3 выход регистра 4. Элемент И 8 подключает к выходу 13 первый выход блока 7 сравнения. Элемент И 15 блокирует прохождение синхроимпульсов Т1 на вход установки счетчика 3, элемент И 16 - синхроимпульсов Т2 на синхровход регистров 4 и 5.

По сбросу ВО на выходе элемента ИЛИНЕ 20 устанавливается уровень «1. По заднему фронту Т1 на инверсном выходе триггера 21 устанавливается «1, и «1 на выходе элемента 20 сбрасывается. Этот сигнал через элемент ИЛИ 19 поступает на вход установки счетчика 3 (фиг. Зд) и устанавливает его в состояние максимального значения AR. Одновременно элемент И 17 разрешает прохождение синхроимпульсов Т1 на синхровход счетчика, и он начинает переключаться, начиная с максимального значения AR, до единичного состояния, затем переходит в нулевое состояние и переключается вплоть до максимального значения AR, при котором на первом выходе блока 7 сравнения вырабатывается сигнал «Равно

(фиг. 3л), поступающий через элемент ИВ на выход 13 как сигнал окончания регенерации. По нему сигнал ВО,вновь устанавливается и устройство вновь переходит к работе в режиме внешнего обмена.

Таким образом, из цикла регенерации

исключаются адреса, по которым в текушем цикле производились внешние обращения. При этом, если в известном устройстве запоминаются первый и последний в течение цикла адреса внешнего обращения, что делает необходимым осуществлять только последовательную внешнюю адресацию, то в предлагаемом устройстве запоминаются максимальное и минимальное значения внешних строчных адресов в течение цикла, что позволяет производить произвольную внешнюю адресацию.

Формула изобретения

Устройство для регенерации динамической памяти, содержащее блок управления,

коммутатор, счетчик, первый и второй ре- , первый блок сравнения,,выход и первый вход которого подключены соответственно к входу разрешения записи первого регистра и выходу первого регистра, выход счетчика является адресным выходом устройства и подключен к второму входу пер- вого блока сравнения и к информационным входам первого и второго регистров, синхро- входы которых подключены к первому выходу блока управления, первый и второй синхро- входы которого являются соответствующими

входами устройства, вход задания режима блока управления является соответствующим входом устройства и подключен к управляющему входу коммутатора, второй и

третий

ны

ляющ«

блока

nepeoijo

целью

рой

сации

выходы блока управления подключе- гветственно к счетному входу и управ- му входу счетчика, четвертый выход управления подключен к входу сброса регистра, отличающееся тем, что, с расширения области применения уст- за счет произвольной внешней адре- памяти, оно содержит второй блок сравнения и элемент И, выход которого является выходом окончания регенерации устройства, первый и второй входы элемента И подключены соответственно к входу задания режима блока управления и первому

iCTia

выходу второго блока сравнения, второй выход которого подключен к входу разрешения записи второго регистра, вход установки которого подключен к четвертому выходу блока управления, первый и второй входы второго блока сравнения подключены соответственно к выходу второго регистра и выходу счетчика, информационный вход которого подключен к выходу коммутатора, первый информационный вход которого подключен к выходу первого регистра, второй информационный вход коммутатора является адресным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| Устройство для сортировки информации | 1990 |

|

SU1795450A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для распределения и регенерации динамической памяти | 1989 |

|

SU1735857A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в аппаратуре передачи данных устройств автоматики и вычислительной техники. Цель изобретения - расширение области применения устройства за счет произвольной внешней адресации памяти. Устройство содержит блок управления, коммутатор, счетчик, два регистра, две схемы сравнения, элемент И и имеет адресные вход и выход, вход задания режима внешнего обращения, выход окончания регенерации и два синхровхода. В регистрах запоминаются максимальное и минимальное значения строчных адресов внешнего обращения в текущем цикле. В режиме регенерации счетчик перебирает строчные адреса, начиная с запомненного максимального адреса вплоть до запомненного минимального. Тем самым из процесса регенерации исключаются адреса внешних обращений текущего цикла при обеспечении непрерывно-произвольной внешней адресации. 3 ил.

Фиг.

о TJ

5 тг

ВО

-luT L/ J

л

/1

| Авторское свидетельство СССР № , кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| институт | |||

Авторы

Даты

1990-11-23—Публикация

1988-12-27—Подача