/У

сп о 00 |

ел

ел

Изобретение относится к вычислительмой технике н может быть иепользовано для отбраковки болыиих интегральных схем (БИС) оперативных заномкнающих уетройств (ОЗУ).

Цель изобретения -- повышение быстродействии устройства за счет исключения избыточных циклов контроля записи информации.

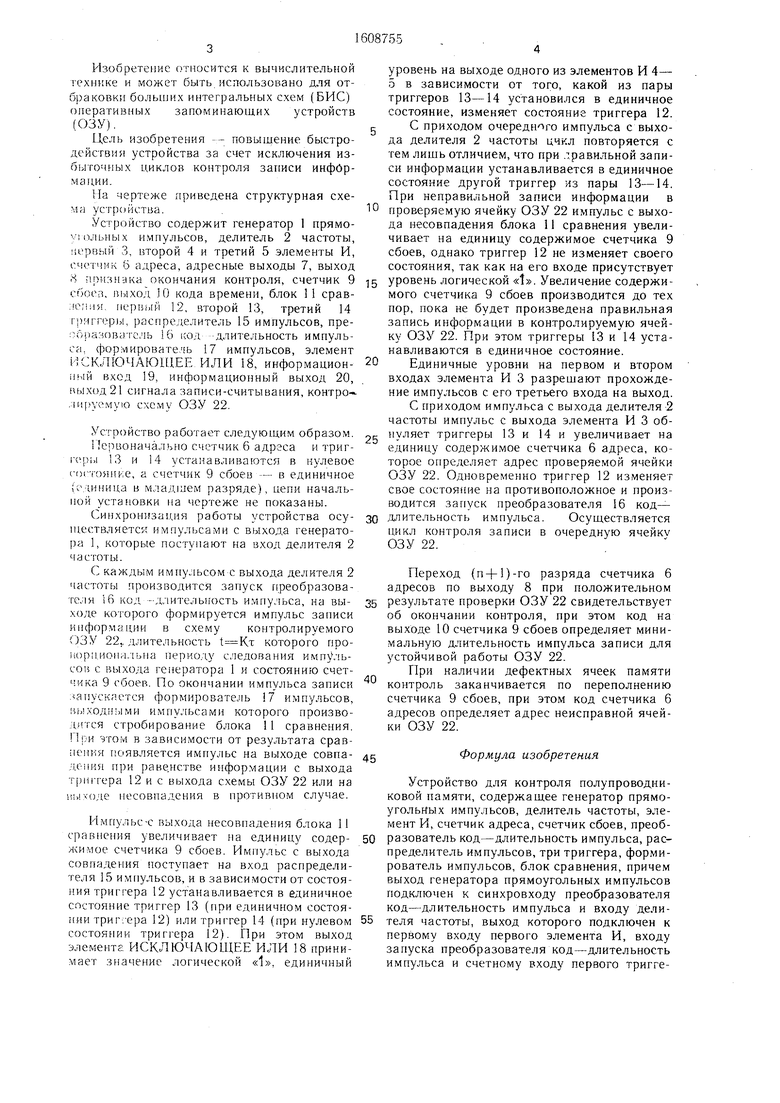

На чертеже приведена структурная схема устройства.

Устройство содержит генератор 1 прямо- viixribHbix импульсов, делитель 2 частоты, 3, второй 4 и третий 5 элементы И, счетчик 6 адреса, адресные выходы 7, выход 8 ; ризнака окончания контроля, счетчик 9 сбооа, выход 10 кода времени, блок 11 срав- ле.пяя. перылй 12, второй 13, третий 14 rpHrrcpjji, распре;1.елитель 15 импульсов, пре- :;5(1азов;)тс,чь 16 код -длите,1 ьность импуль- ся. фор;у1ировате ь 17 импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, информационный вход 19, информационный выход 20, и)1ход 21 сигнала записи-считывания, кoнтpo- ;1И| уему10 схему ОЗУ 22.

Устройство работает следующим образом.

1 ервоначально счетчик 6 адреса и триг- | ср; 1 13 и 14 устанавливаются в нулевое coi(-ояние, а счетчик 9 сбоев - в единичное (о.чииица в младшем разряде), цепи начальной установки на чертеже не показаны.

Синхронизация работы устройства осу- Н1ествлиетс;-т импульсами с выхода генератора 1, которые поступают на вход делителя 2 частоты.

С каждым импульсом с выхОлВд делителя 2 частоты производится запуск преобразователя 16 код -длительность и.мпульса, на выходе которого формируется импульс записи информации в схему контролируемого Г}ЗУ 22,, длительность которого про- 1юрииона. 1ьпа Периоду следования импуль- еон с выхода генератора 1 и СОСТОЯНИЕО счетчика 9 сбоев. По окончании импульса записи : апускается формирователь 7 импульсов, :1ыход; ,1ми импульсами которого производится стробирование блока 11 сравнения. 1ри этом в зависимости от результата сравнения появляется импульс на выходе совпа- /i.CiiHH при раве.нстве информации с выхода трштера 12 и с выхода схемы ОЗУ 22 или на .ьг . оде несовпадения в противном случае.

Импульс-с выхода несовнадения блока И сравнения увеличивает па единицу содержимое счетчика 9 сбоев. Импульс с выхода совпадения поступает на вход распределителя 15 импульсов, и в зависимости от состояния триггера 12 устанавливается в единичное состояние триггер 13 (при единичном состоянии триггера 12) или триггер 14 (при нулевом состоянии триггера 12). При этом выход элементе. ИСКЛЮЧАЮЩЕЕ ИЛИ 18 принимает значение логической «1, единичный

уровень на выходе одного из элементов И 4-

5в зависимости от того, какой из пары триггеров 13-14 установился в единичное состояние, изменяет состояние триггера 12.

g С приходом очередного импульса с выхода делителя 2 частоты цчкл повторяется с тем лишь отличием, что при .травильной записи информации устанавливается в единичное состояние другой триггер из пары 13-14. При неправильной записи информации в

0 проверяемую ячейку ОЗУ 22 импульс с выхода несовпадения блока 11 сравнения увеличивает на единицу содержимое счетчика 9 сбоев, однако триггер 12 не изменяет своего состояния, так как на его входе присутствует

5 уровень логической «t. Увеличение содержимого счетчика 9 сбоев производится до тех пор, пока не будет произведена правильная запись информации в контролируемую ячейку ОЗУ 22. При этом триггеры 13 и 14 устанавливаются в единичное состояние.

0 Единичные уровни на первом и втором входах элемента И 3 разрешают прохождение импульсов с его третьего входа на выход. С приходом импульса с выхода делителя 2 частоты импульс с выхода элемента И 3 обс нуляет триггеры 13 и 14 и увеличивает на единицу содержимое счетчика 6 адреса, которое определяет адрес проверяемой ячейки ОЗУ 22. Одновременно триггер 12 изменяет свое состояние на противоположное и производится запуск преобразователя 16 код-

0 ..вдительность импульса. Осуш,ествляется н,икл контроля записи в очередную ячейку ОЗУ 22.

Переход (п+1)-го разряда счетчика 6

адресов по выходу 8 при положительном

5 результате проверки ОЗУ 22 свидетельствует

06окончании контроля, при этом код на выходе 10 счетчика 9 сбоев определяет минимальную длительность импульса записи для устойчивой работы ОЗУ 22.

При наличии дефектных ячеек памяти контроль заканчивается по переполнению счетчика 9 сбоев, при этом код счетчика 6 адресов определяет адрес неисправной ячейки ОЗУ 22.

0

45

Формула изобретения

Устройство для контроля полупроводниковой памяти, содержащее генератор прямоугольных импульсов, делитель частоты, элемент И, счетчик адреса, счетчик сбоев, преобразователь код-длительность импульса, распределитель импульсов, три триггера, формирователь импульсов, блок сравнения, причем выход генератора прямоугольных импульсов подключен к синхровходу преобразователя код-длительность импульса и входу делителя частоты, выход которого подключен к первому входу первого элемента И, входу запуска преобразователя код-длительность импульса и счетному входу первого триггеpa,

НЫМ Ы

ляюшим

вторь м

внени1я

рого

ройстЬа

входом

являк

и ПОД1

разовзтел

ход № ПИСИ-(

входо л тороп блока соеди

сов, П(

йены и трет динен

д которого является информацион- лодом устройства и соединен с управ- входом распределителя импульсов к информационным входом блока сра- первый информационный вход кото- является информационным входом уст- а выход нчсовпадеиня соедкнек с счетчика сбоев, выходы которого 1ТСЯ выходами кода времени устройства шючены к установочным входам преоб- :ля ход-длительность 1 мпуль€а, вы- торого является выходом сигнала за- штываяия устройства и соединен с формирователя импульсов, выход ко- подключен к входу стробнровакия сравнения, выход совпадения которого ген с входом распределителя импуль- фвый и второй выходы которого соеди- с З-входа-ми соответственно второго ьего триггеров, R-входы которых сое- Ы с выходом первого элемента И и

П)

р.ходо 5 счетчика адреса, выходы младших разрядов которого являются адресными вы- ходаУ . устройства, а выход старшего разряда является выходом признака окончания KCHT|jC:;iH усгройства отличающееся тем, что, с целый Н)ЕЫ;. быстродействия устройства, 3 -него введены элем ент ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, причем выход вторюго триггера соединен с вторым входом второго элемента И и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход третьего триггера соединен с вторым входом третьего элемента И и вторым входом элемента ИСКЛЮЧАЬЭЩЕГ:. ИЛИ, выход которого соединен с первыми входами второго и треть- его элементов I;, выходы которых подключены соответственно к R- и S-входам первого триггера, выходы второго и третьего триггеров соединоньч ссютветственно с вторым и третьим входами первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1425788A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Параллельный статистический анализатор отклонений и колебаний напряжения | 1982 |

|

SU1076913A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для записи информации в оперативную память | 1990 |

|

SU1751811A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1345264A1 |

Изобретение относится к вычислительной технике и может быть использовано для отбраковки больших интегральных схем оперативных запоминающих устройств. Цель изобретения - повышение быстродействия устройства за счет исключения избыточных циклов контроля записи информации. Устройство содержит генератор 1 прямоугольных импульсов, делитель 2 частоты, элементы И 3-5, счетчик 6 адресов, счетчик 9 сбоев, блок 11 сравнения, триггеры 12 - 14, распределитель импульсов 15, преобразователь 16 код-длительность импульса, формирователь 17 импульсов и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18. При наличии дефектных ячеек памяти контроль заканчивается по переполнению счетчика сбоев 9. При этом код счетчика 6 адресов определяет адрес неисправной ячейки оперативного запоминающего устройства. 1 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Бюл | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Шланговое соединение | 0 |

|

SU88A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-11-23—Публикация

1988-12-12—Подача