Устройство относится к вычислительной технике и может быть использовано для отбраковки больших интегральных схем (БИС) оперативной памяти.

Цель изобретения - повьшение достоверности контроля за счет определения минимально возможной длительности сигнала зйписи.

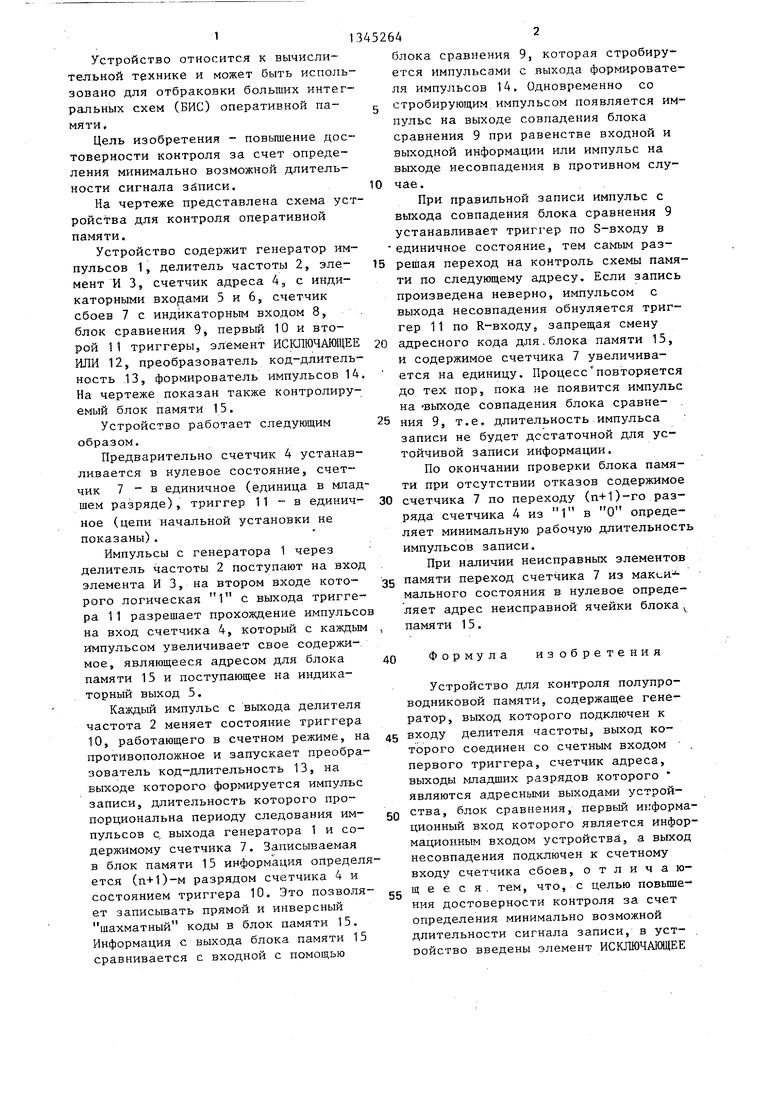

На чертеже представлена схема устройства для контроля оперативной памяти.

Устройство содержит генератор импульсов 1, делитель частоты 2, элемент И 3, счетчик адреса А, с индикаторными вхорами 5 и 6, счетчик сбоев 7 с индикаторным входом 8, блок сравнения 9, первый 10 и второй 11 триггеры, элемент ИС1ШЮЧАЮЩЕЕ ИЛИ 12, преобразователь код-длительность ,13, формирователь импульсов 14 На чертеже показан также контролируемый блок памяти 15.

Устройство работает следующим образом.

Предварительно счетчик 4 устанавливается в нулевое состояние, счетчик 7 - в единичное (единица в младшем разряде), триггер 11 - в единичное (цепи начальной установки не показаны).

Импульсы с генератора 1 через делитель частоты 2 поступают на вход элемента И 3, на втором входе которого логическая 1 с выхода триггера 11 разрешает прохождение импульсо на вход счетчика 4, который с каждым Импульсом увеличивает свое содержимое, являющееся адресом для блока памяти 15 и поступающее на индикаторный выход 5.

Каждьш импульс с выхода делителя частота 2 меняет состояние триггера 10, работающего в счетном режиме, на противоположное и запускает преобразователь код-длительность 13, на выходе которого формируется импульс записи, длительность которого пропорциональна периоду следования импульсов с, выхода генератора 1 и содержимому счетчика 7. Записываемая в блок памяти 15 информация определяется (п+1)-м разрядом счетчика 4 и состоянием триггера 10. Это позволяет записывать прямой и инверсный шахматный коды в блок памяти 15. Информация с выхода блока памяти 15 сравнивается с входной с помощью

. .

в

3452642

блока сравнения 9, которая стробиру ется импульсами с выхода формирователя импульсов 14,

Одновременно со

g стробирующим импульсом появляется импульс на выходе совпадения блока сравнения 9 при равенстве входной и выходной информации или импульс на выходе несовпадения в противном слу10 чае.

При правильной записи импульс с выхода совпадения блока сравнения 9 устанавливает триггер по S-входу в единичное состояние, тем самым раз15 решая переход на контроль схемы памяти по следующему адресу. Если запись произведена неверно, импульсом с выхода несовпадения обнуляется триггер 11 по R-входу, запрещая смену

20 адресного кода для,блока памяти 15, и содержимое счетчика 7 увеличивается на единицу. Процесс повторяется до тех пор, пока не появится импульс на -выходе совпадения блока сравне- .

25 ния 9, т.е. длительность импульса : записи не будет достаточной для устойчивой записи информации.

По окончании проверки блока памяти при отсутствии отказов содержимое

30 счетчика 7 по переходу (п+1)-го разряда счетчика 4 из 1 в О определяет минимальную рабочую длительность импульсов записи.

При наличии неисправных элементов

35 памяти переход счетчика 7 из макси- мального состояния в нулевое определяет адрес неисправной ячейки блока

, памяти 15.

40 Формула изобретения

Устройство для Контроля полупроводниковой памяти, содержащее генератор, выход которого подключен к 45 входу делителя частоты, выход которого соединен со счетным входом , первого триггера, счетчик адреса, выходы младших разрядов которого являются адресными выходами устройства, блок сравнения, первый информационный вход которого является информационным входом устройства, а выход несовпадения подключен к счетному входу счетчика сбоев, о т л и ч а ю- щ е е с я . тем, что, с целью повыше ния достоверности контроля за счет определения минимально возможной длительности сигнала записи, в устройство введены элемент ИСКЛЮЧАЮЩЕЕ

50

55

ИЛИ, элемент и, второй триггер, преобразователь код-длительность и формирователь импульсов, причем выхо ды счетчика сбоев являются выходами кода времени цикла устройства и подключены к установочньм входам преобразователя код-длительность, выход которого является выходом записи-считывания устройства и соединен с входом формирователя импульсов выход которого подключен к входу стробирования блока сравнения, выходы совпадения и несовпадения которого соединены соответственно с S-, R-входами второго триггера, выход которого, подключен к первому

Редактор И. Сегляник Заказ 4927/51

Составитель 0. Исаев

Техред Л.Сердюкова Корректор А. Обручар

Тираж 587Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035-, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

входу элемента И, второй вход которого соединен с выходом делителя частоты и с входом запуска преобразователя код-длительность, синхровход которого подключен к выходу генератора, выход элемента И соединен со счетным входом счетчика адреса, выход старшего, разряда которого является выходом окончания контроля устройства и соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого триггера, а выход является кнформацион21ым выходом устройства и соединен с вторым информационным входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1425788A1 |

| Устройство для контроля полупроводниковой памяти | 1988 |

|

SU1608755A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для контроля блоков памяти | 1987 |

|

SU1437925A1 |

Изобретение относится к вычислительной технике и может быть использовано для.отбраковки больших интегральных схем оперативной памяти, Целью изобретения является повышение достоверности контроля за счет определения минимально возможной длительности сигнала записи. Устройство содержит генератор 1 импульсов, делитель 2 частоты, элемент И 3, счетчик 4 адреса с индикаторными входами 5 и 6, счетчик 7 сбоев с индикаторным входом 8, блок 9 сравнения, триггеры 10, 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, преобразователь 13 код-длительность, формирователь 14 импульсов, контро- , лируемьш блок 15 памяти. 1 ил. оо 4 СП го 05 4

| Устройство для контроля оперативного накопителя информации | 1972 |

|

SU443414A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-15—Публикация

1985-11-15—Подача