to ел -vj

00 00

Изобретение относится к вычислительной технике и может быть использовано для отбраковки больших интегральных схем (БИС) памяти.

Цель изобретения - повышение дос- товерности контроля.

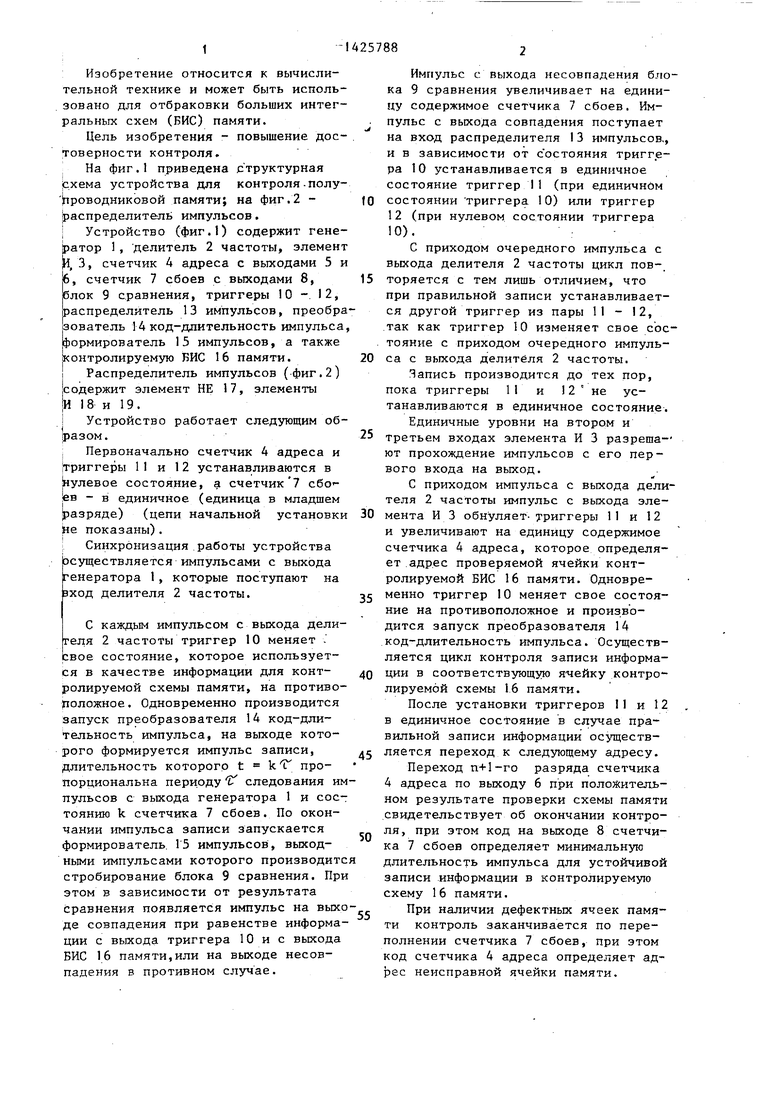

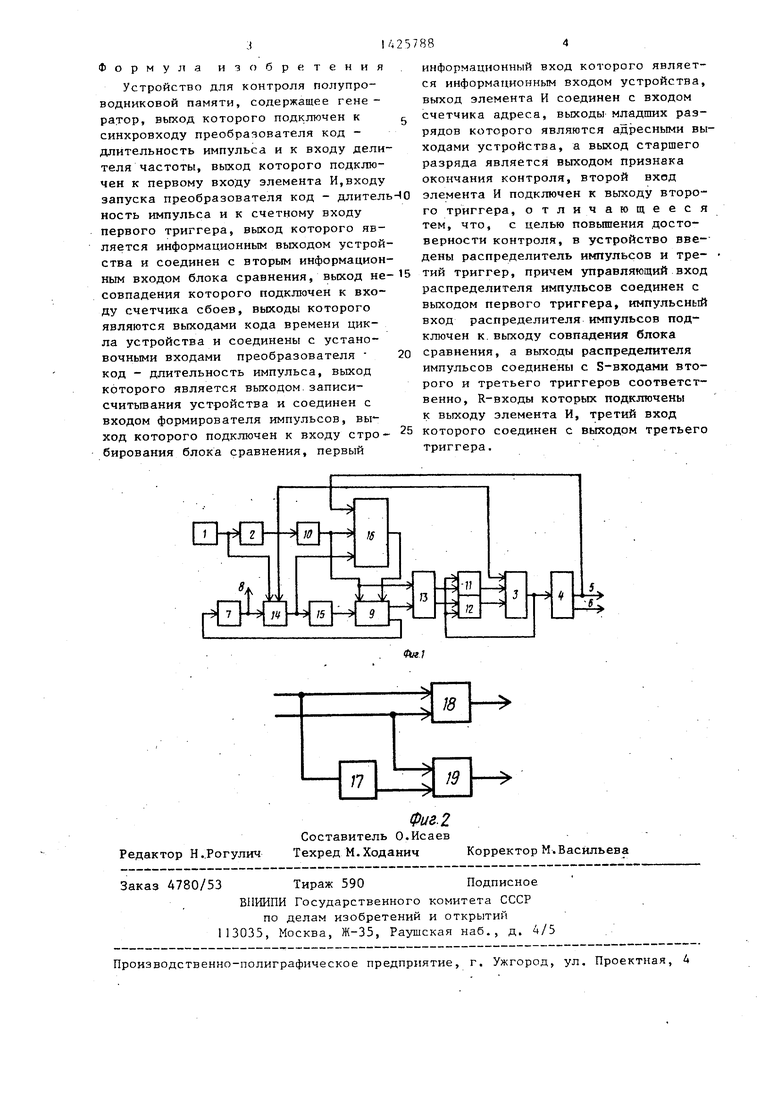

На фиг.1 приведена структурная рхема устройства для контроля-полу- Ьроводниковой памяти; на фиг.2 - распределитель импульсов. I Устройство (фиг.О содержит генератор 1, делитель 2 частоты, элемент , 3, счетчик 4 адреса с выходами 5 и

счетчик 7 сбоев с выходами 8, лок 9 сравнения, триггеры 10 . 12, аспределитель 13 импульсов, преобра Ьователь 14 код-длительность импульса, формирователь 15 импульсов, а также Контролируемую БИС 16 памяти. I Распределитель импульсов (-фиг. 2) Ьодержит элемент НЕ 17, элементы |И 1 8 и 1 9 .

I Устройство работает следующим образом.

; Первоначально счетчик 4 адреса и Триггеры 11 и 12 устанавливаются в {улевое состояние, а счетчик 7 сбо Ьв - в единичное (единица в младшем разряде) (цепи начальной установки не показаны).

I Синхронизация работы устройства Осуществляется импульсами с выхода генератора 1, которые поступают на зход делителя 2 частоты.

С каждым импульсом с выхода делителя 2 частоты триггер 10 меняет . tBoe состояние, которое используется в качестве информации для конт- ролируемой схемы памяти, на противоположное. Одновременно производится запуск преобразователя 14 код-длительность импульса, на выходе которого формируется импульс записи, длительность которого t kf пропорциональна периоду t следования импульсов с выхода генератора 1 и состоянию k счетчика 7 сбоев. По окончании импульса записи запускается формирователь. 15 импульсов, выход- импульсами которого производитс стробирование блока 9 сравнения. При этом в зависимости от результата сравнения появляется импульс на выходе совпадения при равенстве информации с выхода триггера 10 и с выхода БИС 16 памяти,или на выходе несовпадения в противном случае.

0

5

0

5

0

5

0

0

5

Импульс с выхода несовпадения блока 9 сравнения увеличивает на единицу содержимое счетчика 7 сбоев. Импульс с выхода совпадения поступает на вход распределителя 13 импульсов., и в зависимости от с остояния триггера 10 устанавливается в единичное состояние триггер I1 (при единичном состоянии триггера 10) или триггер 12 (при нулевом состоянии триггера 10).

С приходом очередного импульса с выхода делителя 2 частоты цикл пов-. торяется с тем лишь отличием, что при правильной записи устанавливается другой триггер из пары 11 - 12, так как триггер 10 изменяет свое состояние с приходом очередного импульса с выхода делителя 2 частоты.

Яапись производится до тех пор, пока триггеры 11 и 12 не устанавливаются в единичное состояние.

Единичные уровни на втором и третьем входах элемента И 3 разрешают прохождение импульсов с его первого входа На выход.

ti

С приходом импульса с выхода делителя 2 частоты импульс с выхода элемента ИЗ обнуляет- триггеры 11 и 12 и увеличивают на единицу содержимое счетчика 4 адреса, которое определяет адрес проверяемой ячейки контролируемой БИС 16 памяти. Одновременно триггер 10 меняет свое состояние на противоположное и производится запуск преобразователя 14 код-длительность импульса. Осуществляется цикл контроля записи информации в соответствующую я-чейку контролируемой схемы 16 памяти.

После установки триггеров II и 12 в единичное состояние в слзгчае правильной записи информации осуществляется переход к следующему адресу.

Переход п+1-го разряда счетчика 4 адреса по выходу 6 при положительном результате проверки схемы памяти свидетельствует об окончании контроля, при этом код на выходе 8 счетчика 7 сбоев определяет минимальную длительность импульса для устойчивой записи информации в контролируемую схему 16 памяти.

При наличии дефектных ячеек памяти контроль заканчивается по переполнении счетчика 7 сбоев, при этом код счетчика 4 адреса определяет адрес неисправной ячейки памяти.

:i

Формула изобретения

Устройство для контроля полупроводниковой памяти, содержащее гене - ратор, выход которого подключен к синхровходу преобразователя код - длительность импульса и к входу делителя частоты, выход которого подключен к первому входу элемента И,входу запуска преобразователя код - длитель ность импульса и к счетному входу первого триггера, выход которого является информационным выходом устройства и соединен с вторым информационным входом блока сравнения, выход несовпадения которого подключен к входу счетчика сбоев, выходы которого являются выходами кода времени цикла устройства и соединены с установочными входами преобразователя код - длительность импульса, выход которого является выходом,записи- считьгоания устройства и соединен с входом формирователя импульсов, выход которого подключен к входу стро- бирования блока сравнения, первый

/ 25788

О 5

0

5

информационный вход которого является информационным входом устройства, выход элемента И соединен с входом счетчика адреса, выходы младших раэ- рядов которого являются адресными выходами устройства, а вькод старшего разряда является выходом признака окончания контроля, второй вход элемента И подключен к выходу второго триггера, отличающееся тем, что, с целью повышения достоверности контроля, в устройство вне- дены распределитель импульсов и третий триггер, причем управляющий вход распределителя импульсов соединен с выходом первого триггера, импульсный вход распределителя импульсов подключен к вьпсоду совпадения блока сравнения, а выходы распределителя импульсов соединены с S-входами второго и третьего триггеров соответственно, R-входы которых подключены к выходу элемента И, третий вход которого соединен с выходом третьего триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1988 |

|

SU1608755A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1345264A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение относится к вычислительной технике и может быть использовано для отбраковки больших интегральных схем (БИС) памяти. Целью изобретения является повьшение достоверности контроля. Устройство содержит генератор, делитель частоты, элемент И, счетчик адреса, счетчик сбоев, соединенный с установочными входами преобразователя код - длительность импульса, блок сравнения, первьй, второй и третий триггеры, распределитель импульсов и формирователь импульсов. В устройстве осуществляется последовательная запись и счи- тьгаание нуля и единицы по всем ячейкам контролируемой БИС памяти, причем время цикла вначале устанавливается минимальным, а затем увеличивается на один дискрет после каждой ошибки считывания. После окончания контроля на выходе устройства формируется код ьшнимального времени цикла БИС памяти, при котором обеспечивается устойчивая запись и считьшание информации. 2 ил. с (Л

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1345264A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-09-23—Публикация

1986-12-12—Подача