Изобретение относится к импульсной технике и может быть использова- .но при построении аппаратной части умножителей двоичных чисел.

Целью изобретения является расширение функциональных возможностей путем увеличения разрядности операндов.

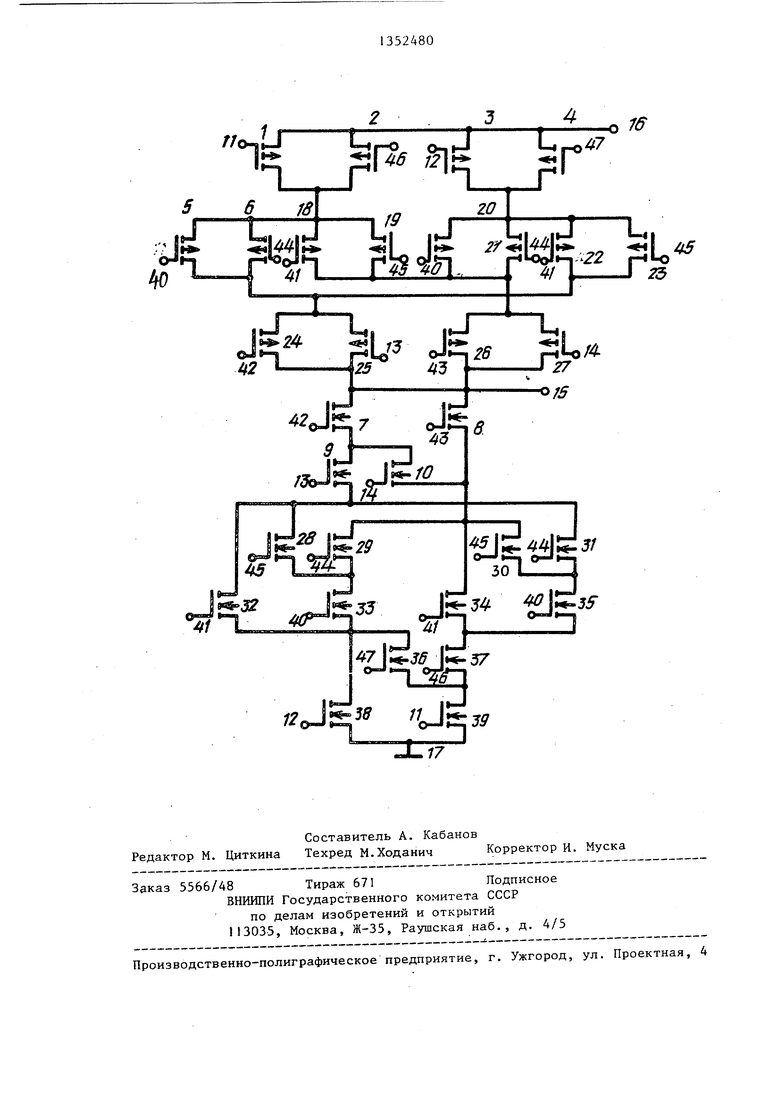

На чертеже представлена электрическая принципиальная схема логического элемента матричного умножителя.

Устройство содержит первый - шестой р-транзисторы 1-6, первый - четвертый п-транзисторы 7-10, прямую и инверсную шины 11 и 12 кулевого разряда первого операнда, прямую и инверсную шины 13 и 14 нулевого разряда второго операнда, инверсную шину

15 результата, шину 16 питания, общую JQ рого п-транзисторов 7 и 8 соединены

шину 17, затвор первого р-транзистора 1 соединен с прямой шиной 11 нулес выходной шиной 15 результата, стоки первого и второго р-транзисторов 1 и 2 соединены со стоками с пятого по восьмой р-транзисторов 5,6,18 и 25 19, стоки третьего и четвертого р- транзисторов 3 и 4 соединены со сто ками с девятого по двенадцатый р- транзисторов 20...23, истоки пятого, шестого, одиннадцатого и двенадцатового разряда первого операнда, затвор третьего р-транзистора 3 соединен с инверсной шиной 12 нулевого разряда первого операнда, с седьмого по шестнадцатьш р-транзисторы 18-27, с пятого по шестнадцатый п-транзисторы 28-39, прямзгю и инверснзпо шины 40

41 первого разряда пе.рвого операн-зо го р-транзисторов 5,6,22,23 соединены

и

да, прямую и инвевсную шины 42 и 43 второго разряда первого, операнда, прямую и инверсную шины 44 и 45 первого разряда второго операнда, прямую и инверсную шины 46 и 47 второго разряда второго операнда, шина 11 соединена с затвором шестнадцатого п-транзистора 39, шина 12 соединена с затвором пятнадцатого п-транзистора 38, шина 40 соединена с затворами пятого р-транзистора 5, девятого р-транзис- гора 20, десятого п-транзистора 33 и двенадцатого п-транзистора 35, шина 41 соединена с затворами седьмого р-транзистора 18, одиннадцатого р- транзистора 22, девятого п-транзистора 32 и одиннадцатого п-транзистора 34, шина 42 соединена с затворами тринадцатого р-транзистора 24 и первого п-транзистора 7, шина 43 соединена с затворами пятнадцатого р-тран- зистора 26 и второго п-транзистора 8, шина 13 соединена с затворами- четырнадцатого р-транзистора 25 и третьего п-транзистора 9, шина 14 соединена с затворами шестнадцатого р-транзистора 27 и четвертого п-транзистора 14, шина 44 соединена с затворами шестого р-транзистора 6, десятого

35

40

45

50

55

со стоками тринадцатого и четырнадцатого р-транзисторов 24 и 25, истоки с седьмого по десятый р-транзисторов 18-21 соединены со стоками пятнадцатого и шестнадцатого р-транзисторов 26 и 27, исток первого п-транзистора 7 соединен со стоками третьего и четвертого п-транзисторов 9. и 10, исток третьего п-транзистора 9 соединен со стоками пятого, восьмого и девятого п-транзисторов 28,31,32, истоки второго и четвертого п-транзисторов 8 и 10 соединены со стоками шестого, седьмого и одиннадцатого п-транзисторов 29, 30 и 34, истоки пятого и шестого п-транзисторов 28 и 29 соединены со стоками .девятого п-транзистора 33, исток которого соединен с истоком девятого п-транзистора 32 и стоками тринадцатого и пятнадцатого п-транзисторов 36 и 38, истоки седьмого и восьмого п-транзисторов 30 и 31 соединены со стоками двенадцатого п-транзистора 35, исток которого соединен с истоком одиннадцатого п-транзистора 34 и со стоком четырнадцатого п-транзистора 37, исток которого соединен с истоком тринадцатого И -транзистора 36 и

р-транзистора 21, шестого п-транзйс- тора 29 и восьмого п-транзистора 31, шина 45 соединена с затворами восьмого р-транзистора 19, двенадцатого р-транзистора 23, пятого п-транзистора 28 и седьмого п-транзистора 30, шина 46 соединена с затворами второго р-транзистора 2 и четырнадцатого

п-транзистора 37, шина 47 соединена с затворами .четвертого р-транзистора 4 и тринадцатого п-транзистора 36, истоки с первого по четвертый р-тран- зисторов 1-4 соединены с шиной 16

питания, истоки пятнадцатого и шестнадцатого п-транзисторов 38 и 39 соединены с общей шиной 17, истоки с тринадцатого по шестнадцатый р-тран- зисторов 24-27, стоки первого и втос выходной шиной 15 результата, сто, ки первого и второго р-транзисторов 1 и 2 соединены со стоками с пятого по восьмой р-транзисторов 5,6,18 и 19, стоки третьего и четвертого р- транзисторов 3 и 4 соединены со стоками с девятого по двенадцатый р- транзисторов 20...23, истоки пятого, шестого, одиннадцатого и двенадцато5

0

5

0

5

со стоками тринадцатого и четырнадцатого р-транзисторов 24 и 25, истоки с седьмого по десятый р-транзисторов 18-21 соединены со стоками пятнадцатого и шестнадцатого р-транзисторов 26 и 27, исток первого п-транзистора 7 соединен со стоками третьего и четвертого п-транзисторов 9. и 10, исток третьего п-транзистора 9 соединен со стоками пятого, восьмого и девятого п-транзисторов 28,31,32, истоки второго и четвертого п-транзисторов 8 и 10 соединены со стоками шестого, седьмого и одиннадцатого п-транзисторов 29, 30 и 34, истоки пятого и шестого п-транзисторов 28 и 29 соединены со стоками .девятого п-транзистора 33, исток которого соединен с истоком девятого п-транзистора 32 и стоками тринадцатого и пятнадцатого п-транзисторов 36 и 38, истоки седьмого и восьмого п-транзисторов 30 и 31 соединены со стоками двенадцатого п-транзистора 35, исток которого соединен с истоком одиннадцатого п-транзистора 34 и со стоком четырнадцатого п-транзистора 37, исток которого соединен с истоком тринадцатого И -транзистора 36 и

стоком шестнадцатого п - транзистора 39..

Устройство работает следующим образом.

На шины 11,12, 40-43 поступают нулевой - второй разряды первого операнда, на шины 13,14, 44-47 поступают нулевой - второй разряды второго операнда.

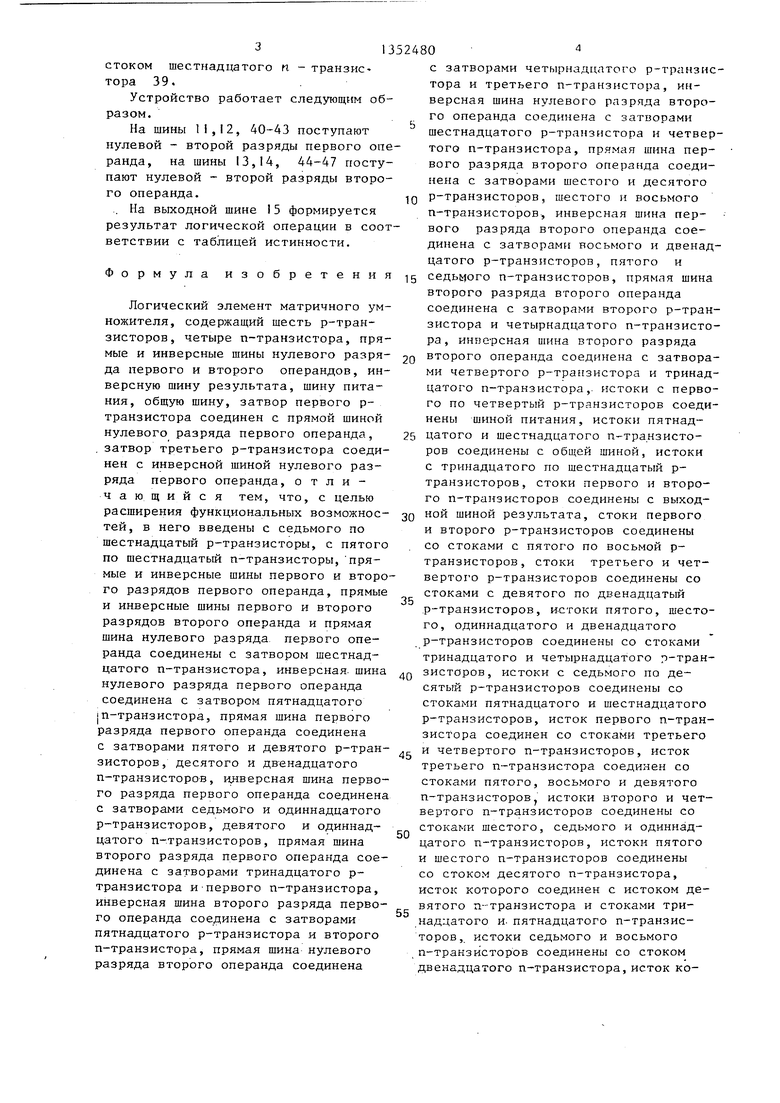

. На выходной шине 15 формируется результат логической операции в соответствии с таблицей истинности.

Формула изобретения

Логический элемент матричного умножителя, содержащий шесть р-тран- зисторов, четыре п-транзистора, прямые и инверсные шины нулевого разряда первого и второго операндов, инверсную шину результата, шину питания, общую шину, затвор первого р- транзистора соединен с прямой шиной нулевого разряда первого операнда, , затвор третьего р-транзистора соединен с инверсной шиной нулевого разряда первого операнда, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены с седьмого по шестнадцатый р-транзисторы, с пятого по шестнадцатый п-транзисторы, прямые и инверсные шины первого и второго разрядов первого операнда, прямые и инверсные шины первого и второго разрядов второго операнда и прямая шина нулевого разряда первого операнда соединены с затвором шестнадцатого п-транзистора, инверсная, шина нулевого разряда первого операнда соединена с затвором пятнадцатого jп-транзистора, прямая шина первого разряда первого операнда соединена с затворами пятого и девятого р-тран- зисторов, десятого и двенадцатого п-транзисторов, инверсная шина первого разряда первого операнда соединена с затворами седьмого и одиннадцатого р-транзисторов, девятого и одиннадцатого п-транзисторов, прямая шина второго разряда первого операнда соединена с затворами тринадцатого р- транзистора и-первого п-транзистора, инверсная шина второго разряда первого операнда соединена с затворами пятнадцатого р-транзистора и второго п-транзистора, прямая шина нулевого разряда второго операнда соединена

13

52480 с

10

15

20

25

30

35

40

45

50

55

затворами четырнадцатого р-транзистора и третьего п-транзистора, инверсная шина нулевого разряда второго операнда соединена с затворами шестнадцатого р-транзистора и четвертого п-транзистора, прямая шина первого разряда второго операнда соединена с затворами шестого и десятого р-транзисторов, шестого и восьмого п-транзисторов, инверсная шина первого разряда второго операнда соединена с затворами восьмого и двенадцатого р-транзисторов, пятого и седьмого п-транзисторов, прямая шина второго разряда второго операнда соединена с затворами второго р-транзистора и четырнадцатого п-транзистора, иние-рсная шина второго разряда второго операнда соединена с затворами четвертого р-транзистора и тринадцатого п-транзистора,. истоки с первого по четвертый р-транзисторов соединены шиной питания, истоки пятнадцатого и шестнадцатого п-транзисторов соединены с общей шиной, истоки с тринадцатого по шестнадцатый р- транзисторов, стоки первого и второго п-транзисторов соединены с выходной шиной результата, стоки первого и второго р-транзисторов соединены со стоками с пятого по восьмой р- транзисторов, стоки третьего и четвертого р-транзисторов соединены со стоками с девятого по двенадцатый р-транзисторов, истоки пятого, шестого, одиннадцатого и двенадцатого р-транзисторов соединены со стоками тринадцатого и четырнадцатого р-транзисторов, истоки с седьмого по десятый р-транзисторов соединены со стоками пятнадцатого и шестнадцатого р-транзисторов, исток первого п-тран- зистора соединен со стоками третьего и четвертого п-транзисторов, исток третьего п-транзистора соединен со стоками пятого, восьмого и девятого п-транзисторов, истоки второго и четвертого п-транзисторов соединены со стоками шестого, седьмого и одиннадцатого п-транзисторов, истоки пятого и шестого п-транзисторов соединены со стоком десятого п-транзистора, исток которого соединен с истоком девятого п-транзистора и стоками тринадцатого и. пятнадцатого п-транзисторов, истоки седьмого и восьмого п-транзйсторов соединены со стоком двенадцатого п-транзистора, исток ко 13524806

торого соединен с истоком одиннадцато- с оединен с истоком тринадцатого п- го п-транзистора и со стокомчетырнад- транзистора и стоком шестнадцатого цатогоп-транзистора, исток которого п-транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1989 |

|

SU1640684A1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

Изобретение относится к области импульсной техники и может быть использовано при построении аппаратной части умножителей двоичньгх чисел. Логический элемент матричного умножителя содержит р-транзисторы, п-тран- зисторы, прямую и инверсную шины (Ш) нулевого разряда (Р) первого операнда, прямую и инверсную Ш нулевого Р второго операнда, инверстную Ш результата, Ш питания, общую Ш, прямую и инверсную Ш первого Р первого операнда, прямую и инверсную Ш, второго Р первого операнда, прямую.и инверсную Ш первого Р второго операнда, прямую и-инверсную Ш второго Р второго операнда. Изобретение расширяет функциональные возможности путем увеличения разрядности операндов. 1 ил. 1 табл. 00 СД ю

| Одноразрядный сумматор | 1983 |

|

SU1117634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № | |||

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-01-10—Подача