(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля функционирования блоков ЭВМ в процессе их работы. Целью изобретения является упрощение устройства. С этой целью в устройство, содержащее генератор тестов, блок постоянной памяти, схему сравнения, блок задания режима и блок индикации, введены вторая схема сравнения, счетчик, три триггера, два элемента ИЛИ, элемент И, элемент запрета и сигнатурный анализатор. 1 ил. I

Изобретение относится к вычислительной технике и может быть использовано для контроля функционирования блоков ЭВМ в процессе их работы.

Целью изобретения является упрощение устройства.

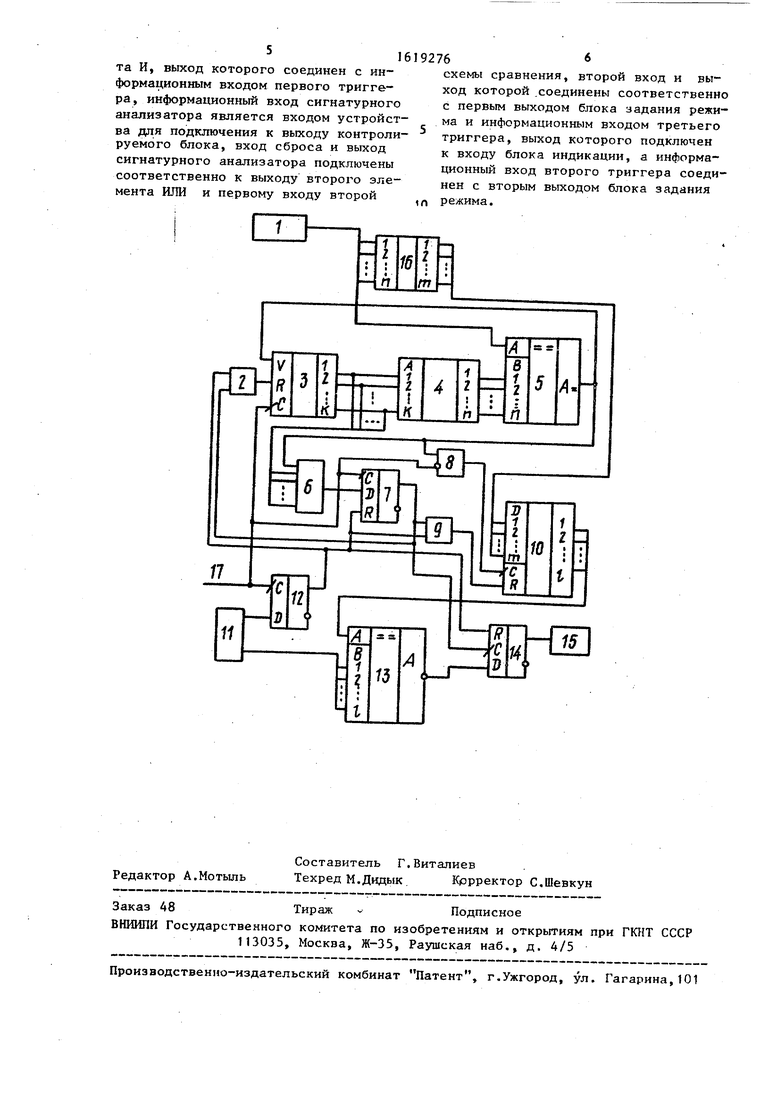

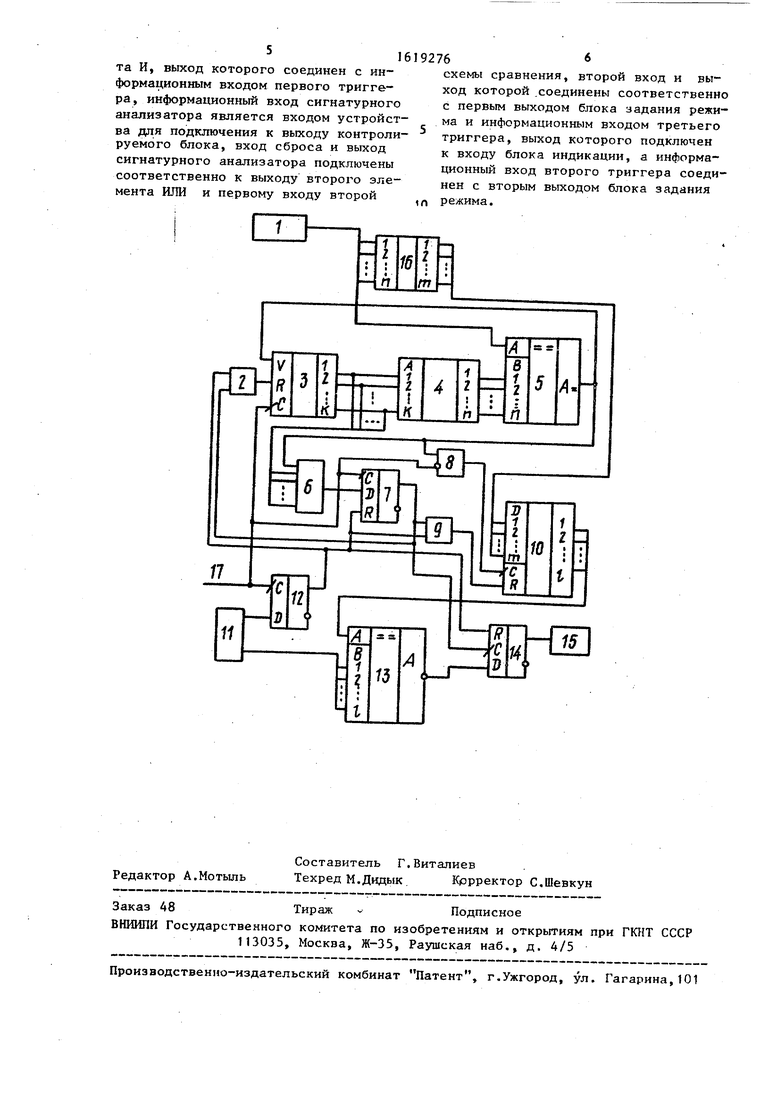

На чертеже представлена функциональная схема устройства.

Устройство содержит генератор 1 тестов, первый элемент ИЛИ 2, счетчик 3, блок 4 постоянной памяти, первую схему 5 сравнения, элемент И 6, первый триггер 7, элемент 8 запрета, второй элемент ИЛИ 9, сигнатурный анализатор 10, блок 11 задания режима, второй триггер 12, вторую схему 13 сравнения, третий триггер 14, блок 15 индикации, контролируемый блок 15, тактовый вход 17. В качестве генератора 1 тестов могут быть использованы технические средства той же ЭВМ, в состав которой входит контролируемый блок 16. В этом случае выход контролируемого блока 16 должен быть соединен с входами соответ- ,|ствующих блоков ЭВМ, а тактовый вход I7 - с тактовой шиной ЭВМ (не показано).

Устройство работает следующим образом.

Сигнал Сброс с выхода блока 1 задания режима поступает на информационный вход триггера 12, на выходе которого формируется импульс, начат яо и конец которого синхронны с передним фронтом тактовых импульсов, поступающих по шине 17. Выходной сигнал триггера 12 устанавливает в исходное нулевое состояние триггеры 7 и 14, счетчик 3 и сигнатурный знализатор 10. При этом в следующем такте на вход схемы 5 сравнения поступа-| ет содержимое ячейки с нулевым адресом блока 4 памяти. Схема 5 сравнения сравнивает входной набор контро4- лируемого блока 16 и поступившее содержимое блока 4 памяти. Если наборы различаются, то состояния счетчика 3, сигнатурного анализатора 10 и триггеров 7 и 14 не меняются. При совпадении входного набора с текущим содержимым блока 4 памяти на выходе схемы 5 сравнения появляется единичный сигнал, элемент 8 запрета во второй половине такта открывается и на синхровход сигнатурного анализатора 10 поступает импульс, в результате чего ана изатор 10 переходит в следующее состояние, определяемое текущим состоянием и выходным набором контролируемого блока 16. Одновременно выходной сигнал схемы 5 сравнения поступает на вход разрешения счета счетчика 3, который в начале следующего такта увеличивает свое содержимое на единицу.

На вход схемы 5 сравнения поступает содержимое новой ячейки блока 4 памяти, так что в новом такте схе- ма 5 сравнения сравнивает входной набор с новым содержимым блока 4 памяти. Состояния триггеров 7 и 14 не меняются до тех пор, пока элемент И 6 остается закрытым. Этот элемент открывается при условии,что все разрязные выходы счетчика 3 принимают единичное состояние, а входной набор контролируемого блока 16 совпадает с содержимым бпока 4 памяти. При этом на выходе триггера 7 в следующем такте появляется единичный сигнал. Во второй половине текущего такта сигнатурный анализатор 10 переходит в свое последнее состояние, которое сравнивается с помощью схемы 13 сравнения с эталоном, поступающим с блоХа 11 задания режима. Если коды совпадают, то па выходе схемы 13 сравнения появляется уровень логического нуля, в результате чего триггер 14 остается в нулевом состоявши. Если же коды не совпадают, то на выходе схемы 13 сравнения появляется единичный сигнал. При этом в начале следующего такта триггер 14 переходит в единичное состояние, что свидетельствует о неисправности контролируемого блока 16. Состояние триггера 14

0

5

0

5

0

5

0

5

0

5

индицируется блоком 15. Единичный сигнал с выхода триггера 7 устанавливает в исходное состояние счетчик 3 и сигнатурный анализатор 10. При этом на выходе элемента И 6 появляется уровень логического нуля, так что в следуюшем такте возвращается в исходное состояние и триггер 7. На этом один цикл проверки контролируемого блока 16 заканчивается и начинается новый цикл. Если несовпадение фактической и эталонной сигнатур было случайным, то триггер 14 после окончания следующего цикла возвратится в нулевое состояние. Если же контролируемый блок 16 неисправен, то триггер 14 остается в единичном состоянии.

Формула изобретения

Устройство для оперативного контроля цифровых блоков, содержащее генератор тестов, блок постоянной памяти, первую схему сравнения, блок задания режима и блок индикации, отличающееся тем, что, с целью упрощения устройства, оно содержит вторую схему сравнения, счетчик, три триггера, два элемента ИЛИ, элемент И, элемент запрета и сигнатурный анализатор, причем первый вход первой схемы сравнения является входом устройства для подключения к выходу генератора тестов и входу контролируемого блока, выход блока постоянной памяти соединен с вторым входом первой схемы сравнения, выход которой подключен к входу управления счетом счетчика, первому входу элемента И и прямому входу элемента запрета, выход которого соединен с синхровходом сигнатурного анализатора, синхровходы первого и второго триггеров и счетчика и инверсный вход элемента запрета подключены к тактовому входу устройства, выход первого триггера соединен с первыми входами первого и второго элементов ИЛИ и синхровходом третьего триггера, выход второго триггера подключен к вторым входам первого и второго элементов ИЛИ и входам сброса первого и и третьего триггеров, выход первого элемента ИЛИ соединен с входом сброса счетчика, выход которого подключен к адресному входу блока постоянной памяти и второму входу элемен516

та И, выход которого соединен с информационным входом первого триггера, информационный вход сигнатурного анализатора является входом устройства для подключения к выходу контролируемого блока, вход сброса и выход сигнатурного анализатора подключены соответственно к выходу второго элемента ИЛИ и первому входу второй

92766

схемы сравнения, второй вход и выход которой соединены соответственно с первым выходом блока задания режима и информационным входом третьего триггера, выход которого подключен к входу блока индикации, а информационный вход второго триггера соединен с вторым выходом блока задания ,л режима.

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| - М.: Мир, 1972, рис.12.1 | |||

| Устройство для контроля логических блоков | 1984 |

|

SU1166119A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-06-01—Подача