Изобретение относится к вычислительной технике и может быть использовано в специализированных IBM, а также при разработке вычислительных устройств, изготовляемых в составе больших интегральных сгем.

Цель изобретения - расширение области изменения аргумента дня целочисленных (как положительных, так и отрицательных) степеней при одновременном сокращении объема памяти.

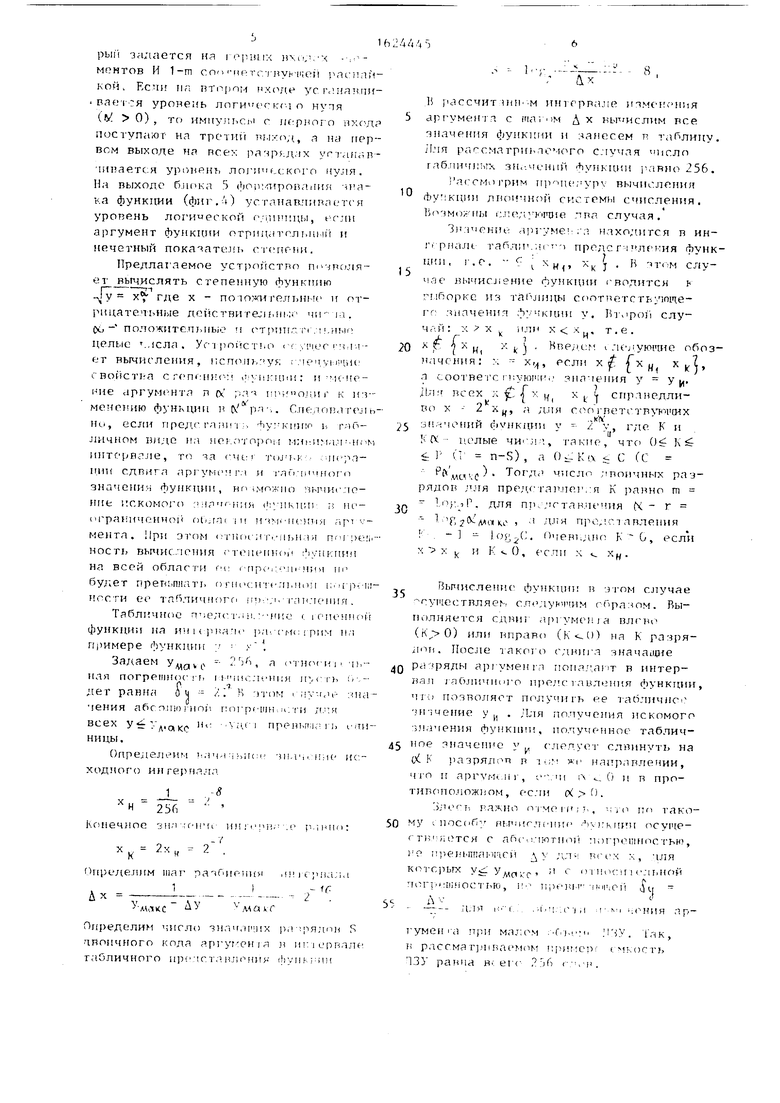

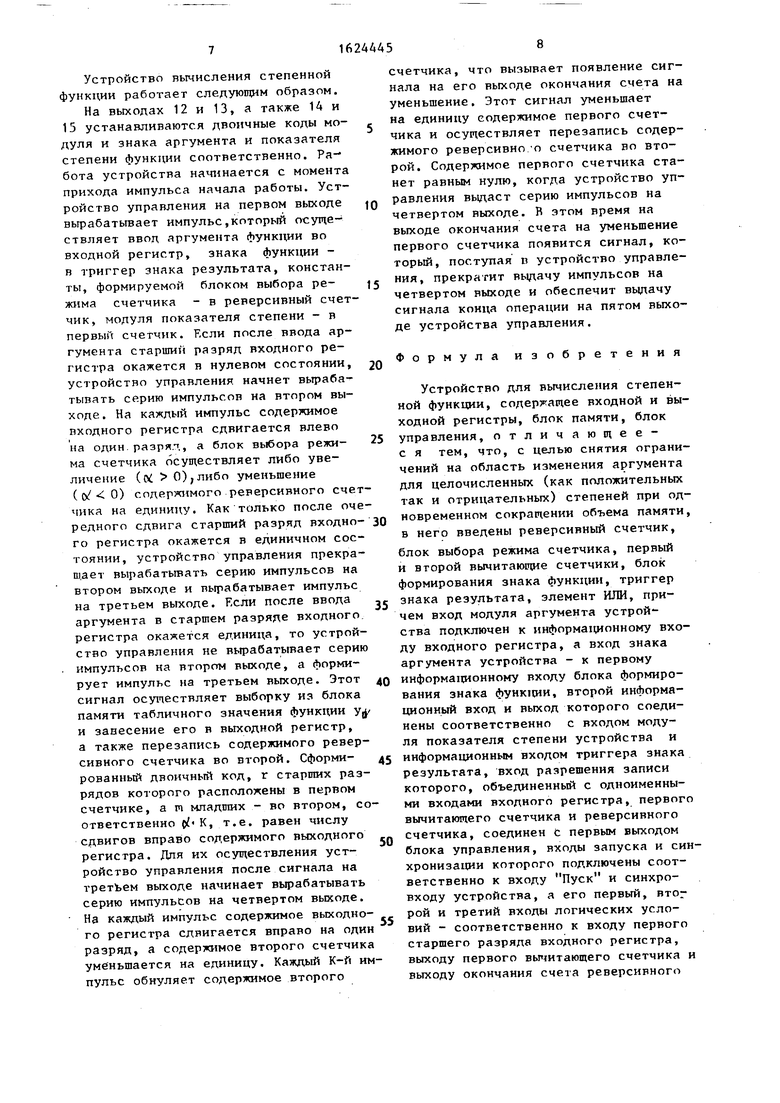

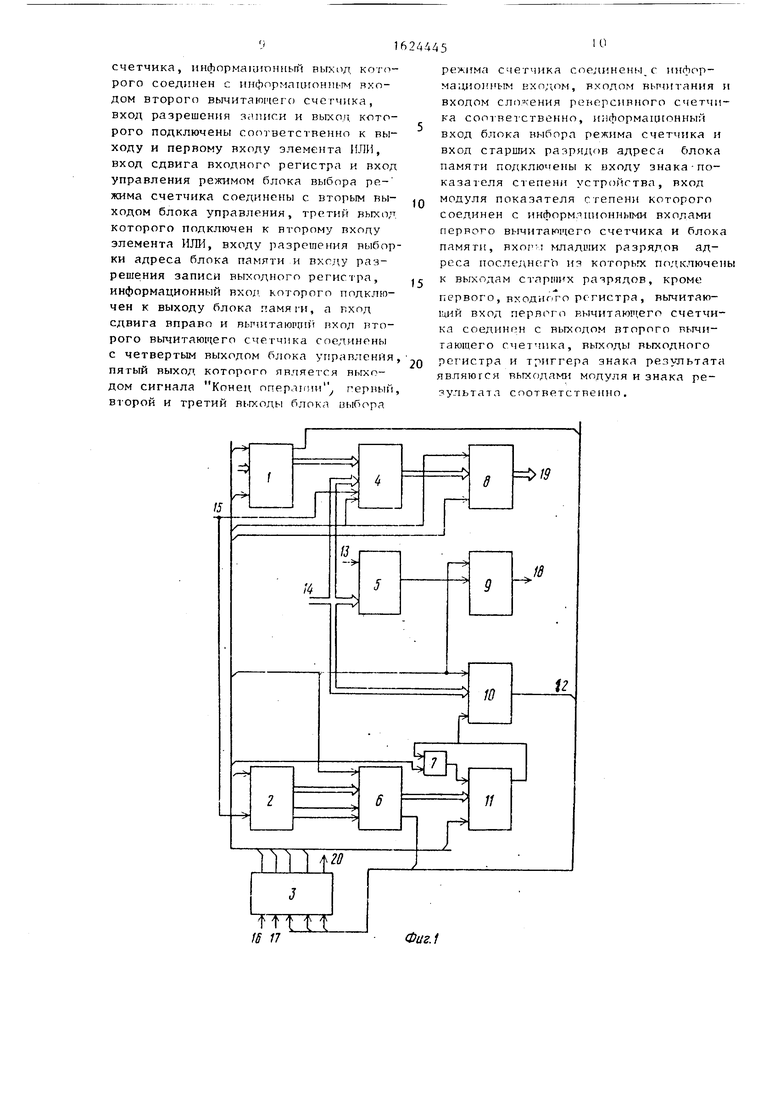

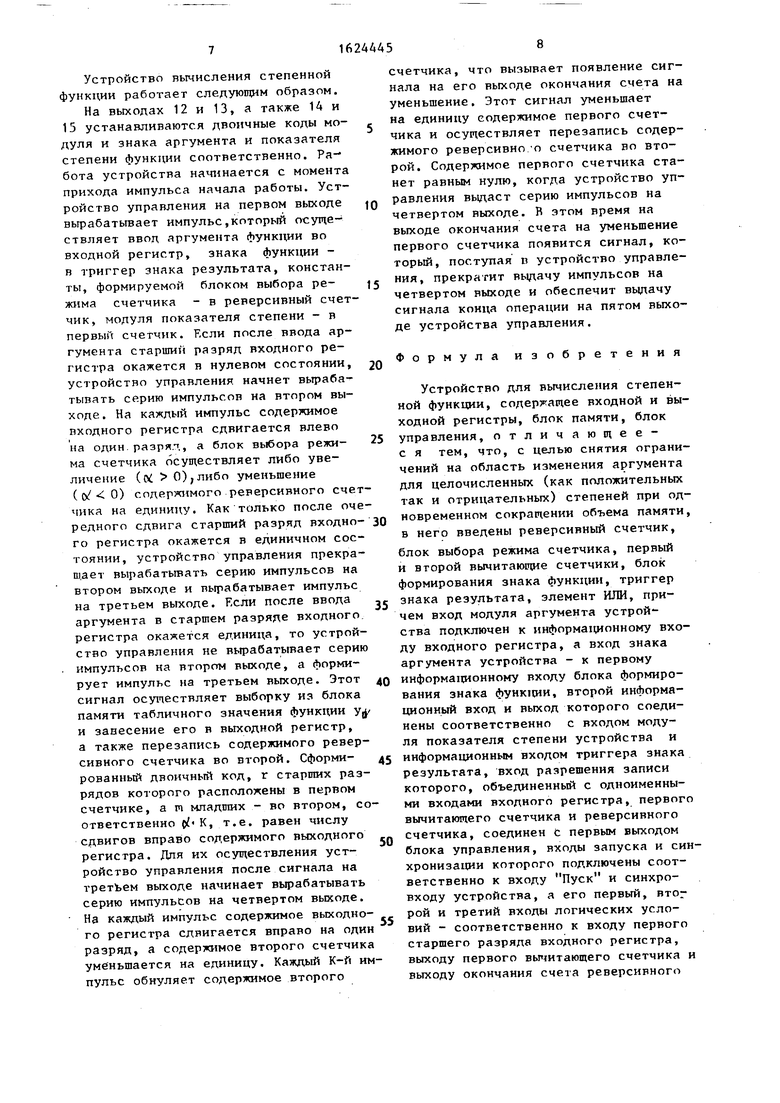

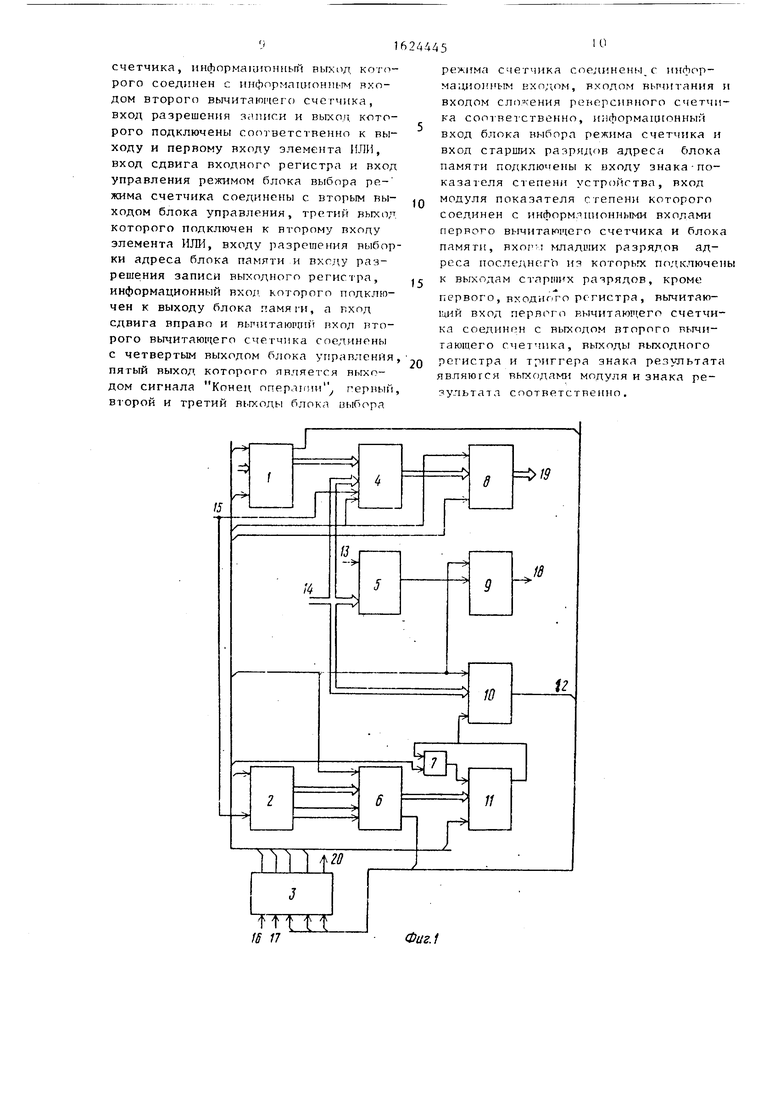

На фиг. 1 представлена Лч-икцио- нальная схема предлагаемо о устройства для вычисления степенной функции} на фиг. 2 - вариант реализации устройства управления; на Лиг. i - вариант

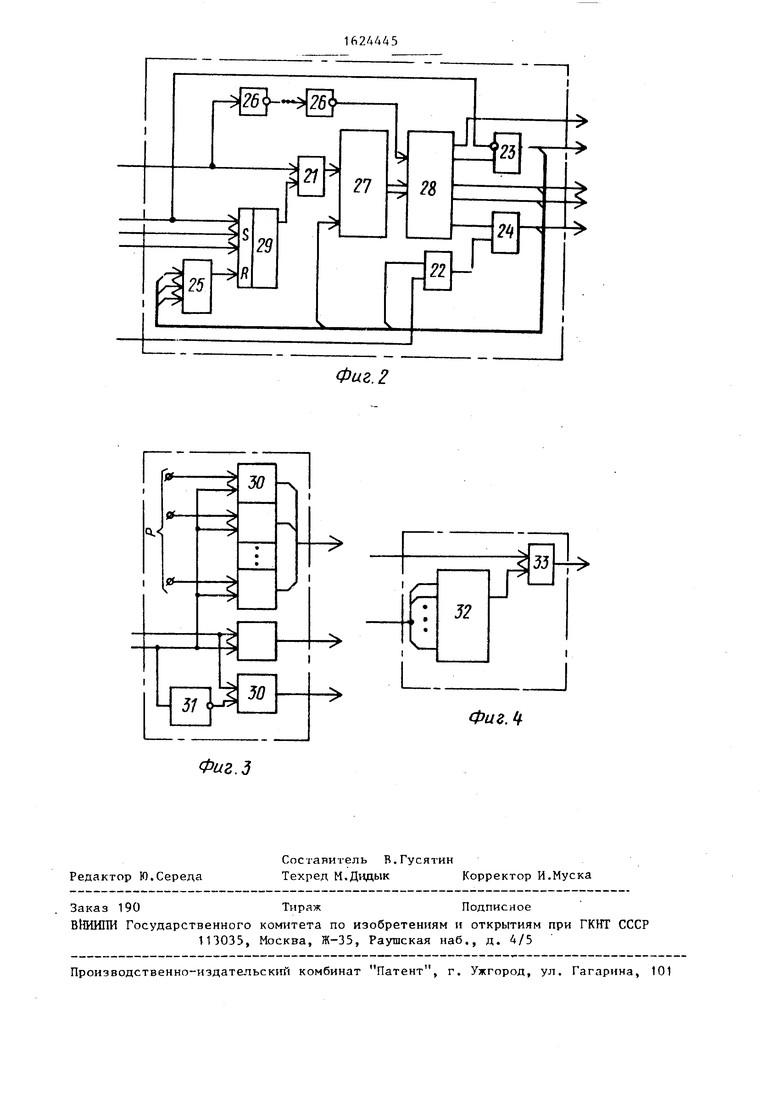

реализации блока выбора режима счетчика; на фиг. 4 - то же, блока формирования знака функции.

Устройство содержит (фиг.1) входной регистр 1, блок выбора режима счетчика, блок 3 управления, блок 4 памяти (ПЗУ) , блок 5 сформирования знака функции, реверсивный счетчик 6, элемент ИЛИ 7, втоднон регистр 8, триггер 9 знака результата, первый 10 и второй 11 вычитающие счетчики, входы 12 и 13 соответственно модуля и знака аргумента устрппсгы1, входы 14 и 15 соответственно моду IR и знака показателя , гг.-ип 16 Пуск, синхровход 17, 18 чнаЕ 4

05

ю

ел

ка результата, выход 19 модуля результата и выход 70 конца операции. Элементы устройства могут быть реализованы на основе стандартных микро- , схем.

Блок 3 управления (фиг.2) содержит элементы И 21-23, элементы ИЛИ 24 и 25, элементы НЕ 26, счетчик 27, дешифратор 28, триггер 29, блок 2 вы- ю бора режима счетчика содержит элементы И 30,, -30, элемент НЕ 31.

Устройство управления работает следующим образом.

Счетчик 27 имеет пять состояний, с 15 помощью дешифратора 28 каждому состоянию поставлен в соответствие по номерам выход устройства управления. В исходном состоянии содержимое счетчика равно нулю и оно не дешифрирует- 20 ся. Из состояния в состояние счетчик переводится синхроимпульсами, поступающими на второй вход устройства управления. Сменой состояний счетчика управляет триггер 29 и элемент И 21. 25 Синхроимпульсы поступают также на первый разрешающий вход дешифратора через цепочку элементов НЕ, которая обеспечивает зацер ку импульса на время окончания переходных процессов в 0 счетчике .Устройство управления начинает работу с момента прихода на его первый вход импульса начала работы Пуск, этот сигнал устанавливает триггер 29 в единичное состояние.Первый синхроимпульс установит счетчик в первое состояние. Этот же импульс поступит на разрешающий вход дешиЛ- ратора и на его первом выходе,так же как и на первом выходе устройства .Q управления, появится импульс.

Второй синхроимпульс переводит счетчик во второе состояние. Если при этом на третьем входе устройства управления установлен уровень дс логической единицы, т.е. старший разряд входного регистра находится в единичном состоянии, то элемент И 23 по второму входу будет заперт и на втором выходе устройства управле- ,Q ния импульс будет отсутствовать, а третий синхроимпульс переведет счетчик в третье состояние. В противном случае элемент И 23 будет открыт и первый же импульс с его выхода установит триггер 9 в нулевое состояние. Это приводит к тому, что второе состояние счетчика не будет изменяться следующими синхроимпульсами до тех

пор, пока на третьем входе устройства управления не появится уровень логической единицы. В течение времени, когда счетчик будет находиться во втором состоянии, устройство управления на втором выходе будет вырабатывать серию импульсов. Уровень логической единицы на третьем входе устройства управления установит триггер 24 в единичное состояние, а очередной синхроимпульс переведет счетчик п третье состояние и на третьем выходе дешифратора и третьем выходе устройства управления появится импульс. Этот же импульс поступает на первый вход элемента И 22, если на втором входе этого элемента присутствует уровень логической единицы, когда содержимое первого счетчика равно нулю, на выходе элемента ИЛИ 24 и на пятом выходе устройства управления вырабатывается сигнал конца операции. Этот сигнал устанавливается в нулевое состояние триггер 29 и счетчик 27. Если это не происходит, го очере шой синхроимпульс переведет счетчик в четвертое состояние. Первый же импучьс с четвертого выхода устройств управления установит триггер в нуп°в,е состояние, это приведет к тому, то ртвертое состояние счетчика не будя г изменяться с поДУЮЩИМИ синхроимпульсами до тех пор, пока на четвертом входе vcтройства управления не появится уровень погической единицы, когда содержимое первого счетчика станет равным нулю. В течение времени, когда счетчик будет находиться в четвертом состоянии, устройство управления будет вырабатывать серию ИМПУЛЬСОВ на че вертом выходе. Уровень логической единицы на четвертом входе устройства управления установит триггер в единичное состояние, а очередной синхроимпульс переведет счетчик в пятое состояние. На пятом выходе устройства управления появится сигнал конца операции.

Принцип работы бтока выбора режима счетчика (фиг. 3s состоит в том, что на перрмй вход поступает импульс, а на второй вход - знак покачатепя степени функции. Гели на втором входе устанавливается уроне нь логической единицы С (X 0) , то импульсы с первого вхола поступают нт второй выход, а на первом выходе появпяется тп-раз- рчдный двоичный код чистя Р, которык задается ня i ерш , ментов И 1-m сомните i nvMueit pai JT ы- коч, Есчи и, втором iwpjre усьмачпи- - вар i я уровень (V 0), то имттьоы г шрного т-ота поступаю нл третий яи- од, а цс) пер- вгм выходе на псе-- разр;д)х vriah,B- ынаегся уровень noi in f i KOI о нудя. На выходе бпоьа 5 Ьоп тфовалия ira- va функции (фи .) }сганавчива т я уровень логической t нпч цы, есчи аргумент Функции отрицапглььни и нечетный показатель сюит ни.

Предлагаемое устройство гн шочя- ei вычислять степенную Лунышю

-ГМ

-J v х, где х - по ЮЧГИГРПЬНМО и от- рпдатечьные доистви гелып,. чи п.

(X,-4 ПОЛО ЧИТСПЬИЫ Ч ОТрИП ii I

целые т 1сла . Yi i ронс р о I пег i i i от вычисления, ьспоп у« , i. воисп-а с гсп HI ( « мчипп: и ч не- иие аргумоша п fx , м HI i и мечопию функции в &. ) i . Гиг ioraieir HU, если лред ia/пм f мчго i г наличном ви ic HI че uopoit tint им i i н NJ пнтг рвгле, т т ч t i i iu i i IK , i - пин сдвига api vNi1 i и 1лч ичного значени i Лункции, нп (молмо мчш ieHHfc I CKOHOl О 1Я if h lii ( Hbll II i Hi orpai нченнон о1мт ii и SM. IK ipi мента. При этом nun им ы п i tr. носгь вычис сния leneniioi HI пич на всей области г i i rip IK чих IIP будет прев; niLiT ь омкчн п но i i ip i нес И ее тг.бтичи г ri ч i IB lennri

Табличное т сл i ни.1 iriuniion функции нл ич i ( ia i примере fbvHKiuin

1 ( М( I РИ I Н 1 (

Г)Ь , а см но( HI р

I I IIU I HI,Я 1Г ( I }

/ .9 Ь лог; . i,u

ч i i 1

на ГО Г) IIIH i I Н Д Я

1 a i i прет п i i i t TH)М 1

I 1(J M

Л- - ,

2Ь6 н i f iru ин i i

,HH.

хч

- 2

Определим таг пачОт ния Ах- 1

2

млкс у хмияг Определим число ян .ч IP их ра ря юв S Типичного (ода apiyrenia ч in lepmif табличного up in влепив ().пь и (

1

их

8

В раосчит inn м ин7грва,е ч ння api VMeniT с ina i м Д х ыг ислим все значения функнин и занесем Р таблицу. Лчя рчг-смагриьтемого с исло

Пбпич i X 31Ь Ч1.НПИ ПУНКЦИИ 1ВЯО 256.

i Morpnv p вычисления rbv кции д1нч чнои системы счисления. Ьо JMO/- ны i го и H TOse ва случая .

3) j lOhiu ни уме1 н 1Ходнтся в ин15

2Q

т i. ooi не i г 11 ЮР с. чна it-нил у у . /1 i BI. ex , Ј Г ( t ij спр янедливо х 2 л,., а Д|1я ссчч пет i i (их

- ,tffti,

зернении оч нкцип у - / , где К и

Л редые 4H j , ьчкиг, что 0 К t ( n-S) , а О- К ь С (С.

ft ,

, ). Тогда

«пело

0

via с |1-л 1ВОИЧНЫХ paj- рядов 7 1я пред( laiTiier л К равно гп , if. для пп ставн чия ( - г

OHU1 И Про/ Т 1ПТРННЯ

io(j( . (чев ,I.HO р О, если

О , f С п и ч X н .

1

v - k И Р

-)

Вьпшслечис ф нкции в з i ом случае гвляег сгчмуьччим . Вы- иопняется сдви ia вл во () ипи вправо ( на К разрядов. После iaKoio IBIII т значаиц-ге Q ра «ряды apivMemi попа глпт в интер- вяп i пОлично о i тления ф нкции, 41 ) позволяет подучи ib je таочичнс ui Celine у ( . Лля no4V4ei nn искомого чучения Лункппи, помученное таблич- 5 НОР значение уv cuensei СДВИНУТЬ на (Ј Ь разряд IB в i i награвпении, 4JO н aprvfitiii, ч л о ц в про- i ивгпто(ОЖ1 он, ест о( О .

им т j члно оi моiн , о го iаь о- 0 МУ тсоб Hinuir ii иге ч) ьнни (icvrie- i ) i / с абс ютнои ч,н ргппос i ьн, in i,iei im ai )цси л ,т ь t , HI я кот грьгч .-умс1кГ, a i (многим F.HOH

Ч14 i i ШМОС I ЬЮ , IIi,U I г II И СП j (.1

,(

-а

I 7 Я

С НИ Я

р

i умен i а чрн M. f j м -Л . 1 а, ь р юсмя i пьаеном i (, 13i раина нем jfi н.

Устройство вычисления степенной функции работает следующим образом. На выходах 12 и 13, а также 14 и 15 устанавливаются двоичные коды мо- дуля и знака аргумента и показателя степени функции соответственно. Работа устройства начинается с момента прихода импульса начала работы. Устройство управления на первом выходе вырабатывает импульс,который осуществляет ввод аргумента функции во входной регистр, знака функции - в триггер знака результата, константы, формируемой блоком выбора ре- жима счетчика - в реверсивный счетчик, модуля показателя степени - в первый счетчик. Если после ввода аргумента старший разряд входного регистра окажется в нулевом состоянии, устройство управления начнет вырабатывать серию импульсов на втором выходе. На каждый импульс содержимое входного регистра сдвигается влево на один разряд, а блок выбора режи- ма счетчика осуществляет либо увеличение (& 0),либо уменьшение ( О/ «С 0) содержимого реверсивного счетчика на единицу. Как только после очередного сдвига старший разряд входно- го регистра окажется в единичном состоянии, устройство управления прекра- шает вырабатывать серию импульсов на втором выходе и вырабатывает импульс на третьем выходе. Если после ввода аргумента в старшем разряде входного регистра окажется единица, то устройство управления не вырабатывает серию импульсов на втором выходе, а формирует импульс на третьем выходе. Этот сигнал осуществляет выборку из блока памяти табличного значения функции у, и занесение его в выходной регистр, а также перезапись содержимого реверсивного счетчика во второй. Сформи- рованный двоичный код, г старших разрядов которого расположены в первом счетчике, a m младщих - во втором, соответственно К, т.е. равен числу сдвигов вправо содержимого выходного регистра. Для их осуществления устройство управления после сигнала на третьем выходе начинает вырабатывать серию импульсов на четвертом выходе. На каждый импульс содержимое выходного регистра сдвигается вправо на один разряд, а содержимое второго счетчика уменьшается на единицу. Каждый К-й импульс обнуляет содержимое второго

5 0 5 0 - о 5

5

счетчика, что вызывает появление сигнала на его выходе окончания счета на уменьшение. Этот сигнал уменьшает на единицу содержимое первого счетчика и осуществляет перезапись содержимого реверсивно о счетчика во второй. Содержимое первого счетчика станет равным нулю, когда устройство управления выдаст серию импульсов на четвертом выходе. В этом время на выходе окончания счета на уменьшение первого счетчика появится сигнал, который, поступая п устройство управления, прекратит выдачу импульсов на четвертом выходе и обеспечит выдачу сигнала конца операции на пятом выходе устройства управления.

Формула изобретения

Устройство для вычисления степенной функции, содержащее входной и выходной регистры, блок памяти, блок управления, отличающее- с я тем, что, с целью снятия ограничений на область изменения аргумента для целочисленных (как положительных так и отрицательных) степеней при одновременном сокращении объема памяти, в негр введены реверсивный счетчик,

блок выбора режима счетчика, первый и второй вычитающие счетчики, блок формирования знака функции, триггер знака результата, элемент ИЛИ, причем вход модуля аргумента устройства подключен к информационному входу входного регистра, а вход знака аргумента устройства - к первому информационному входу блока формирования знака функции, второй информационный вход и выход которого соединены соответственно с входом модуля показателя степени устройства и информационным входом триггера знака результата, вход разрешения записи которого, объединенный с одноименными входами входного регистра, первого вычитающего счетчика и реверсивного счетчика, соединен с первым выходом блока управления, входы запуска и синхронизации которого подключены соответственно к входу Пуск и синхро- входу устройства, а его первый, втог рой и третий входы логических условий - соответственно к входу первого старшего разряда входного регистра, выходу первого вычитающего счетчика и выходу окончания счета реверсивного

- 1

счетчика, информационный выход которого соединен с информационным входом второго вычитающего счегчика, вход разрешения записи и выход, которого подключены соответственно к выходу и первому входу элемента ИЛИ, вход сдвига входного регистра и вход управления режимом блока выбора ре- жима счетчика соединены с вторым выходом блока управления, третий выход которого подключен к второму входу элемента ИЛИ, входу разрешения выборки адреса блока памяти и вхгду разрешения записи выходного регистра, информационный вход которого подключен к выходу блока памяти, а лход сдвига вправо и вьгчитаюрцш вход нто- рого вычитающего счетчика соединены с четвертым выходом блока управления пятый выход которого является выходом сигнала Конец оперлпни, первый второй и третий выходы блока выбора

О

0

5

0

режима счетчика соединены с информационным входом, входом вычитания и входом слежения реверсивного счетчика соответственно, информационный вход блока выбора режима счетчика и вход старших разрядов адреса блока памяти подключены к входу знака-показателя степени устройства, вход модуля показателя степени которого соединен с информационными входами первого вычитающего счетчика и блока памяти, вхорч младших разрядов адреса последнего из которых подключены к выходам старших разрядов, кроме первого, входного регистра, вычитающий вход первого вычитающего счетчика соединен с выходом второго вычитающего счетчика, выходы выходного регистра и триггера знака результата являются выходами модуля и знака результата соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Устройство для воспроизведения функций | 1981 |

|

SU991435A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных ЭВМ, а также при разработке вычислительных устройств, входящих в состав больших интегральных схем. Цель изобретения - расширение области изменения аргумента для целочисленных (как положительных, так и отрицательных) степеней при одновременном сокращении объема памяти. Устройство содержит входной регистр 1, бпок 2 выбора режима счетчика, блок 3 управления, блок 4 памяти, блок 5 формирования знака функции, реверсивный счетчик 6, элемент ИЛИ 7, выходной регистр 8, гер 9 знака результата, вычитающие счетчики 10 и 11 с соответствующими связями. Элементы устройства могут быть реализованы на основе стандартных микросхем. 4 ил. о

f

29

25

Фиг. 2

Г7.

4

30

|4зад

27

28

t

Ы

г-1

|.

ФигЛ

| Устройство для деления | 1985 |

|

SU1285464A1 |

| С, 06 F 7/52, 1985 | |||

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1989-03-15—Подача