Изобретение относится к вычислительной технике и преимущественно может быть использовано для построения аналоговых и гибридных вычислительных машин и цифровых дифференциальных анализаторов, предназначенных для решения краевых задач описываемых уравнением в частных производных.

Целью изобретения является повышение быстродействия и упрощение устройства.

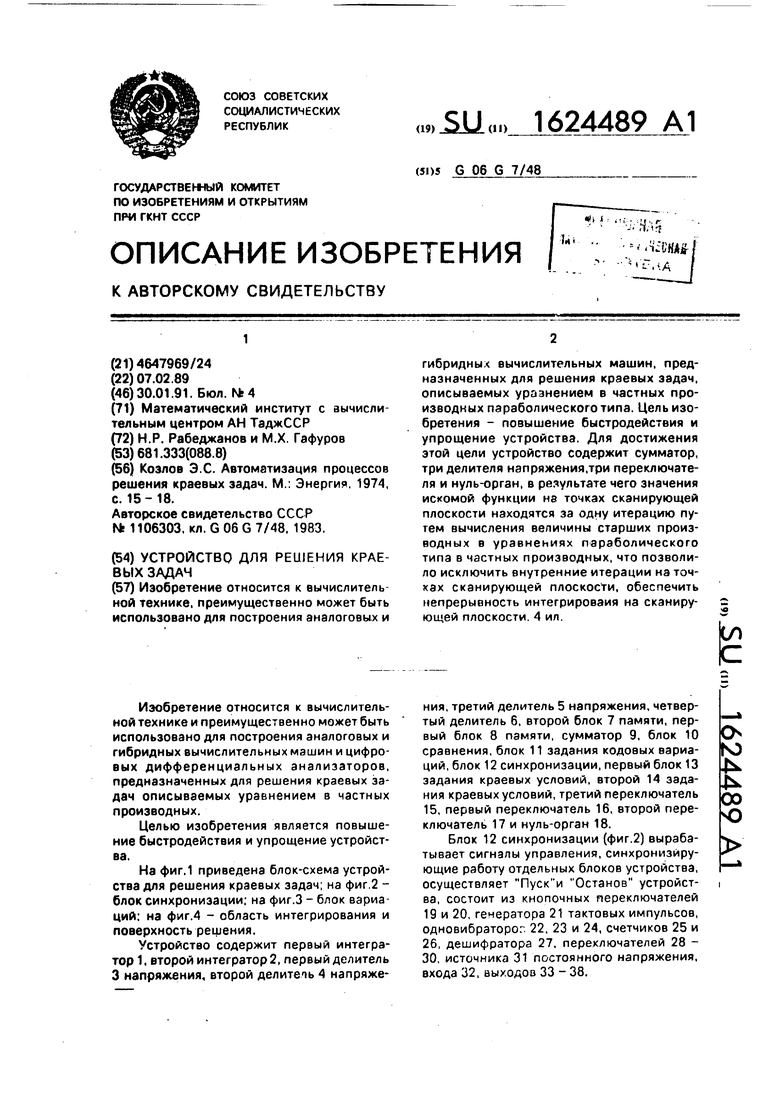

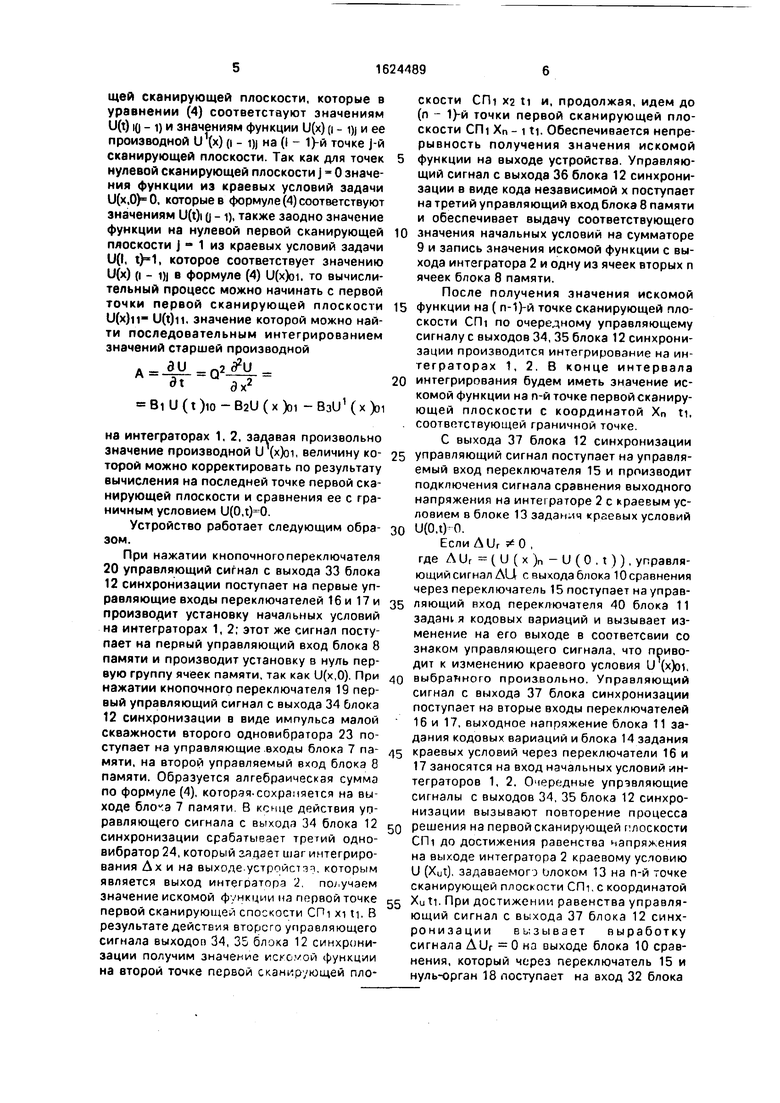

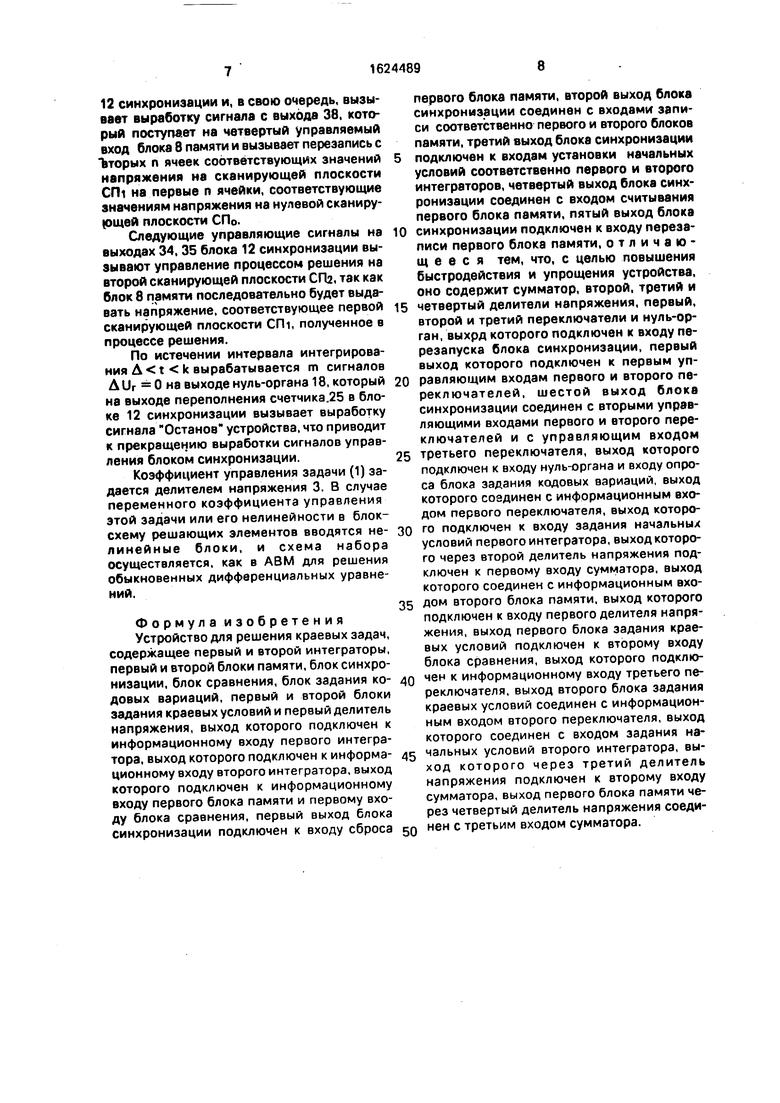

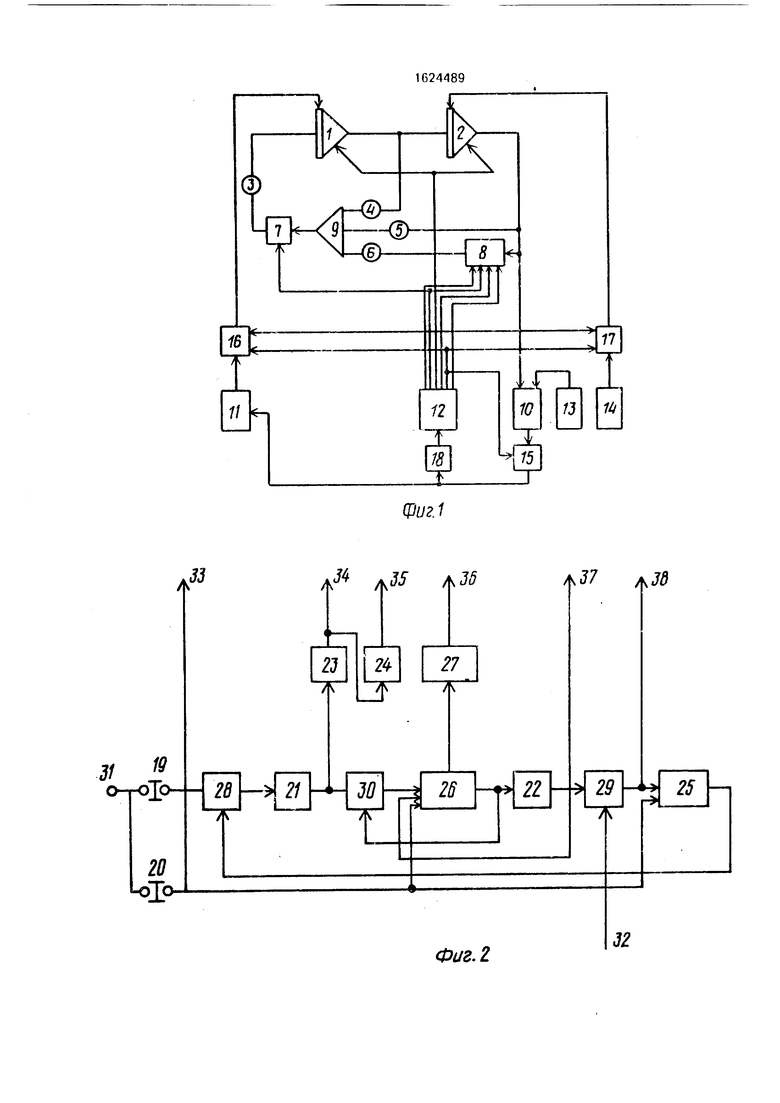

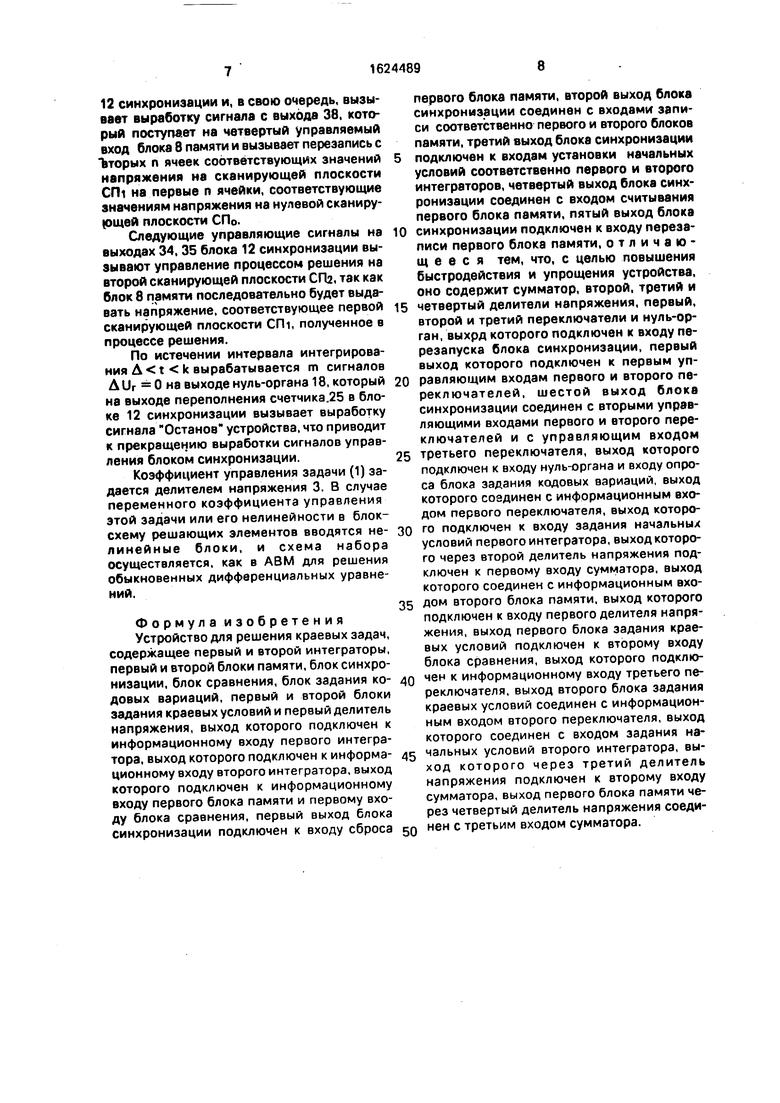

На фиг.1 приведена блок-схема устройства для решения краевых задач; на фиг.2 - блок синхронизации; на фиг.З - блок вариаций: на фиг.4 - область интегрирования и поверхность решения.

Устройство содержит первый интегратор, второй интегратор 2, первый делитель 3 напряжения, второй делитечь 4 напряжения, третий делитель 5 напряжения, четвертый делитель 6, второй блок 7 памяти, первый блок 8 памяти, сумматор 9, блок 10 сравнения, блок 11 задания кодовых вариаций, блок 12 синхронизации, первый блок 13 задания краевых условий, второй 14 задания краевых условий, третий переключатель 15, первый переключатель 16, второй переключатель 17 и нуль-орган 18.

Блок 12 синхронизации (фиг.2) вырабатывает сигналы управления, синхронизирующие работу отдельных блоков устройства, осуществляет Останов устройства, состоит из кнопочных переключателей 19 и 20, генератора 21 тактовых импульсов, одновибраторог. 22, 23 и 24, счетчиков 25 и 26, дешифратора 27, переключателей 28 - 30, источника 31 постоянного напряжения, входа 32, выходов 33 - 38.

и

fc

СО

о

Блок 11 задания кодовых вариаций (фиг.З) состоит из интегратора 39 и переключателя 40. Работа устройства для решения краевых задач уравнений в частных производных параболического типа применительно к решению следующей краевой задачи уравнения теплопроводности:

-Ј- $--оС)

с начальным условием U (х,0)Р и граничными условиями U (0, t) О, U (д) 1 при О х 1иО t Sk.

Задание краевых условий U (1д)1 производится блоком 14 задания краевых условий через переключатель 17, как начальное условие интегратора 2, U (Од)0 -блоком 13 задания краевых сло- вий; начальное условие U (х,0)0 задается блоком 8 памяти; недостающее краевое условие U(x)4-;- -задается блоком 11 через переключатель 16, как начальное условие интегратора 1; блок 10 сравнения производит сравнение искомого решения на границе Од с заданным краевым условием U (0,t) 0 и через переключатель 15 вырабатывает сигналы управления работой блоком 11 задания кодовых вариаций и через нуль-орган 18 - сигнал управления блоком 12 синхронизации; блок 12 синхронизации вырабатывает сигналы управления, синхронизирующие работ/ устройства; блок 11 задания кодовых вариаций изменяет выходное напряжение с зависимости от полярности управляющего на выходе перключателя 15; сумматор 9 вычисляет значение старшей произвол 2| | i i

ной Q2z- делитель 3 напряжения

Зх2 flt задает величину коэффициента уравнения

-г- ; переключатели 16, 17 подают начэль- О2

ные условия интегратора 1, 2 в начале процесса интегрирования на границе l,t.

Область интегрирования рассматриваемой краевой задачи и поверхность решения представлена на фиг,4. Решение ищут последовательно на сканирующих плоскостях

СП1, . На нулевой сканирующей

плоскости СП0 решение задано в виде начального условия U (х,0)0.

Рассмотрим процесс получения решения на первой сканирующей плоскости Cfli последовательно на точках с координатами

XI, tl, X2, tl,..., Xutl.

Исходя из уравнения (1) для значений компонент искомой функции, для первой

точки первой сканирующей плоскости CHi (фиг.4) компоненты равны:

U((t)io+/U1(t)iodt; 5°

U(x)n U(x)oi +

ДхАх Ах

1П+ / U x idx-f / dx /U11(x)oidx

«nnn

где At и Д х- интервалы интегрирования по независимым переменным t и х. Обозначим через

А U1 (t )ю 02U (х )oi и, считая А постоянным в интервале интегрирования, имеем

. U(t)n U(t)io-i-AioAt;

U(x)ii U(x)oi + U1(x)oi Ax +

1 . Ax2

+

Aoi

Q - 2 Из условия равенства компонентов искомой функции на поверхности области ин- тегрировэния U(t)n U(x)n ,будем иметь U (Ою + AAt U(x)oi +

0

5

0

5

1

-bu4x)oiAx+- A

Ах2

Q

(2)

относительно А, имеем JlMll )io + U(x)i -m4x)oi Ах

Л.оi

At

1 Ах2

Q2 2

Когда значения шага интегрирования Ах и At по независимым переменным произвольны, уравнение (2) имеет вид

A -Bi U(t)io B2U(x)oi + B3U1 (x)oi, (3)

где Bi B2 - 1

A Y2

2Q2

B3

Ax

AtAi

2Q2

Для произвольной точки области интегрирования уравнение (3) имеет следующий вид:

Aij Biyit)i(j-i)+B2U(xXi-i)j+

+ Взи (х),-1),.(4)

Как видно из уравнения (4), нет необходимости в интегрировании по независимей переменной t, так как оно получено из усло- вия равенства U(x)ij U(t)ij. Кроме того, для получения значения искомой функции на последующих точках области интегрирования интегрированием вычисленного значения старшей производной необходимо иметь значени- функции наточках предыдущей сканирующей плоскости, которые в уравнении (4) соответствуют значениям U(t) to - 1) и значениям функции U(x) (i - i)j и ее производной U1(x) (i - i)j на (I - 1)-й точке j-й сканирующей плоскости. Так как для точек нулевой сканирующей плоскости j - 0 значения функции из краевых условий задачи U(x,0)0, которые в формуле (4) соответствуют значениям U(t)i (j -1), также заодно значение функции на нулевой первой сканирующей плоскости j - 1 из краевых условий задачи U(l, t)-1, которое соответствует значению U(x) (i - i)j в формуле (4) U(x)oi, то вычислительный процесс можно начинать с первой точки первой сканирующей плоскости U(x)n- U(t)ii, значение которой можно найти последовательным интегрированием значений старшей производной

BiU(t)io-B2U(x)oi -BaU Cx))

на интеграторах 1, 2, задавая произвольно значение производной U (x)oi, величину ко- торой можно корректировать по результату вычисления на последней точке первой сканирующей плоскости и сравнения ее с граничным условием U(0,t)0.

Устройство работает следующим обра- эом.

При нажатии кнопочногопереключателя 20 управляющий сигнал с выхода 33 блока 12 синхронизации поступает на первые управляющие входы переключателей 16 и 17 и производит установку начальных условий на интеграторах 1, 2; этот же сигнал поступает на первый управляющий вход блока 8 памяти и производит установку в нуяь первую группу ячеек памяти, так как U(x,0) При нажатии кнопочного переключателя 19 первый управляющий сигнал с выхода 34 блока 12 синхронизации в виде импульса малой скважности второго одновибратора 23 поступает на управляющие входы блока 7 па- мяти, на второй управляемый вход блока 8 памяти. Образуется алгебраическая сумма по формуле (4), которзя-сохраияется на выходе 7 памяти В кснце действия управляющего сигнала с выходя 34 блока 12 синхронизации срабатывает третий одно- вибратор 24, который гадает шаг интегрирования Дх и на выходе устройств которым является выход интегратора 2 получаем значение искомой функции на первой точке первой сканирующей споскости СГМ xi ti. В результате действия второго управляющего сигнала выходоп 34, 35 блока 12 синхронизации получим значение исковой функции на второй точке первой сканирующей пло0 5

0

5

о

5 п Q е

скости СП1 Х2 ti и, продолжая, идем до (п - 1)-й точки первой сканирующей плоскости СП1 Xn - i ti. Обеспечивается непрерывность получения значения искомой функции на выходе устройства. Управляющий сигнал с выхода 36 блока 12 синхронизации в виде кода независимой х поступает на третий управляющий вход блока 8 памяти и обеспечивает выдачу соответствующего значения начальных условий на сумматоре 9 и запись значения искомой функции с выхода интегратора 2 и одну из ячеек вторых п ячеек блока 8 памяти.

После получения значения искомой функции на ( п-1)-й точке сканирующей плоскости СПч по очередному управляющему сигналу с выходов 34, 35 блока 12 синхронизации производится интегрирование на интеграторах 1, 2. В конце интервала интегрирования будем иметь значение искомой функции на n-й точке первойсканиру- ющей плоскости с координатой Xn ti, соответствующей граничной точке

С выхода 37 блока 12 синхронизации управляющий сигнал поступает на управляемый вход переключателя 15 и производит подключения сигнала сравнения выходного напряжения на инте: раторе 2 с краевым условием в блоке 13 задания краевых условий U(0.t)0.

Если Диг 0 ,

где AUr(U(x)n-U(O.t)), управляющий сигнал ALI с выхода блока 10 сравнения через переключатель 15 поступает на управляющий вход переключателя 40 блока 11 задан1 я кодовых вариаций и вызывает изменение на его выходе в соответсвии со знаком управляющего сигнала, что приводит к изменению краевого условия U (x)oi, выбранного произвольно. Управляющий сигнал с выхода 37 блока синхронизации поступает на вторые входы переключателей

16и 17, выходное напряжение блока 11 задания кодовых вариаций и блока 14 задания краевых условий через переключатели 16 и

17заносятся на вход начальных условий интеграторов 1, 2. Очередные упрзвляющие сигналы с выходов 34, 35 блока 12 синхронизации вызывают повторение процесса решения на первой сканирующей плоскости СПч до достижения равенства напряжения на выходе интегратора 2 краевому усповию U (Xut) задаваемого Олоком 13 на n-й точке сканирующей плоскости СПч с координатой Xuti. При достижении равенства управляющий сигнал с выхода 37 блока 12 синхронизации вызывает выработку сигнала AUr 0 на выходе блока 10 сравнения, который через переключатель 15 и нуль-орган 18 поступает на вход 32 блока

12 синхронизации и, в свою очередь, вызывает выработку сигнала с выхода 38, который поступает на четвертый управляемый вход блока 8 памяти и вызывает перезапись с вторых п ячеек соответствующих значений напряжения на сканирующей плоскости СП1 на первые п ячейки, соответствующие значениям напряжения на нулевой сканирующей плоскости СП0.

Следующие управляющие сигналы на выходах 34, 35 блока 12 синхронизации вызывают управление процессом решения на второй сканирующей плоскости СГЪ, так как блок 8 памяти последовательно будет выдавать напряжение, соответствующее первой сканирующей плоскости СГН, полученное в процессе решения.

По истечении интервала интегрирования Л t k вырабатывается m сигналов Л Ur 0 на выходе нуль-органа 18, который на выходе переполнения счетчика,25 в блоке 12 синхронизации вызывает выработку сигнала Останов устройства, что приводит к прекращению выработки сигналов управления блоком синхронизации.

Коэффициент управления задачи (1) задается делителем напряжения 3. В случае переменного коэффициента управления этой задачи или его нелинейности в блок- схему решающих элементов вводятся не- линейные блоки, и схема набора осуществляется, как в АВМ для решения обыкновенных дифференциальных уравнений.

Формула изобретения Устройство для решения краевых задач, содержащее первый и второй интеграторы, первый и второй блоки памяти, блок синхронизации, блок сравнения, блок задания ко- довых вариаций, первый и второй блоки задания краевых условий и первый делитель напряжения, выход которого подключен к информационному входу первого интегратора, выход которого подключен к информа- ционному входу второго интегратора, выход которого подключен к информационному входу первого блока памяти и первому входу блока сравнения, первый выход блока синхронизации подключен к входу сброса

первого блока памяти, второй выход блока синхронизации соединен с входами записи соответственно первого и второго блоков памяти, третий выход блока синхронизации подключен к входам установки начальных условий соответственно первого и второго интеграторов, четвертый выход блока синхронизации соединен с входом считывания первого блока памяти, пятый выход блока синхронизации подключен к входу перезаписи первого блока памяти, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит сумматор, второй, третий и четвертый делители напряжения, первый, второй и третий переключатели и нуль-орган, выхрд которого подключен к входу перезапуска блока синхронизации, первый выход которого подключен к первым управляющим входам первого и второго переключателей, шестой выход блока синхронизации соединен с вторыми управляющими входами первого и второго переключателей и с управляющим входом третьего переключателя, выход которого подключен к входу нуль-органа и входу опроса блока задания кодовых вариаций, выход которого соединен с информационным входом первого переключателя, выход которого подключен к входу задания начальных условий первого интегратора, выход которого через второй делитель напряжения подключен к первому входу сумматора, выход которого соединен с информационным входом второго блока памяти, выход которого подключен к входу первого делителя напряжения, выход первого блока задания краевых условий подключен к второму входу блока сравнения, выход которого подключен к информационному входу третьего переключателя, выход второго блока задания краевых условий соединен с информационным входом второго переключателя, выход которого соединен с входом задания начальных условий второго интегратора, выход которого через третий делитель напряжения подключен к второму входу сумматора, выход первого блока памяти через четвертый делитель напряжения соединен с третьим входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения краевых задач | 1989 |

|

SU1640718A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1270779A1 |

| Устройство для моделирования диффузионных процессов | 1980 |

|

SU945873A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1441326A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Устройство для интегрирования дифференциальных уравнений | 1985 |

|

SU1273962A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Способ управления тиристорным регулятором | 1985 |

|

SU1282287A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

Изобретение относится к вычислительной технике, преимущественно может быть использовано для построения аналоговых и гибридных вычислительных машин, предназначенных для решения краевых задач, описываемых уравнением в частных производных параболического типа. Цель изобретения - повышение быстродействия и упрощение устройства. Для достижения этой цели устройство содержит сумматор, три делителя напряжения,три переключателя и нуль-орган, в результате чего значения искомой функции на точках сканирующей плоскости находятся за одну итерацию путем вычисления величины старших производных в уравнениях параболического типа в частных производных, что позволило исключить внутренние итерации на точках сканирующей плоскости, обеспечить непрерывность интегрироваия на сканирующей плоскости.4 ил. fe

68frfr29l

39

40

+Uon -Uon Фиг.З

U(C,t)1

| Козлов Э.С | |||

| Автоматизация процессов решения краевых задач | |||

| М.: Энергия, 1974, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Авторское свидетельство СССР Ы 1106303, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1991-01-30—Публикация

1989-02-07—Подача