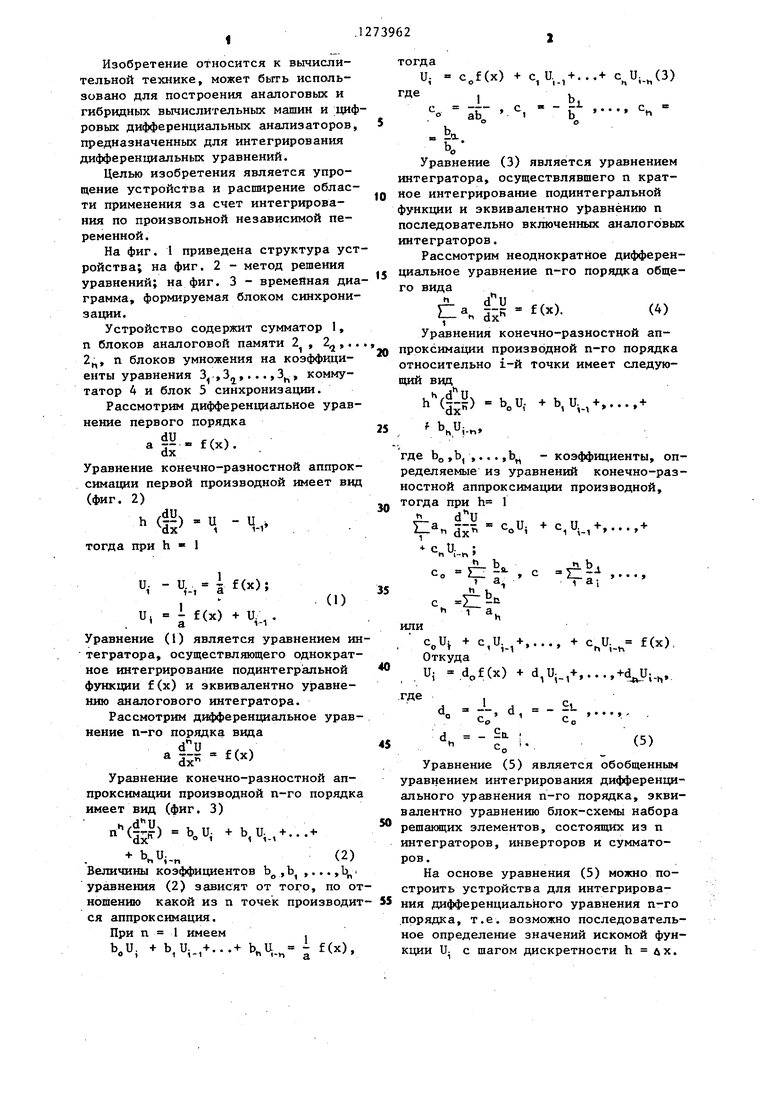

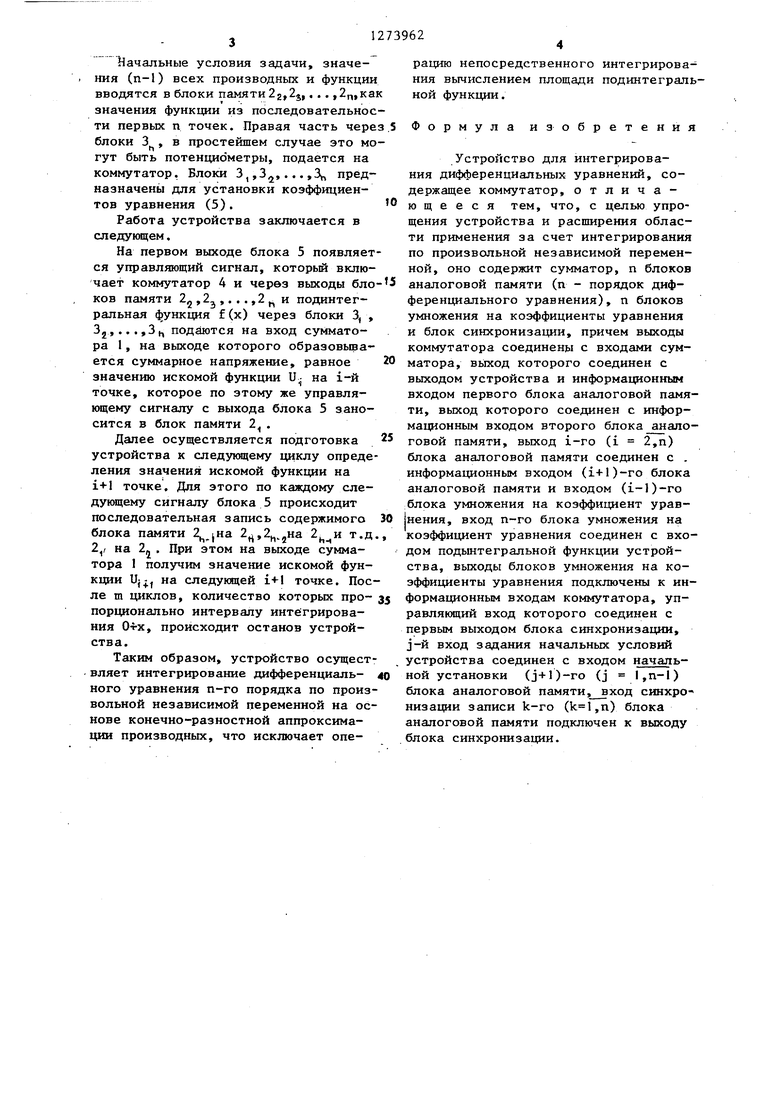

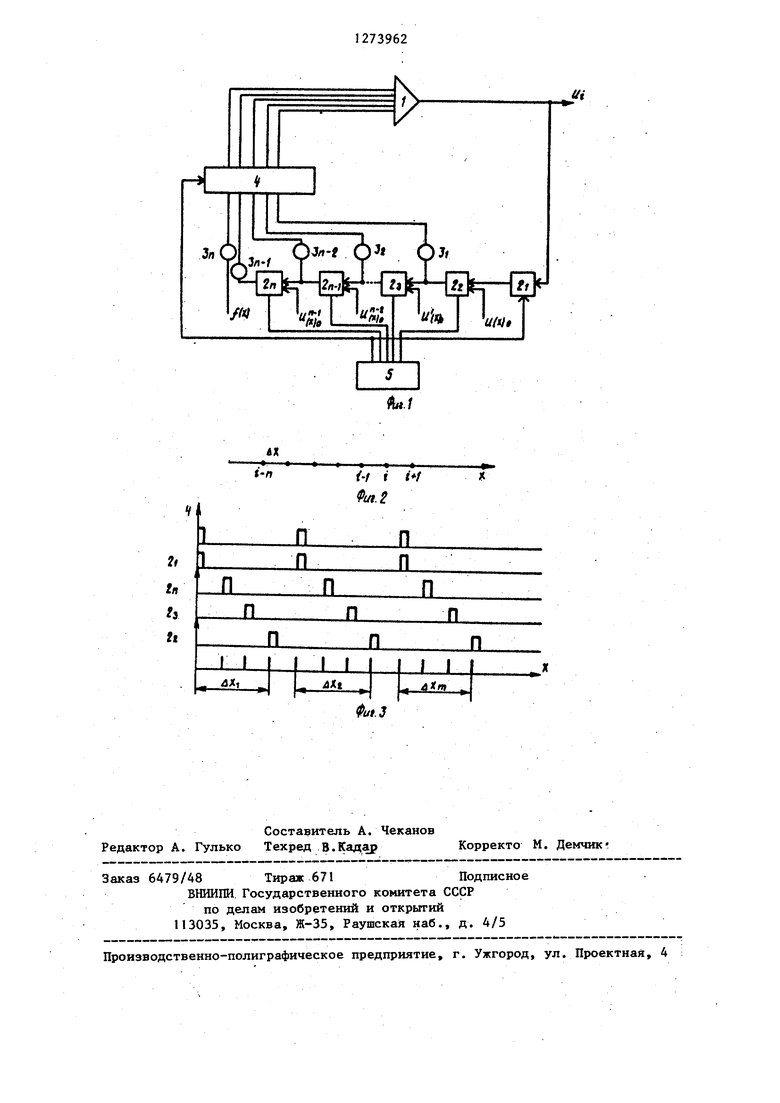

Изобретение относится к вычислительной технике, может быть использовано для построения аналоговых и гибридных вычислительных машин и циф ровых дифференциальных анализаторов, предназначенных для интегрирования дифференциальных уравнений. Целью изобретения является упрощение устройства и расширение области применения за счет интегрирования по произвольной независимой переменной . На фиг. I приведена структура уст ройства; на фиг. 2 - метод решения уравнений; на фиг. 3 - временная диа грамма, формируемая блоком синхронизации. Устройство содержит сумматор 1, п блоков аналоговой памяти 2 , 2,. 2, п блоков умножения на коэффициенты уравнения 3., 3, ,..., 3 , коммутатор 4 и блок 5 синхронизации. Рассмотрим дифференциальное уравнение первого порядка Уравнение конечно-разностной аппрок симации первой производной имеет вид (фиг. 2) . ,dU. dx и - U тогда при h 1 5 f(x); i - Ч-, ,, - f(x) ч-и.:. Уравнение (I) является уравнением ин тегратора, осуществляющего однократное интегрирование подинтеграпьной функции f(х) и эквивалентно уравнению аналогового интегратора. Рассмотрим дифференциальное уравнение п-го порядка вида Уравнение конечно-разностной аппроксимации производной п-го порядка имеет вид (фиг. 3) ,, ) + Ци.„-ь...-ь Ь„и.„(2) Величины коэффициентов Ь,Ь ,...,Ь. уравнения (2) зависят от того, по от ношению какой из п точек производит ся аппроксимация. При п 1 имеем ь„и. -нь,и..,+...ь„и, f(x). и, с„(х) + с,и.., + ...-ь ..(3) Уравнение (3) является уравнением интегратора, осуществлявшего п кратное интегрирование подинтеграпьной функции и эквивалентно уравнению п последовательно включенных аналоговых интеграторов. Рассмотрим неоднократное дифференциальное уравнение п-го порядка общего вида ta, f-R f(x).(4) Уравнения конечно-разностной аппроксимации производной п-го порядка относительно i-й точки имеет следующий вид ) . boU, + b,U.,,+,...,+ b,Uj.,, где bo,b ,...,Ь„ - коэффициенты, определяемые из уравнений конечно-разностной аппроксимации производной, тогда при h 1 Откуда Щ .(x) + d,Ui ,+ ..+VUi-.. ,1 dc --. d, ---,...,, , с iv(5) Уравнение (5) является обобщенным уравнением интегрирования дифференциального уравнения п-го порядка, эквивалентно уравнению блок-схемы набора решакнцих элементов, состоящих из п интеграторов, инверторов и сумматоров. На основе уравнения (5) можно построить устройства для интегрирования дифференциального уравнения п-го .порядка, т.е. возможно последовательное определение значений искомой функции и. с шагом дискретности h лх. Начальные условия задачи, значения (п-1) всех производных и функции вводятся в блоки памяти 22,2j,. .. ,2р,как значения функции из последовательности первьк п точек. Правая часть через блоки 3 , в простейшем случае это могут быть потенциометры, подается на коммутатор. Блоки 3, ,3,,... ,3, предназначены для установки коэффициентов уравнения (5). Работа устройства заключается в следующем. На первом выходе блока 5 появляется управляющий сигнал, которьй включает коммутатор 4 и через выходы блоков памяти 2,j ,2 ,. .. ,2 j и подинтегральная функция f (х) через блоки 3, 32, ...,3, подаются на вход сумматора 1, на выходе которого образовыва ется суммарное напряжение, равное значению искомой функции U на i-й точке, которое по этому же управляющему сигналу с выхода блока 5 зано сится в блок памяти 2. Далее осуществляется подготовка устройства к следукяцему циклу опреде ления значения искомой функции на i+1 точке. Для этого по каждому следующему сигналу блока 5 происходит последовательная запись содержимого блока памяти 2,jHa 2, т.д на 2j. При этом на выходе сумматора 1 получим значение искомой функции Uj на следующей точке. Пос ле m циклов, количество которых пропорционально интервалу интегрирования 0-гх, происходит останов устройства. Таким образом, устройство осущест вляет интегрирование дифференциального уравнения п-го порядка по произ вольной независимой переменной на ос нове конечно-разностной аппроксимации производных, что исключает операцию непосредственного интегрирования вычислением площади подинтегральной функции. Формула изобретения Устройство для интегрирования дифференциальных уравнений, содержащее коммутатор, отличающееся тем, что, с целью упрощения устройства и расширения области применения за счет интегрирования по произвольной независимой переменной, оно содержит сумматор, п блоков аналоговой памяти (п - порядок дифференциального уравнения), п блоков умножения на коэффициенты уравнения и блок синхронизации, причем выходы коммутатора соединены с входами сумматора, выход которого соединен с выходом устройства и информационным входом первого блока аналоговой памяти, выход которого соединен с информационным входом второго блока аналоговой памяти, выход i-ro (i 2,п) блока аналоговой памяти соединен с . информационным входом (i+l)-ro блока аналоговой памяти и входом (i-l)-ro блока умножения на коэффициент уравнения, вход п-го блока умножения на коэффициент уравнения соединен с входом подынтегральной функции устройства, выходы блоков умножения на коэффициенты уравнения подключены к информационным входам коммутатора, управляющий вход которого соединен с первым выходом блока синхронизации, j-й вход задания начальных условий устройства соединен с входом начальной установки (j+l)-ro (j l,n-l) блока аналоговой памяти,вход синхронизации записи k-ro (,n) блока аналоговой памяти подключен к выходу блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1392576A1 |

| Устройство для моделирования дифференциальных уравнений | 1989 |

|

SU1727130A1 |

| Аналого-цифровое устройство для решения системы дифференциальных уравнений | 1987 |

|

SU1462378A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1978 |

|

SU742946A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

| Устройство для решения краевых задач | 1989 |

|

SU1640718A1 |

| Аналого-цифровое вычислительное устройство | 1988 |

|

SU1501103A1 |

| Устройство для решения систем дифференциальных уравнений | 1987 |

|

SU1476502A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения аналоговых и гибридных вычислительных машин и цифровых дифференциальных анализаторов, предназначенных для интегрирования дифференциальных уравнений. Устройство содержит коммутатор, сумматор, п блоков аналоговой памяти, п блоков умножения на коэффициенты уравнения и блок синхронизации. В устройстве достигнуто сокращение затрат аппаратуры и расширена область применения за счет применения алгоО) ритма, основанного на аппроксимации дифференциального уравнения конечш мй разностями. 3 ил.

l-fl

Л

п

п

л

П

П

it

I I

I I

idXt

лх.

л/ г Фса.г

п

п

п

п

I I

4 I.

| Интегратор | 1979 |

|

SU807327A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР ,В 801004, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-07-02—Подача