Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах.

Цель изобретения - сокращение аппаратурных затрат при реализации в устройстве для деления оперативного обнаружения ошибок вычислений.

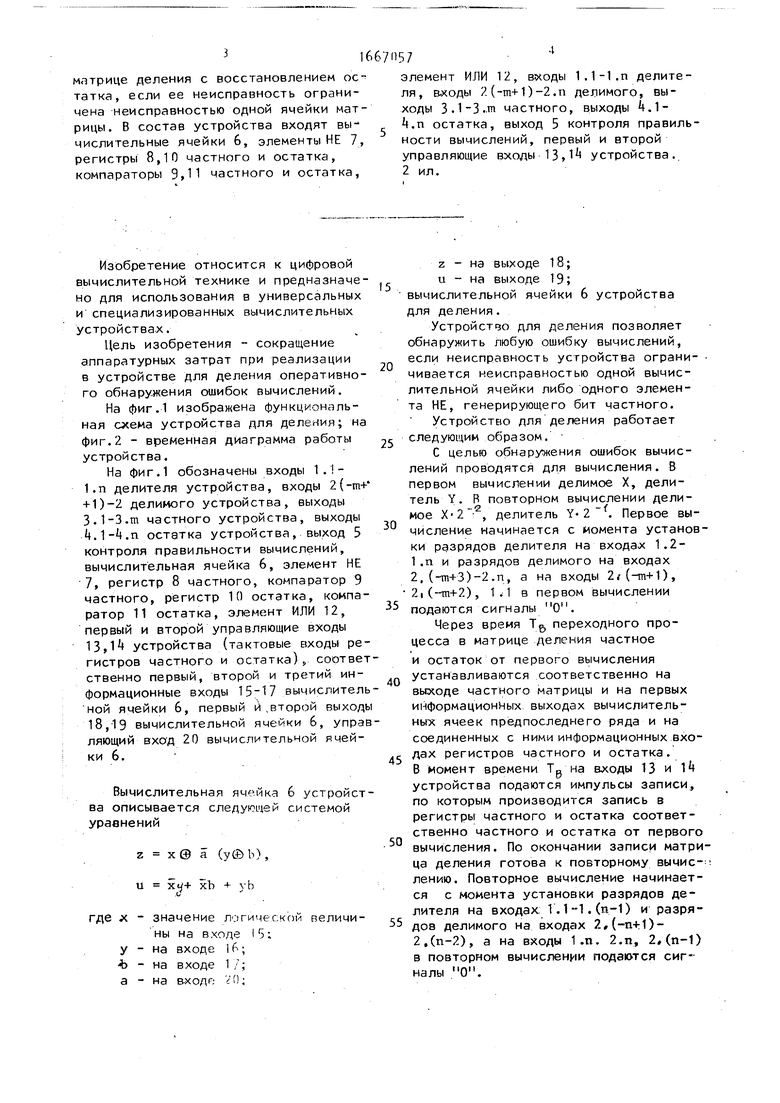

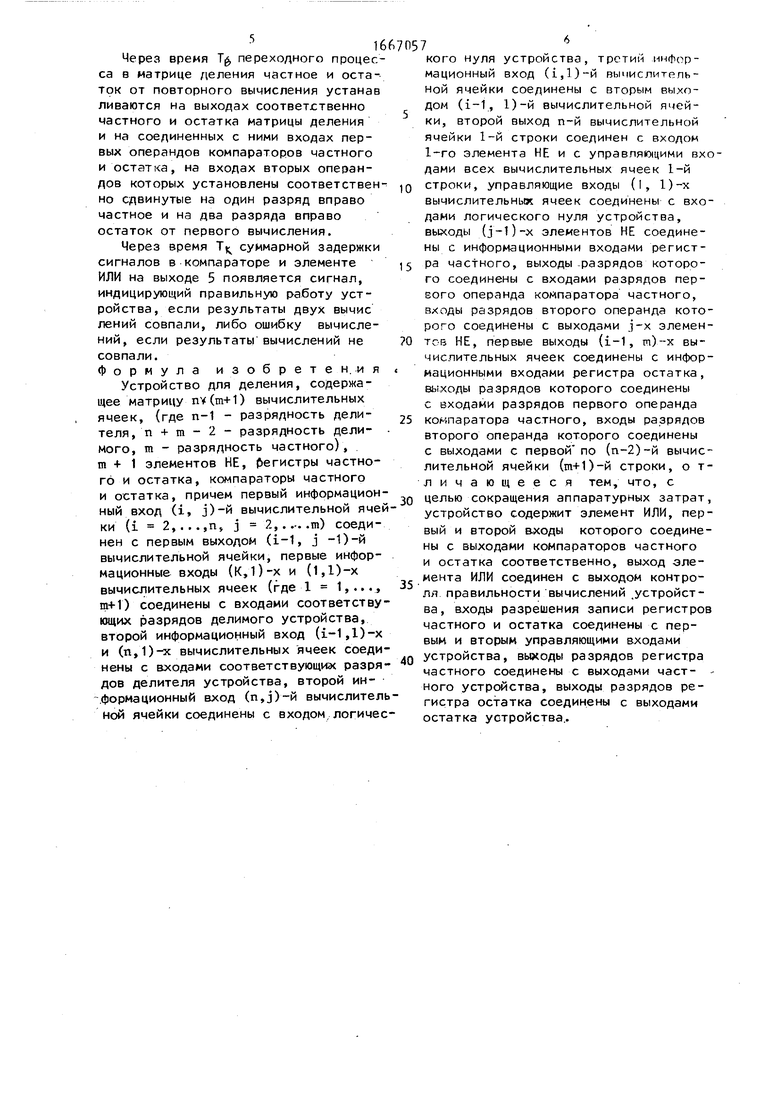

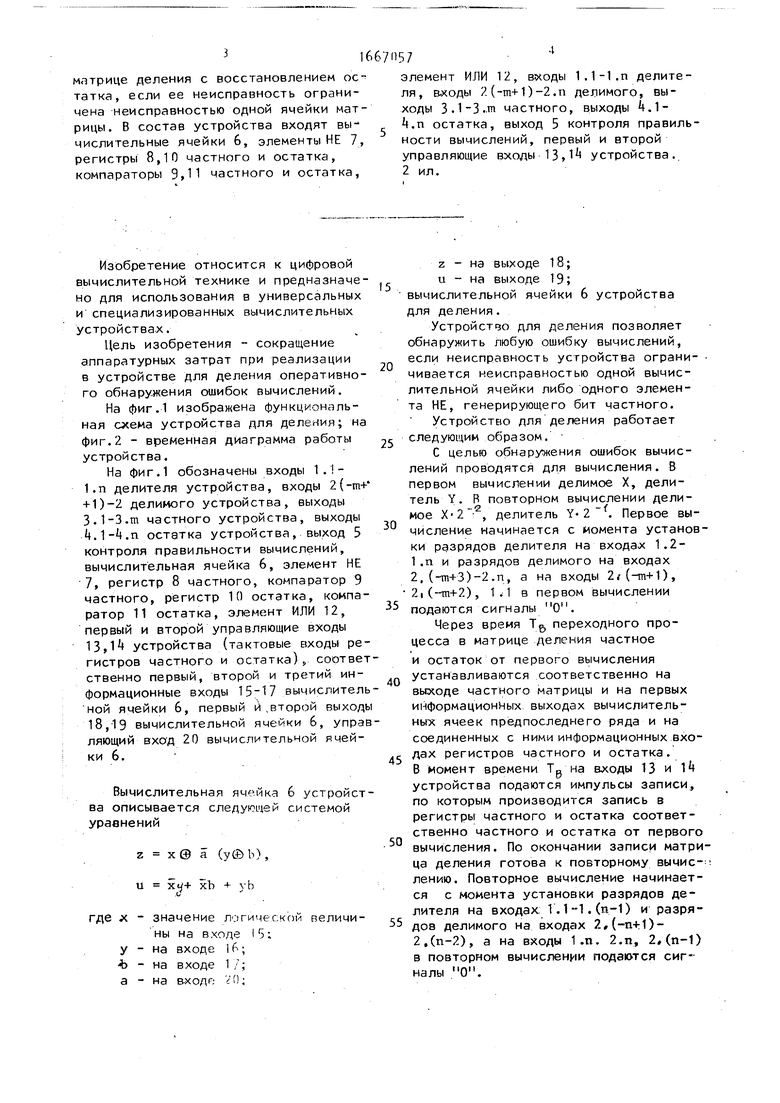

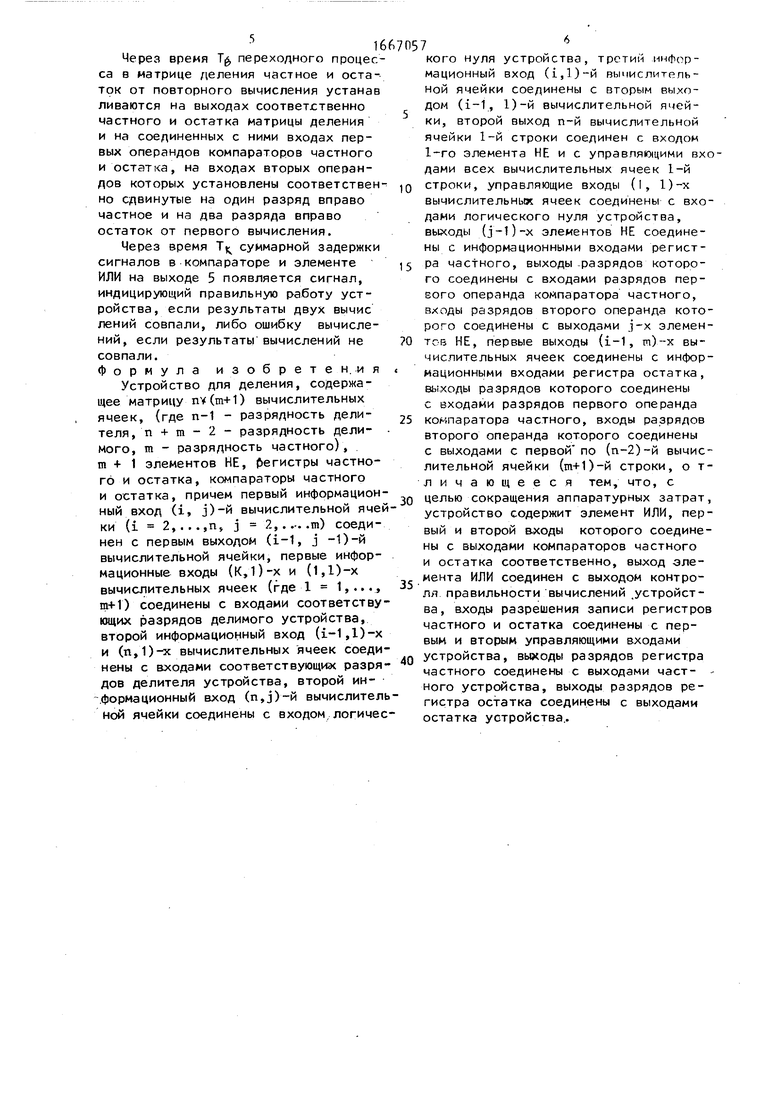

На фиг.1 изображена функциональная схема устройства для деления; на фиг.2 - временная диаграмма работы устройства.

На фиг.1 обозначены входы 1.1- 1.п делителя устройства, входы 2(-т+ + 1)-2 делимого устройства, выходы 3.1-З.т частного устройства, выходы Л-.п остатка устройства, выход 5 контроля правильности вычислений, вычислительная ячейка 6, элемент НЕ 7, регистр 8 частного, компаратор 9 частного, регистр 1(1 остатка, компаратор 11 остатка, элемент ИЛИ 12, первый и второй управляющие входы 13,1 устройства (тактовые входы регистров частного и остатка), соответственно первый, второй и третий информационные входы 15-17 вычислительной ячейки 6, первый и второй выходы 18,19 вычислительной ячейки 6, управляющий вход 20 вычислительной ячейки 6.

Вычислительная ячейка 6 устройства описывается следующей системой уравнений

z х ® а (у() , и хЬ 4 vh

О

где х - значение лмгичег КОР величины на входе I Г5; у - на входе Iь; Ъ - на входе I ; а - на входи I1;

5

0

5

0

5

0

45

50

5

z - на выходе 18; и - на выходе 19;

вычислительной ячейки 6 устройства для деления.

Устройство для деления позволяет обнаружить любую ошибку вычислений, если неисправность устройства ограничивается неисправностью одной вычислительной ячейки либо одного элемента НЕ, генерирующего бит частного.

Устройство для деления работает следующий образом.

С целью обнаружения ошибок вычислений проводятся для вычисления. В первом вычислении делимое X, делитель Y. R повторном вычислении делимое , делитель Y-2 . Первое вычисление начинается с момента установки разрядов делителя на входах 1.2- 1.п и разрядов делимого на входах 2.(-т+3)-2.п, а на входы 2/(-т+1), 2|(-та+2), 1.1 в первом вычислении подаются сигналы О.

Через время Ть переходного процесса в матрице деления частное

и остаток от первого вычисления устанавливаются соответственно на выходе частного матрицы и на первых информационных выходах вычислительных ячеек предпоследнего ряда и на соединенных с ними информационных входах регистров частного и остатка. В момент времени Т на входы 13 и 1 устройства подаются импульсы записи, по которым производится запись в регистры частного и остатка соответственно частного и остатка от первого вычисления. По окончании записи матрица деления готова к повторному вычислению. Повторное вычисление начинается с момента установки разрядов делителя на входах l.l-l.(n-l) и разрядов делимого на входах 2,(-п+1)- 2,(п-2), а на входы 1.п. 2.п, 2.(п-1) в повторном вычислении подаются сигналы О.

16

Через время Tg, переходного процесса в матрице деления частное и остаток от повторного вычисления устанав ливаются на выходах соответственно частного и остатка матрицы деления и на соединенных с ними входах первых операндов компараторов частного и остатча, на входах вторых операндов которых установлены соответствен- но сдвинутые на один разряд вправо частное и на два разряда вправо остаток от первого вычисления.

Через время Т суммарной задержки сигналов в компараторе и элементе

ИЛИ на выходе 5 появляется сигнал, индицирующий правильную работу устройства, если результаты двух вычис лений совпали, либо ошибку вычислений, если результаты вычислений не совпали. Формула изобретения

Устройство для деления, содержащее матрицу nҐ(m+1) вычислительных ячеек, (где п-1 - разрядность дели- теля, n + m - 2 - разрядность делимого, m - разрядность частного), m + 1 элементов НЕ, регистры частного и остатка, компараторы частного и остатка, причем первый информацией- ный вход (i, j)-u вычислительной ячейки (i 2,...,n, j 2,m) соединен с первым выходом (i-1, j -1)-й вычислительной ячейки, первые информационные входы (К,1)-х и (1,1)-х вычислительных ячеек (где ,..., т+1) соединены с входами соответствующих разрядов делимого устройства, второй информационный вход (i-1,l)-x и (п,1)к вычислительных ячеек соединены с входами соответствующих разря- дов делителя устройства, второй информационный вход (n,j)-u вычислительной ячейки соединены с входом логичес

5

0

5 5 0

/

кого нуля устройство, третий информационный вход (i,)-n выиигЛИТРПЬ- ной ячейки соединены с пторым выходом (i-1, 1)-й вычислительной ячейки, второй выход n-й вычислительной ячейки 1-й строки соединен с входом 1-го элемента НЕ и с управляющими входами всех вычислительных ячеек 1-й строки, управляющие входы (I, 1)-х вычислительных ячеек соединены с входами логического нуля устройства, выходы (j-l)-x элементов НЕ соединены с информационными входами регистра частного, выходы разрядов которого соединены с входами разрядов первого операнда компаратора частного, входы разрядов второго операнда которого соединены с выходами -х элемен- тгв НЕ, первые выходы (i-1, m)x вычис пительных ячеек соединены с информационными входами регистра остатка, выходы разрядов которого соединены с входами разрядов первого операнда компаратора частного, входы разрядов второго операнда которого соединены с выходами с первой по (п-2)-й вычислительной ячейки (т+1)-и строки, о т- личающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит элемент ИЛИ, первый и второй входы которого соединены с выходами компараторов частного и остатка соответственно, выход элемента ИЛИ соединен с выходом контроля правильности вычислений .устройства, входы разрешения записи регистров частного и остатка соединены с первым и вторым управляющими входами устройства, выходы разрядов регистра частного соединены с выходами частного устройства, выходы разрядов регистра остатка соединены с выходами остатка устройства.

st «si

€

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1721602A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Мультиконвейерный делитель | 1988 |

|

SU1587499A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах. Целью изобретения является сокращение аппаратурных затрат при реализации в устройстве для деления оперативного обнаружения ошибок вычислений. Оперативное обнаружение ошибок вычислений заключается в проведении повторного вычисления со сдвинутыми операндами и сравнении его результатов с результатами первого вычисления. При этом устройство для деления характеризуется временной и аппаратурной избыточностью. Поставленная цель достигается тем, что при повторном вычислении делитель сдвигается на один разряд вправо, делимое сдвигается на два разряда вправо. Такая организация сдвигов операндов позволяет сократить аппаратурную избыточность при реализации устройства. Устройство для деления позволяет обнаружить все ошибки вычислений в матрице деления с восстановлением остатка, если ее неисправность ограничена неисправностью одной ячейки матрицы. В состав устройства входят вычислительные ячейки 6, элементы НЕ 7, регистры 8, 10 частотного и остатка, компараторы 9, 11 частного и остатка, элемент 12 ИЛИ, входы 1.1 - 1.N делителя, входы 2.(-M + 1) - 2.N делимого, выходы 3.1 - 3.M частного, выходы 4.1 - 4.N остатка, выход 5 контроля правильности вычислений, первый и второй управляющие входы 13, 14 устройства. 2 ил.

S

V

s «N

vl

.

,1

NJ

1

Ј

hS-

,:

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и сиихронная арифметика | |||

| М.: Радио и связь, 1981, с | |||

| Фотореле для аппарата, служащего для передачи на расстояние изображений | 1920 |

|

SU224A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Patel Т.Н., Fung L.Y | |||

| Concurrent Error Detection in Multiplay and Divide Arrays | |||

| IEEE Transactions on Computers, 1983, v | |||

| c | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| , fig | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ( УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | |||

Авторы

Даты

1991-07-30—Публикация

1989-05-05—Подача