Изобретение относится к вычислительной технике и может быть использовано для локализации неисправностей в цифровых блоках.

Проверяемый цифровой блок должен иметь единую систему синхронизации и иметь выход синхронизации.

Цель изобретения - сокращение времени локализации неисправностей.

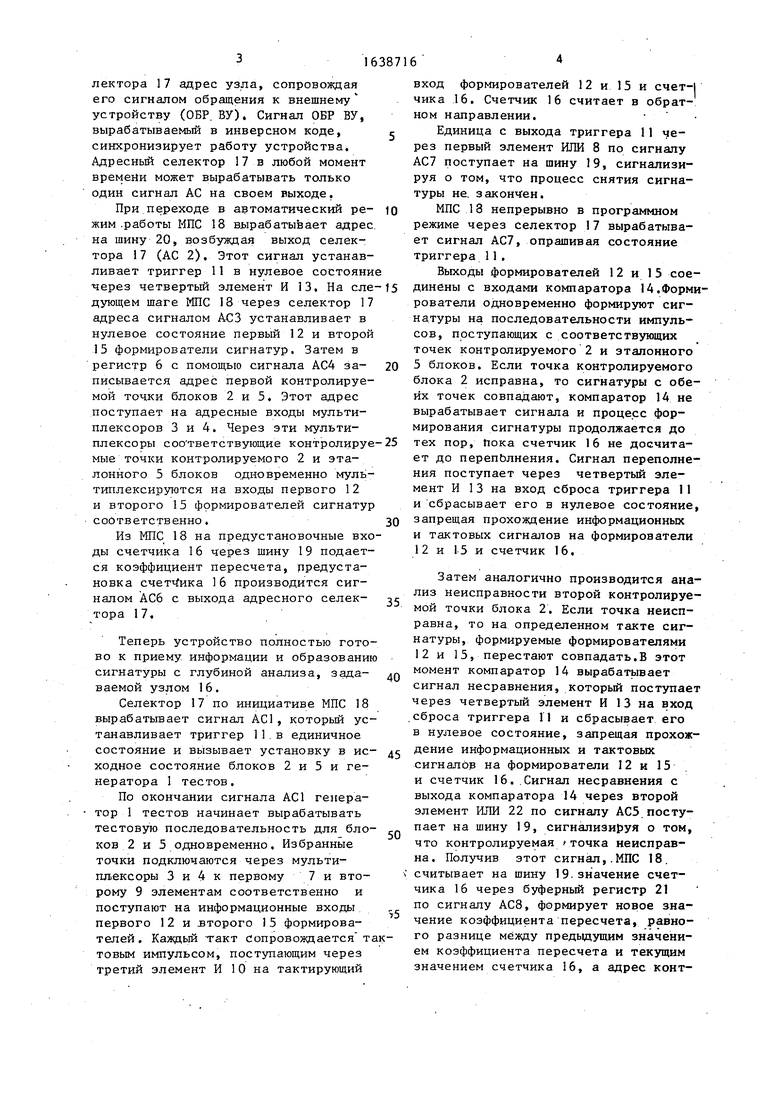

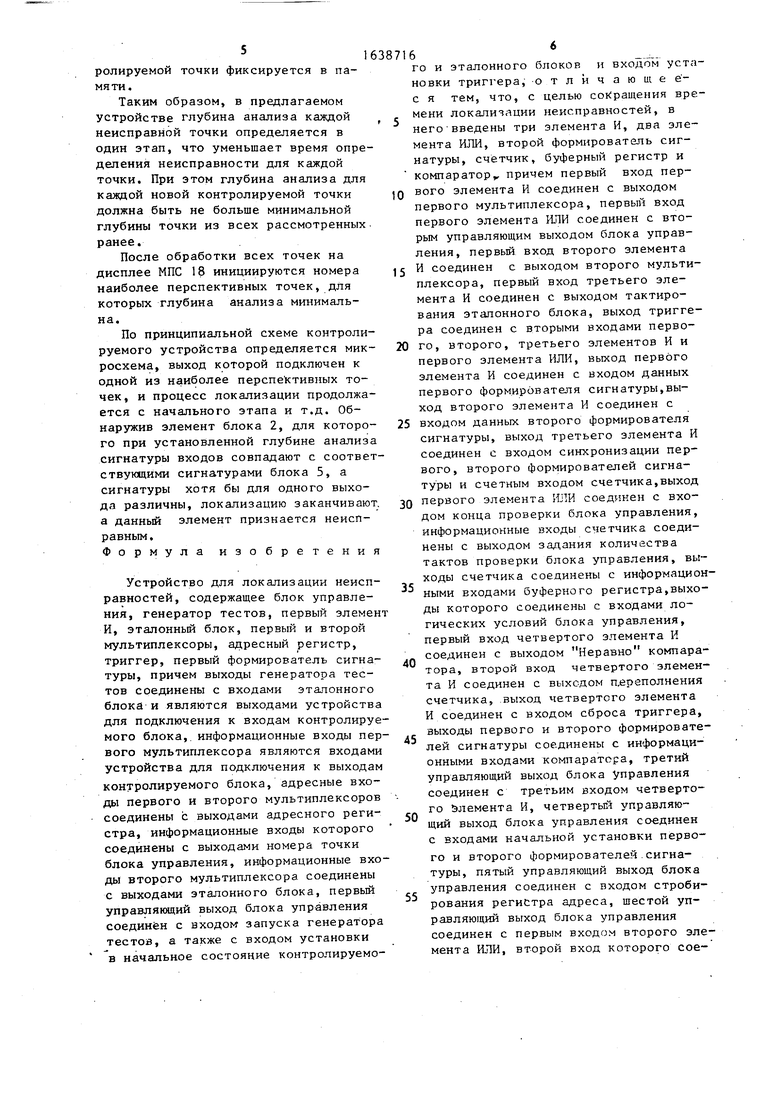

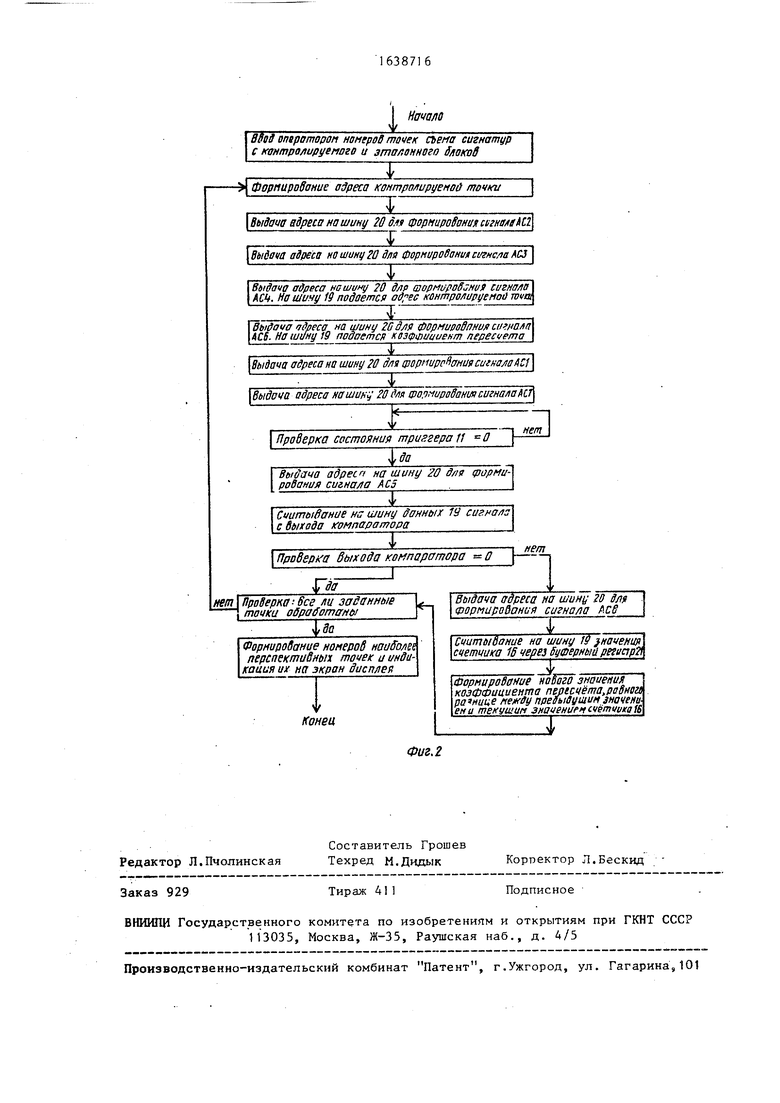

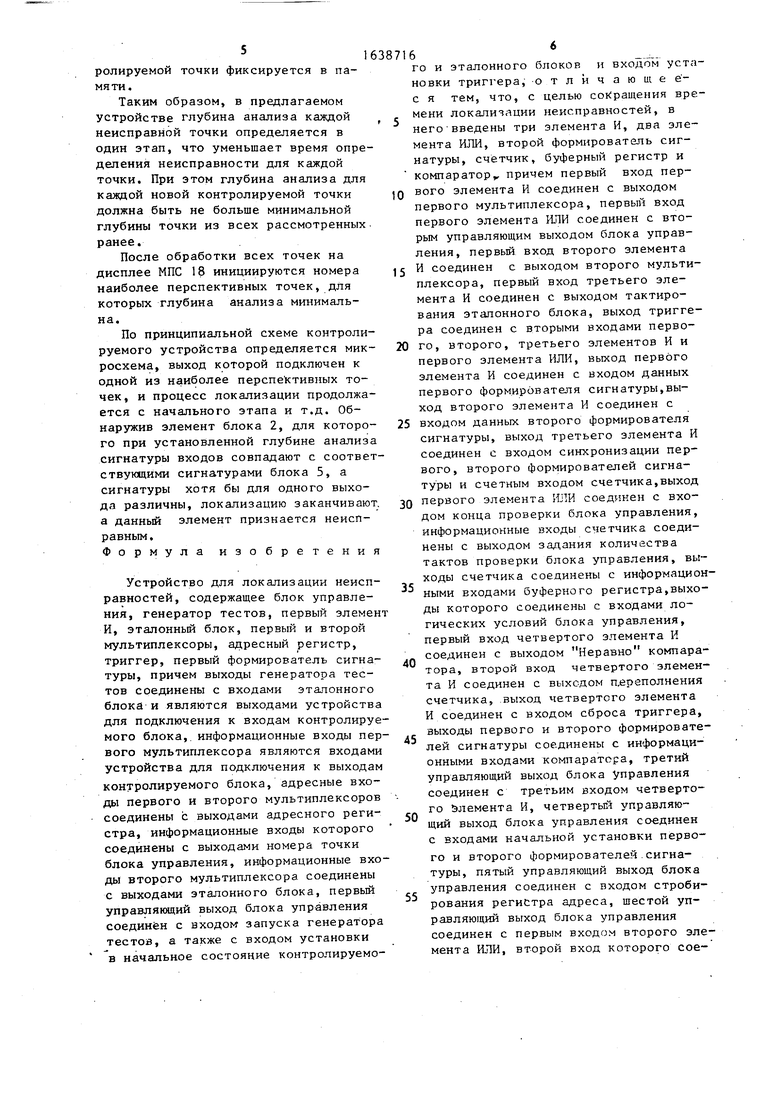

На фиг.1 изображена структурная схема устройства для локализации неисправностей; на фиг.2 - блок-схема алгоритма работы микропроцессорной системы.

Устройство содержит генератор 1 тестов, контролируемый блок 2,первый 3 и второй 4 мультиплексоры, эталонный блок 5, адресный регистр 6, первый элемент И 7, первый элемент ИЛИ 8, второй 9 и третий 10 элементы И, триггер 11, первый .формирователь 12 сигнатуры, четвертый элемент И 13, компаратор 14, второй формирователь 15 сигнатуры, счетчик 16, а также

блок управления, содержащий адресный селектор 17 и микропроцессорную систему 18, в качестве которой может быть использована микроЭВМ СЮ 300. Кроме того, в срстав устройства также входят шина I9 данных микропроцессорной системы, шина 20 адреса микропроцессорной системы, буферный регистр 21 и второй элемент ИЛИ 22.

В память микропроцессорной системы (МПС) 18 заложена программа уп- равления всей работой устройства для локализации неисправностей. После запуска программы оператор по опросу МПС 13 вводит в нее номера точек съема сигнатур с контролируемого 2 и эталонного 5 блоков. Затем устройство переходит в автоматический режим работы. При выполнении любого действия МПС 18 в соответствии с программой обработки воздействует на нужный узел с помощью адресного селектора 17. МПС 18 выдает по шине 20 адреса на информационные входы се(Л

о

ро

оо vj

э лектора 17 адрес узла, сопровождая его сигналом обращения к внешнему устройству (ОБР ВУ). Сигнал ОБР ВУ, вырабатываемый в инверсном коде, синхронизирует работу устройства. Адресный селектор 17 в любой момент времени может вырабатывать только один сигнал АС на своем выходе.

При переходе в автоматический ре- жим работы МПС 18 вырабатывает адрес на шину 20, возбуждая выход селектора 17 (АС 2). Этот сигнал устанавливает триггер 11 в нулевое состояние через четвертый элемент И 13. На еледующем шаге МПС 18 через селектор 17 адреса сигналом АСЗ устанавливает в нулевое состояние первый 12 и второй 15 формирователи сигнатур. Затем в регистр 6 с помощью сигнала АС4 за- писывается адрес первой контролируемой точки блоков 2 и 5. Этот адрес поступает на адресные входы мультиплексоров 3 и 4. Через эти мультиплексоры соответствующие контролируемые точки контролируемого 2 и эталонного 5 блоков одновременно мультиплексируются на входы первого 12 и второго 15 формирователей сигнатур соответственно.

Из МПС 18 на предустановочные входы счетчика 16 через шину 19 подается коэффициент пересчета, предустановка счетчика 16 производится сигналом АСб с выхода адресного селек- тора 17.

Теперь устройство полностью готово к приему информации и образованию сигнатуры с глубиной анализа, зада- ваемой узлом 16.

Селектор 17 по инициативе МПС 18 вырабатывает сигнал АС1, который устанавливает триггер 11 в единичное состояние и вызывает установку в ис- ходное состояние блоков 2 и 5 и генератора 1 тестов.

По окончании сигнала АС1 генера- тор 1 тестов начинает вырабатывать тестовую последовательность для бло- ков 2 и 5 одновременно. Избранные точки подключаются через мультиплексоры 3 и 4 к первому 7 и второму 9 элементам соответственно и поступают на информационные входы первого 12 и второго 15 формирователей . Каждый такт сопровождается татовым импульсом, поступающим через третий элемент И 10 на тактирующий

вход формирователей 12 и 15 и счет-1 чика 16. Счетчик 16 считает в обратном направлении.

Единица с выхода триггера 11 через первый элемент ИЛИ 8 по сигналу АС7 поступает на шину 19, сигнализируя о том, что процесс снятия сигнатуры не закончен.

МПС 18 непрерывно в программном режиме через селектор 17 вырабатывает сигнал АС7, опрашивая состояние триггера 11.

Выходы формирователей 12 и 15 соединены с входами компаратора 14.Формирователи одновременно формируют сигнатуры на последовательности импульсов, поступающих с соответствующих точек контролируемого 2 и эталонного 5 блоков. Если точка контролируемого блока 2 исправна, то сигнатуры с обеих точек совпадают, компаратор 14 не вырабатывает сигнала и процесс формирования сигнатуры продолжается до тех пор, пока счетчик 16 не досчитает до переполнения. Сигнал переполнения поступает через четвертый элемент И 13 на вход сброса триггера 11 и сбрасывает его в нулевое состояние запрещая прохождение информационных и тактовых сигналов на формирователи 12 и 15 и счетчик 16.

Затем аналогично производится анализ неисправности второй контролируемой точки блока 2. Если точка неисправна, то на определенном такте сигнатуры, формируемые формирователями 12 и 15, перестают совпадать.В этот момент компаратор 14 вырабатывает сигнал несравнения, который поступае через четвертый элемент И 13 на вход сброса триггера 11 и сбрасывает его в нулевое состояние, запрещая прохождение информационных и тактовых сигналов на формирователи 12 и 15 и счетчик 16. Сигнал несравнения с выхода компаратора 14 через второй элемент ИЛИ 22 по сигналу АС5 поступает на шину 19, сигнализируя о том, что контролируемая /точка неисправна. Получив этот сигнал,.МПС 18. : считывает на шину 19.значение счетчика 16 через буферный регистр 21 по сигналу АС8, формирует новое значение коэффициента пересчета, равного разнице между предыдущим значением коэффициента пересчета и текущим значением счетчика 16, а адрес контролируемой точки фиксируется в памяти.

Таким образом, в предлагаемом устройстве глубина анализа каждой неисправной точки определяется в один этап, что уменьшает время определения неисправности для каждой точки. При этом глубина анализа для каждой новой контролируемой точки должна быть не больше минимальной глубины точки из всех рассмотренных ранее.

После обработки всех точек на дисплее МПС 18 инициируются номера наиболее перспективных точек, для которых глубина анализа минимальна.

По принципиальной схеме контролируемого устройства определяется микросхема, выход которой подключен к одной из наиболее перспективных точек, и процесс локализации продолжается с начального этапа и т.д. Обнаружив элемент блока 2, для которого при установленной глубине анализа сигнатуры входов совпадают с соответствующими сигнатурами блока 5, а сигнатуры хотя бы для одного выхода различны, локализацию заканчивают. а данный элемент признается неисправным. Формула изобретения

Устройство для локализации неисправностей, содержащее блок управления, генератор тестов, первый элемен И, эталонный блок, первый и второй мультиплексоры, адресный регистр, триггер, первый формирователь сигнатуры, причем выходы генератора тестов соединены с входами эталонного блока и являются выходами устройства для подключения к входам контролируемого блока, информационные входы первого мультиплексора являются входами устройства для подключения к выходам контролируемого блока, адресные входы первого и второго мультиплексоров соединены с выходами адресного регистра, информационные входы которого соединены с выходами номера точки блока управления, информационные входы второго мультиплексора соединены с выходами эталонного блока, первый управляющий выход блока управления соединен с входом запуска генератора тестой, а также с входом установки в начальное состояние контролируемо

38716

го и эталонного блоков

10

25

и входом установки триггера, отличающее- с я тем, что, с целью сокращения времени локализации неисправностей, в него введены три элемента И, два элемента ИЛИ, второй формирователь сигнатуры, счетчик, буферный регистр и компаратор причем первый вход первого элемента И соединен с выходом первого мультиплексора, первый вход первого элемента ИЛИ соединен с вторым управляющим выходом блока управления, первый вход второго элемента 15 И соединен с выходом второго мультиплексора, первый вход третьего элемента И соединен с выходом тактирования эталонного блока, выход триггера соединен с вторыми входами перво- 20 го, второго, третьего элементов И и первого элемента ИЛИ, выход первого элемента И соединен с входом данных первого формирователя сигнатуры,выход второго элемента И соединен с входом данных второго формирователя сигнатуры, выход третьего элемента И соединен с входом синхронизации первого, второго формирователей сигнатуры и счетным входом счетчика,выход первого элемента ИЛИ соединен с входом конца проверки блока управления, информационные входы счетчика соединены с выходом задания количества тактов проверки блока управления, выходы счетчика соединены с информационными входами буферного регистра,выходы которого соединены с входами логических условий блока управления, первый вход четвертого элемента И соединен с выходом Неравно компаратора, второй вход четвертого элемента И соединен с выходом переполнения счетчика, выход четвертого элемента И соединен с входом сброса триггера, выходы первого и второго формирователей сигнатуры соединены с информационными входами компаратора, третий управляющий выход блока управления соединен с третьим входом четвертого элемента И, четвертый управляющий выход блока управления соединен с входами начальной установки первого и второго формирователей сигнатуры, пятый управляющий выход блока управления соединен с входом строби- рования регистра адреса, шестой управляющий выход блока управления соединен с первым входом второго элемента ИЛИ, второй вход которого сое30

35

40

45

50

55

динен с выходом Неравно компаратора, седьмой управляющий выход блока

управления соединен с входом разрешения считывания буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для локализации неисправностей | 1985 |

|

SU1339564A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано для локализации неисправностей в цифровых схемах. Цель изобретения - сокращение времени локализации неисправностей. Устройство содержит генератор тестов, эталонный блок, два мультиплексора, регистр адреса,четыре элемента И, два элемента ИЛИ,триггер, два формирователя сигнатур,компаратор, счетчик, блок управления, буферный регистр. 2 ил.

АС1

Ч

1

BSsS onapamopon номеров точек съема сигнатур с контролируемого и эталонного йяокоб

I

| Формирование адреса контролируемой точки И

| Выдача адреса на шин у 20 дм форнироКаних синапа ktl

i

Выдоча адреса но шину 20 для формировании июнем ACJ}

7Г

Выдача адреса на шину 20 д/ip шормиробйни сигнала АП. Ношичу w подается адрес контро/iupyenou rvi/at

т ш

Выдача чдреса на шину ZGd/m формирования стналп ACS. На шину Iff подается коэффициент пересчета

Выдача адреса на шину 20 для щорниреЯтю сигнала АС1

.Ь,

8ыдоча адреса нашин 20 Рля Формирования сигнала А(.Т

Проверка состояния триггера if 0

I Выдача адрес я на шину 20 д/w фарми роВания сигнала ACS|

Считывание не шину данных 19 сиг. но/is с выхода компаратора.

Проверка Выхода компаратора О

нет {Проверка: бее ли заёа нные 1 тачки обработаны

ф#о

Формирование номеров перспективных точек и индикация их на экран Зисплев

Т

коней

Редактор Л.Пчолинская

Составитель Грошев Техред М.Дидык

Заказ 929

Тираж 411

ВНИИГЩ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

1

Начало

очек съем алонного й

нет

нет

И

Выдача адреса на шину го дли Формирования сигнала ACS

Считывание на шину 19 значении счетчика 16 через буферный, pttucjpft

.-Ј

Формирование нового значения коэффициента пеп1счёта ра8квгй разнице не/коу преаыаишин значена- ени тек у шип эначенир метчика 16

Корректор Л.Бескид

Подписное

| Способ приготовления катализатора для гидрооблагораживания углеводородного сырья | 1980 |

|

SU973154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для локализации неисправностей | 1985 |

|

SU1339564A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-30—Публикация

1988-07-29—Подача