тупает выбранное с помощью мультиплексора 8 слово, выводимое из устройства. На элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 7 ошибочный разряд этого слова инвертируется и исправленное слово поступает на выход 9 ПЗУ.

Изобретение относится к вычислительной технике и может быть использовано при проектировании постоянных запоминающих устройств (ПЗУ).

Целью изобретения является упрощение устройства.

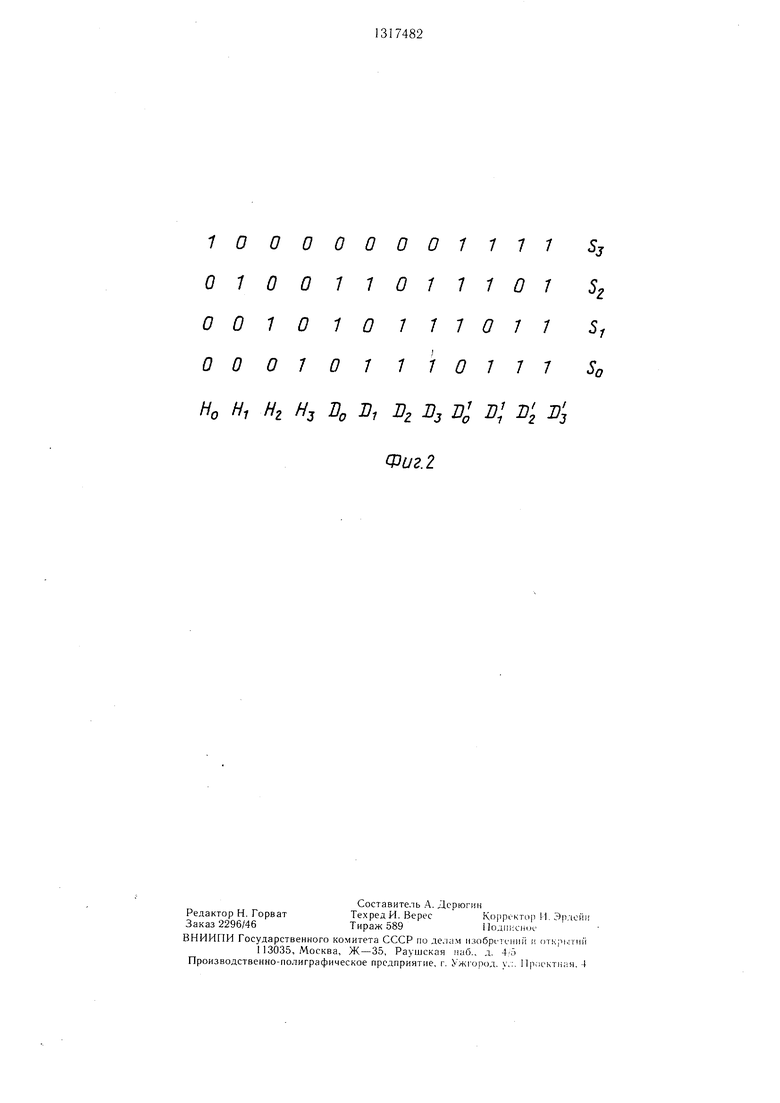

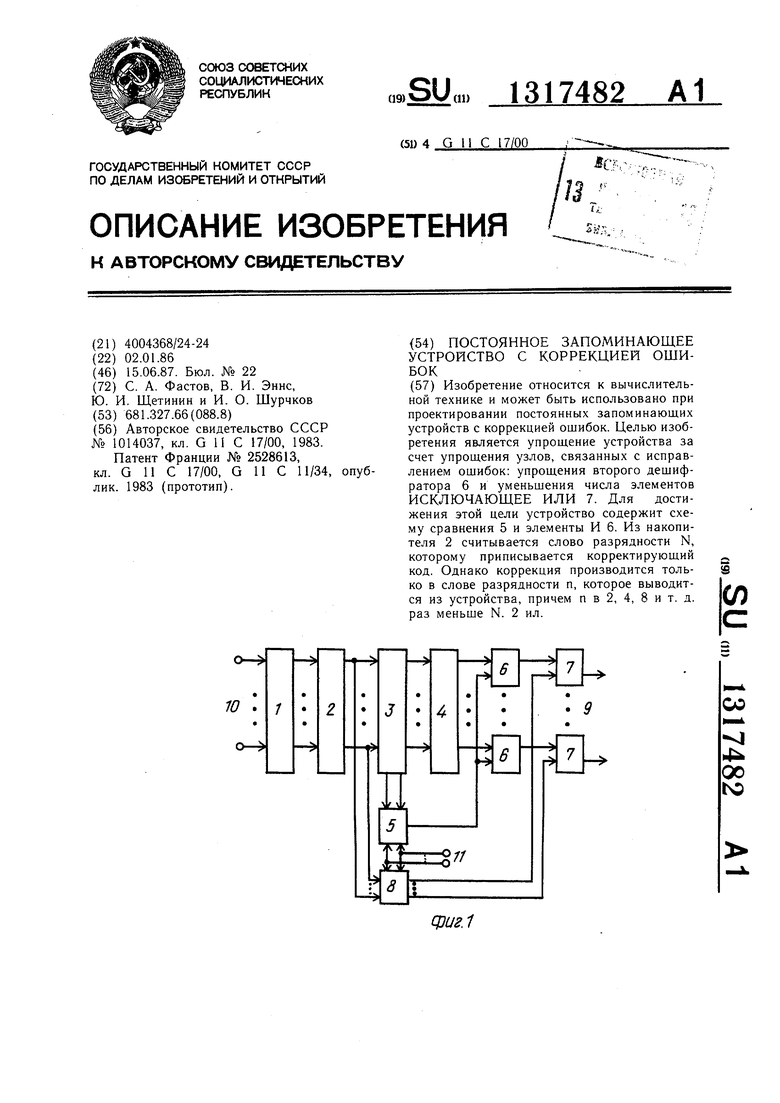

На фиг. 1 представлена функциональная схема постоянного запоминающего устройства с коррекцией ощибок; на фиг. 2 -

конкретный пример построения используе-ошибки нет, то на выходах элементов И 6 -

мой в устройстве проверочной матрицы кода. «О, и исправления ошибок не происходит.

Постоянное запоминающее устройствоПример построения проверочной матрицы

(фиг. 1) содержит первый дещифратор 1,(фиг. 2} приведен для длины слова N 8 и

накопитель 2, блок вычисления синдрома 3,

второй дешифратор 4, схему сравнения 5,

элементы И 6, элементы ИСКЛЮЧАЮ- 15 ных входов второй группы 11 равна 1. Раз.,., ,ЩЕЕ ИЛИ 7, мультиплексор 8. На фиг. 1ряды синдрома So ,..., Sj указывают на

показаны также выходы 9 ПЗУ, первые 10ошибку в информационных разрядах. Если

и вторые 11 адресные входы ПЗУ.

На фиг. 2 обозначены: Д,..., Дз, До---- Д з - информационные разряды, Н,..., Н - проверочные разряды, S,..., S - разряды синдрома.

Устройство при исправлении ошибок работает следующим образом.

На адресные входы устройства. 10 и 11 поступает адрес считываемого из ПЗУ ело- 25 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и число ва. Из накопителя 2 с помощью дешифра-элементов И во втором дешифраторе уменьтора 1 выбирается слово, соответствующе адресным сиг налам, установленным ь

20

Если ошибка обнаружена в разряде, который не выводится из устройства, или

длины слова, вьшодимого из устройства, равной четырем. В таком устройстве число адресSj О, то ошибка произошла в Д ,...Дз , а при Sj 1 ошибка произошла в Л,...Л, (фиг. 2).

По сравнению с прототипом предлагаемое решение позволяет значительно упростить блок исправления ошибок. При длине считываемого из накопителя слова N и длине выводимого из устройства слова п число

цается на N-п.

входах 10. Это слово разрядности N поступает как на входы блока вычисления синд- ро.ма 3, так и на входы .мультиплексора 8. Коммутация информационных и проверочных разрядов слова с целью вычисления синдрома в блоке 3 осуш,1:стч.,- яется в соответствии с проверочной матрицей (фиг. 2).

Формула изобретения

Постоянное запоминающее устройство с коррекцией ошибок, содержащее накопитель, первый и второй дешифраторы, блок вычисления синдрома, мультиплексор, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы Старшие разряды выш TeHHoi u в блоке 3 которых являются выходами устройства, синдрома, число которы ра но числу ад-входы первого дешифратора и управляющие

ресных сигналов на входах il, ос.упаютвходы мультиплексора являются адреснына схему сравнения 5, в которой происхо-ми входа.ми первой и второй группы устдит их сравнение с разрядами адресногоройства, выходы первого де1иифратора соеслова, установленного на входах 11, и, вдинены с входами накопителя, выходы кото40 рого соединены с входами блока вычислеслучае совпадения, на выходе схемы сравнения устанавливается -;. Остальные разряды вычисленного в блоке 3 синдрома передаются на входы второго дешифратора 4, с помощью которого происходит опредения синдрома, выходы первой группы которого соединены с входами второго дешифратора, отличающееся тем, что, с целью упрощения устройства, оно содержит схему

ление местоположения ошибочного разря- сравнения и элементы И, первые входы кода в слове, длина которого равна длине слова, выводимого из ПЗУ п. С выходов дещиф- ратора 4 информация о местоположении ощибочного разряда (вектор-ошибка) поступает на первые входы эле.ментов И 6, на вторые входы которых приходит со схемы сравнения 5 «1, если разряд, в котором обнаружена ошибка совпадает с разрядами слова, выводимого из устройства, и «О - в остальных случаях. С выходов элементов И 6 вектор-ошибка подается на первые входы элементов ИСКЛЮЧАЮторых соединены с соответствуюшими выходами второго дешифратора, а выходы - с первыми входами соответствуюших элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с соответствую- 50 щими выходами мультиплексора, информационные входы которого соединены с выходами накопителя, входы первой и второй групп схемы сравнения соединены соответственно с управляющими входами мультиплексора и с выходами второй группы бло55

ЩЕЕ ИЛИ, на вторые входы которых поска вычисления синдрома, а выход - с вторыми входами элементов И.

тупает выбранное с помощью мультиплексора 8 слово, выводимое из устройства. На элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 7 ошибочный разряд этого слова инвертируется и исправленное слово поступает на выход 9 ПЗУ.

Если ошибка обнаружена в разряде, который не выводится из устройства, или

(фиг. 2} приведен для длины слова N 8 и

длины слова, вьшодимого из устройства, равной четырем. В таком устройстве число адресошибку в информационных разрядах. Если

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и число элементов И во втором дешифраторе умень

Sj О, то ошибка произошла в Д ,...Дз , а при Sj 1 ошибка произошла в Л,...Л, (фиг. 2).

По сравнению с прототипом предлагаемое решение позволяет значительно упростить блок исправления ошибок. При длине считываемого из накопителя слова N и длине выводимого из устройства слова п число

элементов ИСКЛЮ элементов И во вт

цается на N-п.

Формула изобретения

ния синдрома, выходы первой группы которого соединены с входами второго дешифратора, отличающееся тем, что, с целью упрощения устройства, оно содержит схему

сравнения и элементы И, первые входы косравнения и элементы И, первые входы которых соединены с соответствуюшими выходами второго дешифратора, а выходы - с первыми входами соответствуюших элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с соответствую- щими выходами мультиплексора, информационные входы которого соединены с выходами накопителя, входы первой и второй групп схемы сравнения соединены соответственно с управляющими входами мультиплексора и с выходами второй группы бло

ка вычисления синдрома, а выход - с вторыми входами элементов И.

00000001111Sj

1001101110JS

01010111011Sj

00101110111So H, Нг Ну 4 D, Б, Б, Б 77/ Б , Б ,

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1642524A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Устройство декодирования для коррекции двойных ошибок | 1991 |

|

SU1833968A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Декодер линейного кода | 1986 |

|

SU1405118A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании постоянных запоминающих устройств с коррекцией ошибок. Целью изобретения является упрощение устройства за счет упрощения узлов, связанных с исправ- опуб- лением ощибок: упрощения второго дешифратора 6 и уменьщения числа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Для достижения этой цели устройство содержит схему сравнения 5 и элементы И 6. Из накопителя 2 считывается слово разрядности N, которому приписывается корректирующий код. Однако коррекция производится только в слове разрядности п, которое выводится из устройства, причем п в 2, 4, 8 и т. д. раз меньше N. 2 ил. о- Ю о- € (Л со 4; 00 ьо .1

| Постоянное запоминающее устройство | 1981 |

|

SU1014037A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ЭЛЕКТРИЧЕСКИЙ РАЗЪЕДИНИТЕЛЬ | 2011 |

|

RU2528613C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-06-15—Публикация

1986-01-02—Подача