Изобретение относится к технике связи и может быть использовано при построении буферных запоминающих устройств (БЗУ) в системах передачи дискретной информации.

Цель изобретения - расширение области применения устройства путем обеспечения возможности работы с раличными средствами передачи данных, в частности, с радиостанциями.

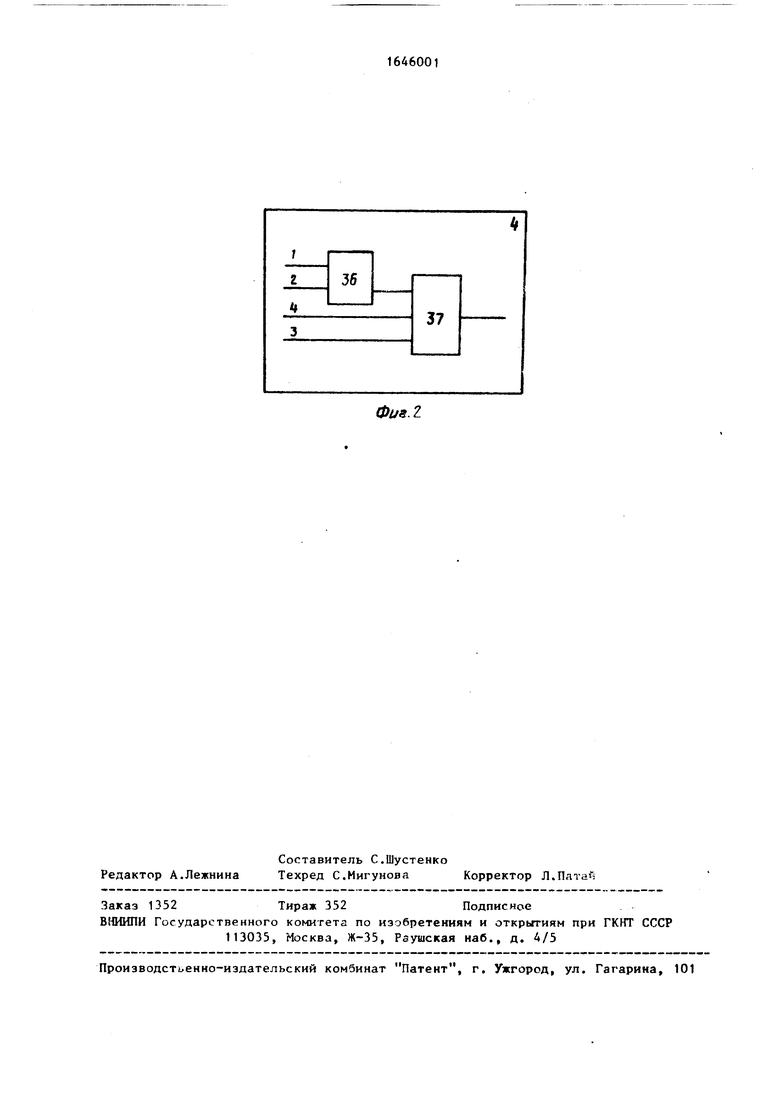

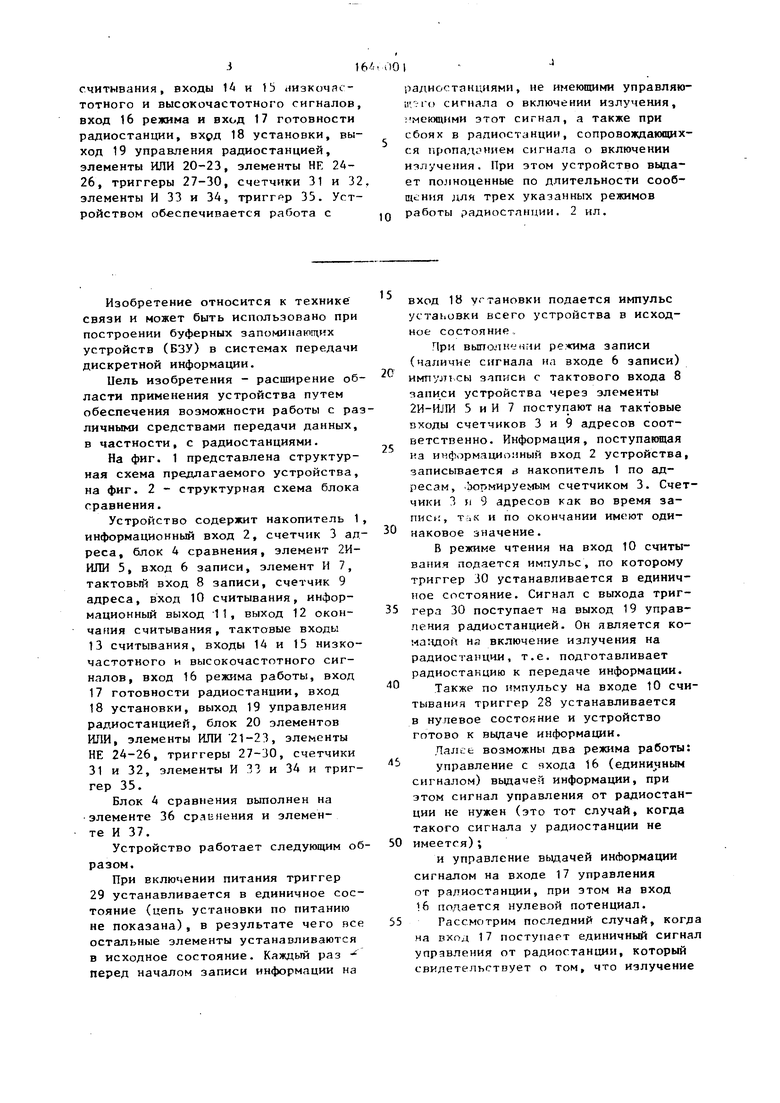

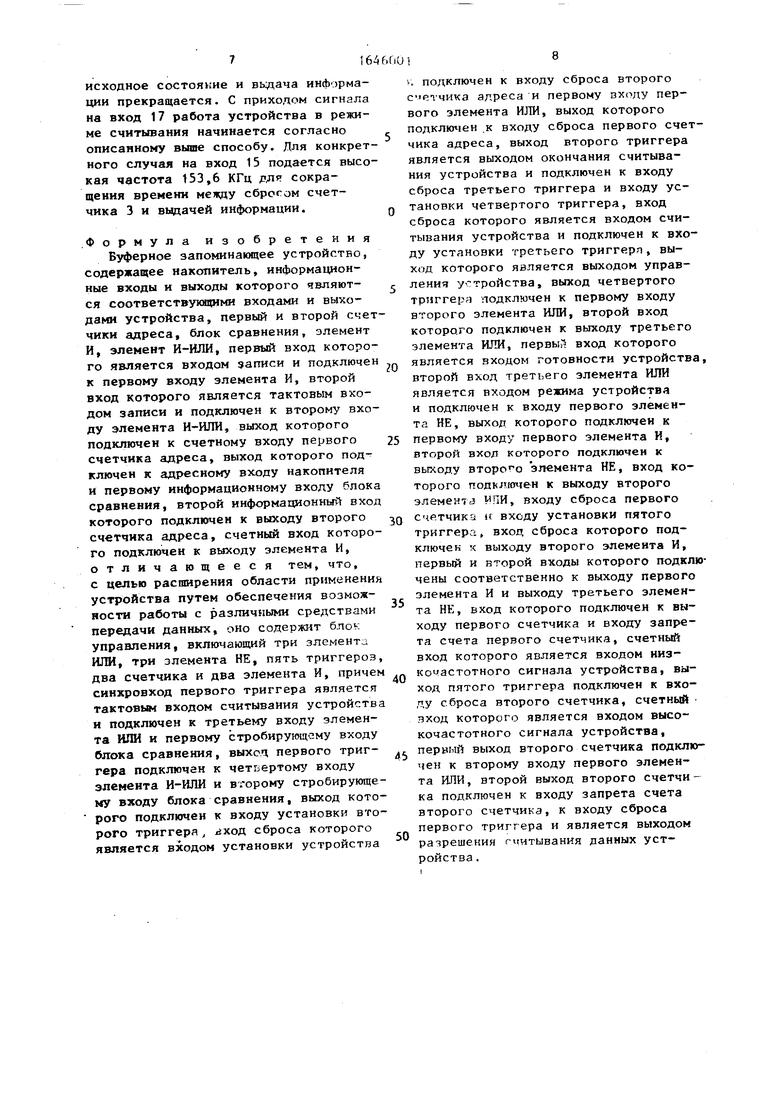

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - структурная схема блока сравнения.

Устройство содержит накопитель 1 информационный вход 2, счетчик 3 адреса, блок 4 сравнения, элемент 2И- ИЛИ 5, вход 6 записи, элемент И 7, тактовый вход 8 записи, счетчик 9 адреса, вход 10 считывания, информационный выход 11, выход 12 окон- чания считывания, тактовые входы 13 считывания, входы 14 и 15 низкочастотного и высокочастотного CHI- налов, вход 16 режима работы, вход

17готовности радиостанции, вход

18установки, выход 19 управления радиостанцией, блок 20 элементов ИЛИ, элементы ИЛИ 21-23, элементы НЕ 24-26, триггеры 27-30, счетчики 31 и 32, элементы И 33 и 34 и триггер 35.

Блок 4 сравнения выполнен на элементе 36 сравнения и элементе И 37.

Устройство работает следующим образом.

При включении питания триггер 29 устанавливается в единичное состояние (цепь установки по питанию не показана), в результате чего все остальные элементы устанавливаются в исходное состояние. Каждый раз перед началом записи информации на

5

С

5

0

5

0

0

5

вход 18 установки подается импульс установки всего устройства в исходное состояние

выполнении режима записи (наличие сигнала на входе 6 записи) импул сы записи с тактового входа 8 чаписи устройства через элементы 2И-ИЛИ 5 и И 7 поступают на тактовые входы счетчиков 3 и 9 адресов соответственно. Информация, поступающая на информационный вход 2 устройства, записывается в накопитель 1 по адресам, -Ьормируемым счетчиком 3. Счетчики 3 ь 9 адресов как во время записи, TJ,K и по окончании имгют одинаковое значение.

В режиме чтения на вход 10 считывания подается импульс, по которому триггер 30 устанавливается в единичное состояние. Сигнал с выхода триггера 30 поступает на выход 19 управления радиостанцией. Он является командой на включение излучения на радиостанции, т.е. подготавливает радиостанцию к передаче информации.

Также по импульсу на входе Ю считывания триггер 28 устанавливается в нулевое состояние и устройство готово к выдаче информации.

Далс-fc возможны два режима работы:

управление с чхода 16 (единичным сигналом) выдачей информации, при этом сигнал управления от радиостанции не нужен (это тот случай, когда такого сигнала у радиостанции не имеется);

и управление выдачей информации сигналом на входе 17 управления от радиостанции, при этом на вход 6 подается нулевой потенциал.

Рассмотрим последний случай, когда ча вход 17 поступает единичный сигнал управления от радиостанции, который свидетельствует о том, что излучение

включено и можно передавать информацию. По этому сигналу с Р-входа триг гора 27 снимав/ся единичный сигнал, а на R-вход поступает. Триггер 27 устанавливается в нулевое состояние, и со счетчика 31 снимается сигнал установки. Счетчик 31 начинает счет импульсов, поступающих постоянно с высокочастотного входа 15 устройства Импульс с второго выхода счетчика 31 (можно ;-спользсзать выход младшего разряда счетчика 564ИЬ )) поступает через элемент ИЛИ 21 На установочны вход счетчика J адреса и устанавливает его в исходное состояние. При дальнейшем счете нулевой сигнал кл первом выходе счетчика 31 чиыход половинного счетч счетчика 5;,ИЕ9. при установке на этом выходе имеется нулевой потенциал) чапрешасг по собственному вхо/.у управления дальней ший счет (т.е. кулевой сигнал остается до установки счетчика) и разрешает работу трип ера 35 и выдачу информации на информационный выход 11,

По первому,же фронту импульса г тактового входа 13 считывания триггер 35 вводится в единичное состояние. Триггер необходим для синхрик:- зации работы, т.е. привязки ъ тактовой частота считывания Единичным сигналом со своего выхода ти.ггер 35 разрешает прохождение импульсов считывания с тактопого входа 13 устройства через элемент 2И-Ш1И 5 на тактовый вхол счетчика 3 адреса. Информация по соответствуктщим адресам, формируемым счетчиком 3, из накопителя 1 поступает через блок 0 элементов ИЛИ на информациейный выход 1 устройства.

Значения выходов счетчиков 3 v 9 сравниваются элементом 36 сравнения Е блок 4 сравнения. При нии равенства этих значений единичный сигнал с яыхода элемент 36 сравнения г.остугаст на третий вход элемента И 37, на первом входе которого уже находится сигнал разрешения с вывода триггера 35. Первый же импульс с тактового входа тЗ через элемент ИЗ/ поступает на S-вход триггера 2ч, в результате чего на выход 12 устройства поступает единичный сигнал окончания считывания, на выход 19 - сигнал снятия включения излучения. Устройство прекращает выдачу информации. Триггеры 28, 27 и 30

0

0

и счетчик 31 устанавливаются в исходное состояние.

Рассмотрим режим работы устрой- сгна, когда от радиостанции не поступает управляющий сигнал, свидетель- ствующий о том, что излучен.ге включено, т.е. в радиостанции такого сигнала нет. В этом случае на входе 17 присутствует нулевой уровень, а управление происходит по входу 16, г.е. на этст вхс/i полов ся лосю/ : ьгч единили.in уровень. Таким образом, гос. записи информацки в накс- питель и прихоаа кмп ттьсон на вход 1C -mi «,и счетччча 32 ,нима- етсч ycTSHoiir (я так-Kt с S-входа трип-ер) , -) . Счсм-чик 32 начинает

С . ИМ1.ЛЬ -ОВ, ПОСТ }, - liOlUi.V ПОСТОЯНчс с ни ксчагтотп г о входа А устройства. Сигнал с вы jaa счетчика 32 (.можно :.СПОЛЬЗОЕ.-Ь 564ИБ9) по собственному с..;о,ьу у.тра . чагре- щоет дальнейший гчс-т. Этот же сигнал 5 мсргз г лемс-ггтк Н 2S и 33 поступает на R-иход триггера 27, Со счетчика 31 снимается уст овкз, и дал 2 про исходит ныпачс ииф гаиии аиг.логич- ко unniia-iHoh- y. - д ,/жка пита : лн- рориацин отнигк гс. . cm нала о нклпче ; . радиостанции Необ. .,- .( ТОГО,

у-г1лнрвился , ,,„1 II ,, рабочий рг- жиь-- ьадис.-танц п. Пп°. примтчяеньп. ра л -тлниин jra задержка сосчч пяет ЗС П- 00 мс. Лоодя иэ того к« низкочастотный ВУОД - подается частота ,3,73 рц.

того, возможен случаи, погда в рапиостанШ И произошел сбой иш кр гковремеч/ ый oT.as, }з результате снимается управ.:чюпг,й иг нал о чении изпученяя. Этпт саучяи мсжет совпасть по времени с моментом 5 передачи сообгц ння, ь результате ч«го 45ст ичфор ации (сообщения) кпжст б51ть не nepeuarui, r.t:. чь ло получатели. В конкретных системах это рааносчгльно пр ша яниь всего со- Q обгоения.

Чля устранения ппгп дл - -f Г1ия несбхд имо чо о лнот1- i- передачу сообЩ .нкл :.о. -nrf .i.. (г гапа после восстан ол ния г игк-i г, j 1::шуч«г} Ия.

Тлким образом, осли D момент передачи сообщен : .1 сит Haj о включении и- лу«ечия с вход, 17, счетчик 3t и трип ер 35 угтапчь: ь акгсл в

O

5

0

5

исходное состояние и ввдача информации прекращается. С приходом сигнала на вход 17 работа устройства в режиме считывания начинается согласно описанному выше способу. Для конкретного случая на вход 15 подается высокая частота 153,6 КГц для сокращения времени сбросом счетчика 3 и вцдачей информации.

.Формула изобретения Буферное запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соответствующими входами и выходами устройства, первый и второй счетчики адреса, блок сравнения, элемент И, элемент И-ИЛИ, первый вход которого является входом записи и подключен к первому входу элемента И, второй вход которого является тактовым входом записи и подключен к второму входу элемента И-ИЛИ, выход которого подключен к счетному входу первого счетчика адреса, выход которого подключен к адресному входу накопителя и первому информационному входу блока сравнения, второй информационный вход которого подключен к выходу второго счетчика адреса, счетный вход которого подключен к выходу элемента И, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности работы с различными средствами передачи данных, оно содержит управления, включающий три элемент ИЛИ, три элемента НЕ, пять триггеров, два счетчика и два элемента И, причем синхровход первого триггера является тактовым входом считывания устройства и подключен к третьему входу элемента ИЛИ и первому стробирующаму входу блока сравнения, выхоч первого триггера подключен к четвертому входу элемента И-ИЛИ и второму стробирующе- му входу блока сравнения, выход которого подключен к входу установки второго триггера t ход сброса которого является входом установки устройства

0

5

0

5

0

н подключен к входу сброса второго счетчика адреса и первому входу первого элемента ИЛИ, выход которого подключен к входу сброса первого счетчика адреса, выход второго триггера является выходом окончания считывания устройства и подключен к входу сброса третьего триггера и входу установки четвертого триггера, вход сброса которого является входом считывания устройства и подключен к входу установки третьего триггерп, выход которого является выходом управления устройства, выход четвертого триггера подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу третьего элемента ИЛИ, первый вход которого является входом готовности устройства, второй вход третьего элемента ИЛИ является входом режима устройства и подключен к входу первого элемента НЕ, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к выходу второго элемента НЕ, вход которого подключен к выходу второго элемента , входу сброса первого счетчика if входу установки пятого триггера, вход сброса которого подключен к выходу второго элемента И, первый и второй входы которого подключены соответственно к выходу первого элемента И и выходу третьего элемента НЕ, вход которого подключен к выходу первого счетчика и входу запрета счета первого счетчика, счетный вход которого является входом низкочастотного сигнала устройства, выход пятого триггера подключен к входу сброса второго счетчика, счетный зход которого является входом высокочастотного сигнала устройства, первый выход второго счетчика подключен к второму входу первого элемента ИЛИ, второй выход второго счетчика подключен к входу запрета счета второго счетчика, к входу сброса первого триггера и является выходом разрешения считывания данных устройства .

Фив.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226528A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278980A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Буферное запоминающее устройство | 1977 |

|

SU720507A1 |

| Микропрограммное устройство управления с контролем | 1987 |

|

SU1621026A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

Изобретение относится к технике связи и может быть использовано при построении буферных запоминающих устройств (лЗУ) в системах передачи дискретной информации. Цель изобретения - расширение области применения устройства путем обеспечения работы с различными радиосредствами. Устройство содержит накопитель 1, информационный вход 2, счетчики 3 и 9 адреса, блок 4 сравнения, элемент 2И-Ш1И 5, вход 6 sanH v. элемент И 7, такто- тзый вход 8 записи, тхоц 10 считывания, выходы информационный 11 и окончания считывания 2 и блок управления, включакхций тактовый вход 13

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1325565A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| I | |||

Авторы

Даты

1991-04-30—Публикация

1989-01-03—Подача