I.

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и системах.

Целью изобретения является упрощение устройства.

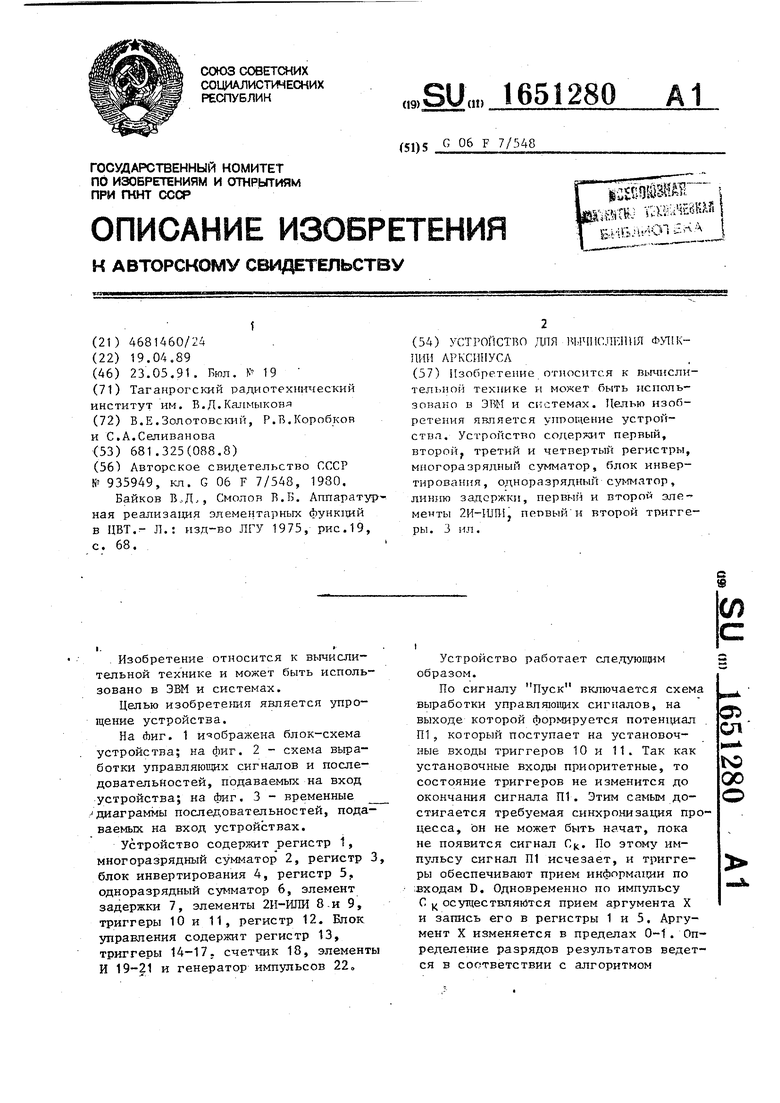

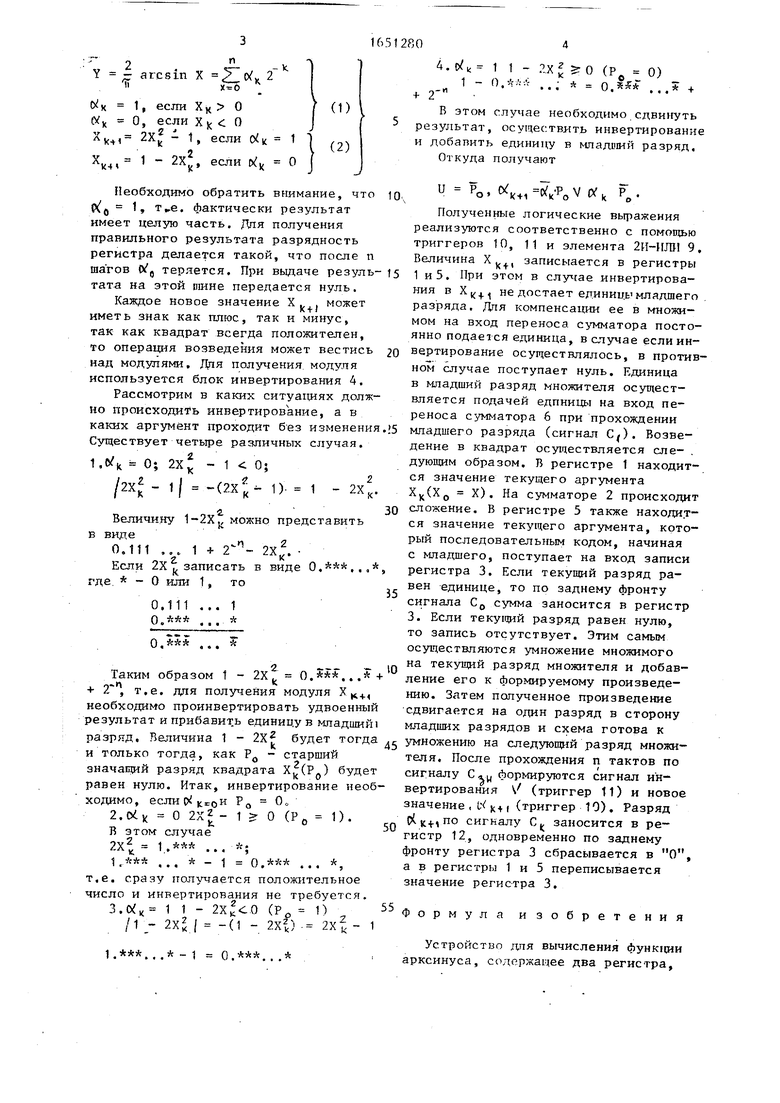

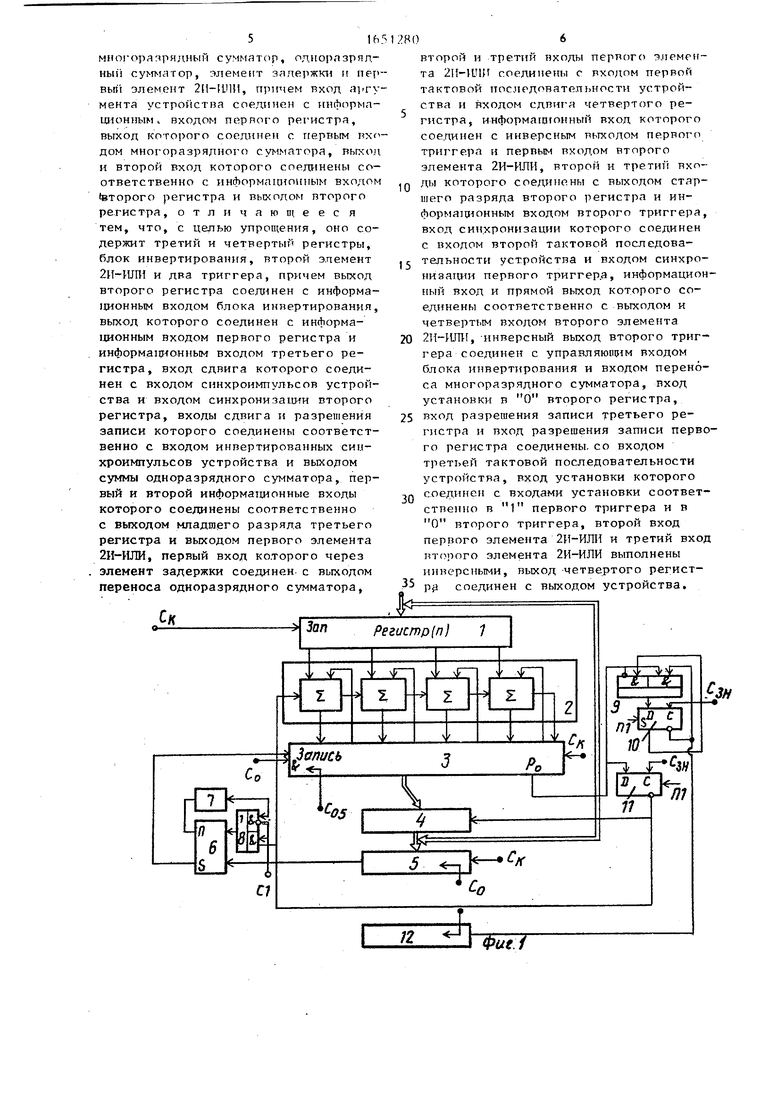

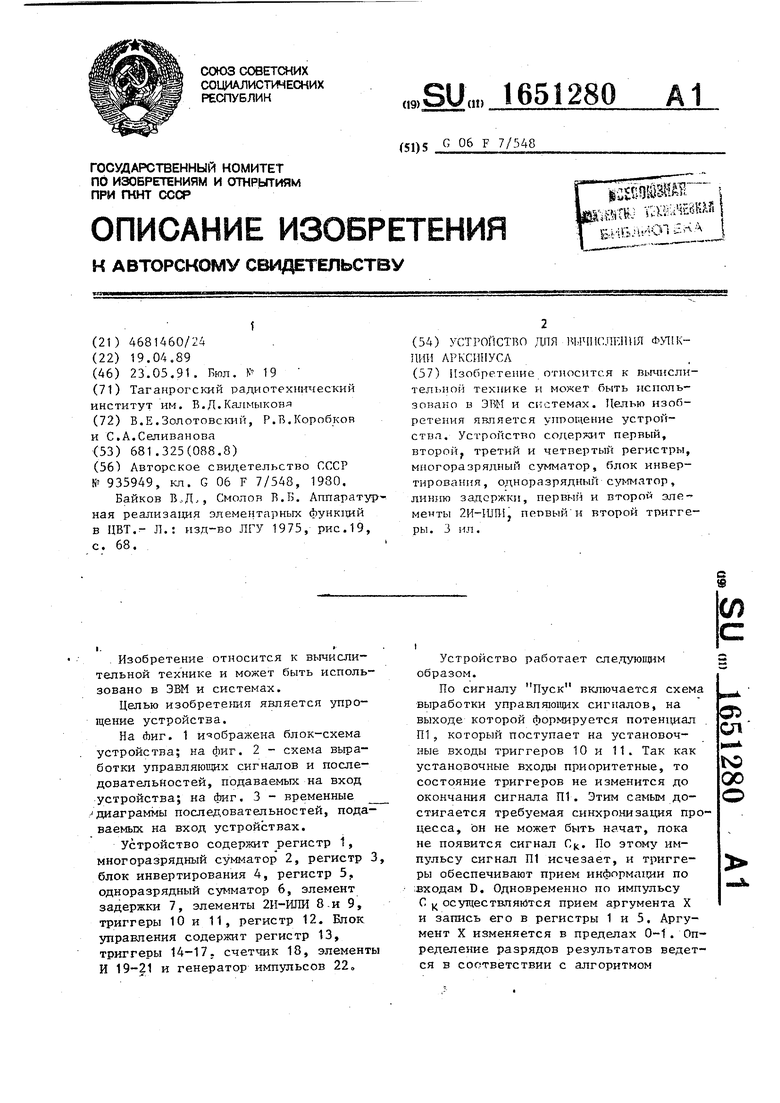

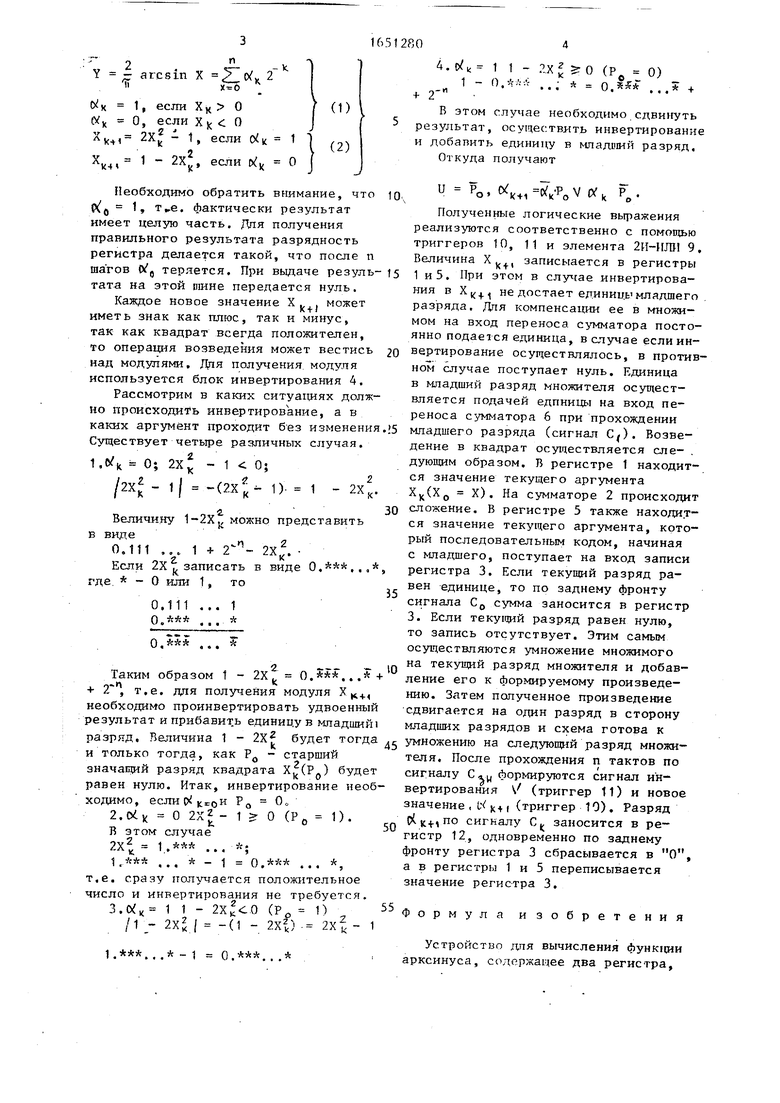

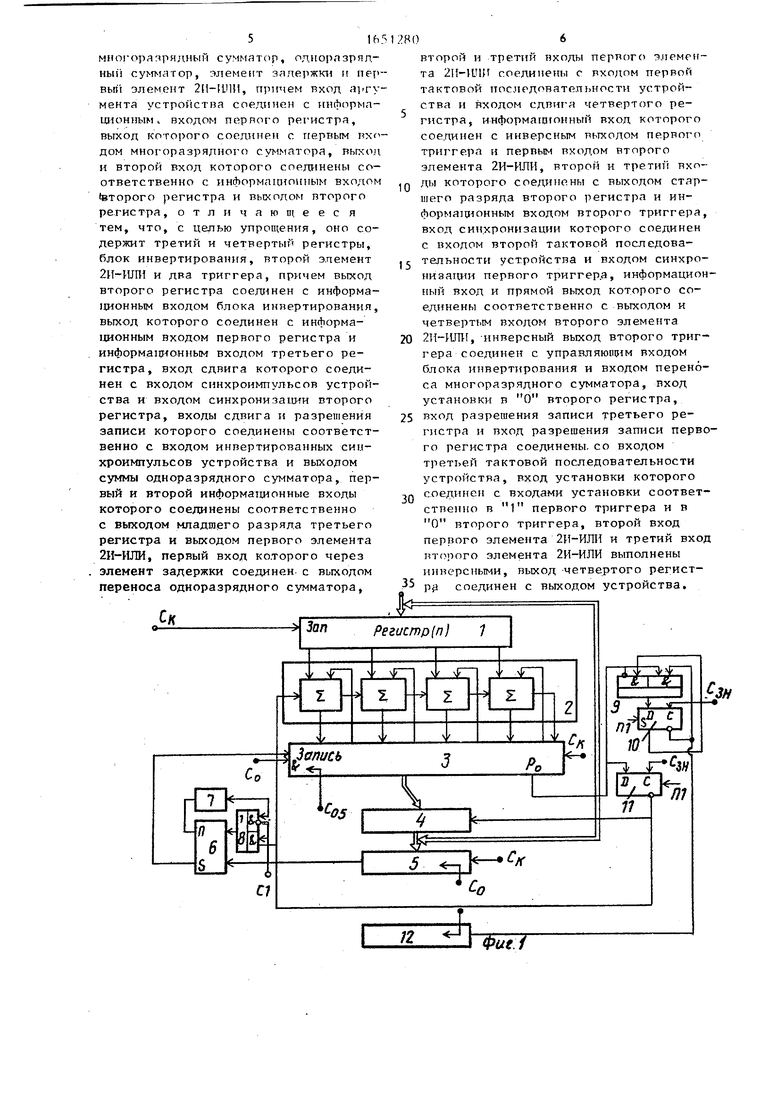

На Лиг. 1 изображена блок-схема устройства; на фиг. 2 - схема выработки управляющих сигналов и последовательностей, подаваемых на вход устройства; на фиг. 3 - временные диаграммы последовательностей, подаваемых на вход устройствах.

Устройство содержит регистр 1, многоразрядный сумматор 2, регистр 3, блок инвертирования 4, регистр 5. одноразрядный сумматор 6, элемент задержки 7, элементы 2Н-ШИ 8.и 9, триггеры 10 и 11, регистр 12. Блок управления содержит регистр 13, триггеры 14-17. счетчик 18, элементы И 19-21 и генератор импульсов 22„

Устройство работает следующим образом.

По сигналу Пуск включается схема выработки управляющих сигналов, на выходе которой формируется потенциал П1, который поступает на установочные входы триггеров 10 и 11. Так как установочные входы приоритетные, то состояние триггеров не изменится до окончания сигнала П1. Этим самым достигается требуемая синхронизация процесса, он не может быть начат, пока не появится сигнал С«. По этому импульсу сигнал П1 исчезает, и триггеры обеспечивают прием информации по входам D. Одновременно по импульсу С у, осуществляется прием аргумента X и запись его в регистры 1 и 5. Аргумент X изменяется в пределах 0-1. Определение разрядов результатов ведется в соответствии с алгоритмом

OS

or

tc

оо о

- a re в in X

n

z

- Sc.

tfK 1, если Хк О (Ук Os если Xk 0 Xk-H 2X - 1, если

XK4, 1 - 2X. если

4. 1 1 - 2X 2 О (Р 0)

„ 1 - 0. ..; 4

4- 2

В этом случае необходимо сдвинуть результат, осуществить инвертирование и добавить единицу в младший разряд.

Откуда получают

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и системах. Целью изобретения является упрощение устройства. Устройство содержит первый, второй третий и четвертый регистры, многоразрядный сумматор, блок инвертирования, одноразрядный сумматор, линию задержки, первый и второй элементы 2И-Ilffllj пепвый и второй триггеры. 3 ил.

Необходимо обратить внимание, что 1, т.,е. фактически результат имеет целую часть. Для получения правильного результата разрядность регистра делается такой, что после п шагов W0 теряется. При выдаче резуль тата на этой пине передается нуль.

Каждое новое значение Х . может иметь знак как плюс, так и минус, так как квадрат всегда положителен, то операция возведения может вестись над модулями. Для получения модуля используется блок инвертирования 4.

Рассмотрим в каких ситуациях должно происходить инвертирование, а в

каких аргумент проходит без изменения.5 младшего разряда (сигнал С(). ВозвеСуществует четыре различных случая. 2

0; .2

2Х,

/zxj- 1) --ml- о.. 1 Величину 1-2Xj,, можно представить

в виде

0.111 ... 1 + 2Х.

Если 2Х записать в виде 0. .,,, где - О или 1, то

дение в квадрат осуществляется еле- . дующим образом. В регистре 1 находится значение текущего аргумента ХК(Х0 X). На сумматоре 2 происходит 30 сложение. В регистре 5 также находится значение текущего аргумента, который последовательным кодом, начиная с младшего, поступает на вход записи регистра 3. Если текущий разряд равен единице, то по заднему фронту сигнала С0 сумма заносится в регистр 3. Если текущий разряд равен нулю, то запись отсутствует. Этим самым осуществляются умножение множимого на текущий разряд множителя и добавление его к формируемому произведению. Затем полученное произведение сдвигается на один разряд в сторону младших разрядов и схема готова к

0.111 0.

1 А

О,

Таким образом 1 - 2Х,, 0.. .. +

- МК

, т.е. для получения модуля X

к-и

г .

дение в квадрат осуществляется еле- . дующим образом. В регистре 1 находит ся значение текущего аргумента ХК(Х0 X). На сумматоре 2 происходи 30 сложение. В регистре 5 также находится значение текущего аргумента, кото рый последовательным кодом, начиная с младшего, поступает на вход записи регистра 3. Если текущий разряд равен единице, то по заднему фронту сигнала С0 сумма заносится в регистр 3. Если текущий разряд равен нулю, то запись отсутствует. Этим самым осуществляются умножение множимого на текущий разряд множителя и добавление его к формируемому произведению. Затем полученное произведение сдвигается на один разряд в сторону младших разрядов и схема готова к

необходимо проинвертировать удвоенный

результат и прибавить единицу в младший

разряд. Величина 1 - 2хЈ будет тогда 45 умножению на следующий разряд множии только тогда, как Р0 - старшийтеля. После прохождения п тактов по

значащий разряд квадрата Х(Р0) будет

равен нулю. Итак, инвертирование необсигналу формируются сигнал ин-

вертирования (триггер 11) и новое значение , Itfx+f (триггер 10). Разряд р( к-нпо сигналу С заносится в регистр 12, одновременно по заднему фронту регистра 3 сбрасывается в О а в регистры 1 и 5 переписывается значение регистра 3.

ходимо, если(ХКс0и Р0 0

В этом случае

2

1

О (Pft 1)

2Х 1. ... ;

З.СХ„ 1 1 - 2хЈсО (Pfl 1)

2ХЈ | -О - 2X0

f.V

2X2kU

РО, к-м V (X,

k о

Полученные логические выражения реализуются соответственно с помощью триггеров 10, 11 и элемента 2И-НЛИ 9. Величина Xk + l записыается в регистры 1 и 5. При этом в случае инвертирования в Х, не достает единиць младшего разряда. Для компенсации ее в множимом на вход переноса сумматора постоянно подается единица, в случае если инвертирование осуществлялось, в противном случае поступает нуль. Единица в младший разряд множителя осуществляется подачей едпницы на вход переноса сумматора 6 при прохождении

дение в квадрат осуществляется еле- . дующим образом. В регистре 1 находится значение текущего аргумента ХК(Х0 X). На сумматоре 2 происходит 0 сложение. В регистре 5 также находится значение текущего аргумента, который последовательным кодом, начиная с младшего, поступает на вход записи регистра 3. Если текущий разряд равен единице, то по заднему фронту сигнала С0 сумма заносится в регистр 3. Если текущий разряд равен нулю, то запись отсутствует. Этим самым осуществляются умножение множимого на текущий разряд множителя и добавление его к формируемому произведению. Затем полученное произведение сдвигается на один разряд в сторону младших разрядов и схема готова к

Ю

45 умножению на следующий разряд множисигналу формируются сигнал ин-

вертирования (триггер 11) и новое значение , Itfx+f (триггер 10). Разряд р( к-нпо сигналу С заносится в регистр 12, одновременно по заднему фронту регистра 3 сбрасывается в О, а в регистры 1 и 5 переписывается значение регистра 3.

55

Формула изобретения

Устройство для вычисления функции арксинуса, содержащее два регистра,

516

многорачридный сумматор, одноразряп- ный сумматор, элемент задержки и первый элемент 2И-НЧИ, причем вход аргумента устройства соединен с информационным входом первого регистра, выход которого соединен с первым входом многоразрядного сумматора, выход и второй вход которого соединены соответственно с информационным входом (второго регистра и выходом второго регистра, отличающееся тем, что, с целью упрощения, оно содержит третий и четвертый регистры, блок инвертирования, второй эпемент 2И-ИЛИ и два триггера, причем выход второго регистра соединен с информационным входом блока инвертирования, выход которого соединен с информационным входом первого регистра и информационным входом третьего регистра, вход сдвига которого соединен с входом синхроимпульсов устройства и входом синхронизации второго регистра, входы сдвига и разрешения записи которого соединены соответственно с входом инвертированных синхроимпульсов устройства и выходом суммы одноразрядного сумматора, первый и второй информационные входы которого соединены соответственно с выходом младшего разряда третьего регистра и выходом первого элемента 2И-ИЛИ, первый вход которого через элемент задержки соединен с выходом переноса одноразрядного сумматора,

С

5

яоб

второй и третий входы первого элемента 2И-Ш1П соединены с входом первой тактовой последоватрпьности устройства и входом сдвига четвертого регистра, информационный вход которого соединен с инверсным выходом первого триггера и первым входом второго элемента 2И-ИЛИ, второй и третий входы которого соединены с выходом старшего разряда второго регистра и информационным входом второго триггера, вход синхронизации которого соединен с входом второй тактовой последовательности устройства и входом синхронизации первого триггера, информационный вход и прямой выход которого соединены соответственно с выходом и четвертым входом второго элемента 2И-ШШ, инверсный выход второго триггера соединен с управляюгцим входом блока инвертирования и входом переноса многоразрядного сумматора, вход установки в О второго регистра, вход разрешения записи третьего регистра и вход разрешения записи первого регистра соединены, со входом третьей тактовой последовательности устройства, вход установки которого соединен с входами установки соответ м первого триггера и в второго триггера, второй вход первого элемента 2И-ИЛИ и третий вход второго элемента 2И-ИЛИ выполнены инверсными, выход четвертого регистра соединен с выходом устройства.

5

0

стпенно в О

.f

Пуск

Ш fflffiffiffiffifflfflfflfflffl fflffiffl.

%L

Ш

ҐfflL

УШ

YZZk

я

О

Cos

4%%ШШ%4%Ш1Ш

У&ШШЧ%(

Остано8 /7{/ек Фиг.1

Ш

УШ

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Байков ВоД,, Смолов Б.Б | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

Авторы

Даты

1991-05-23—Публикация

1989-04-19—Подача