Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических устройствах.

Целью изобретения является сокращение затрат оборудования при делении делимого меньшего делителя по абсолютной величине.

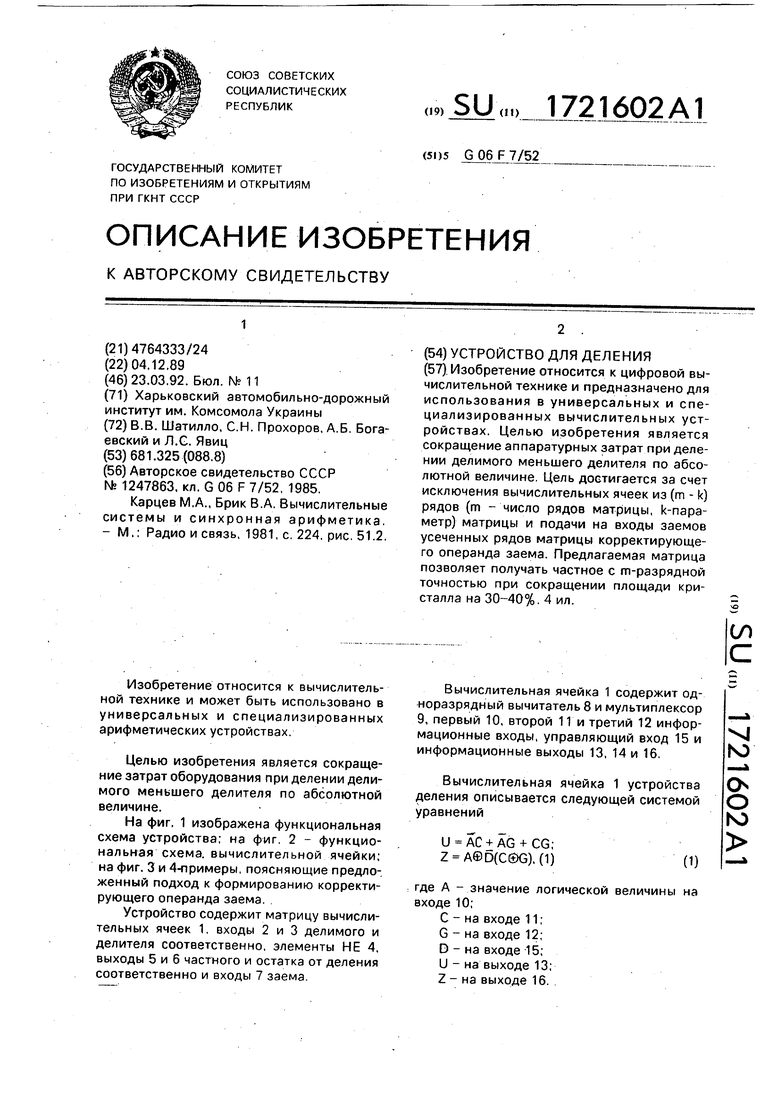

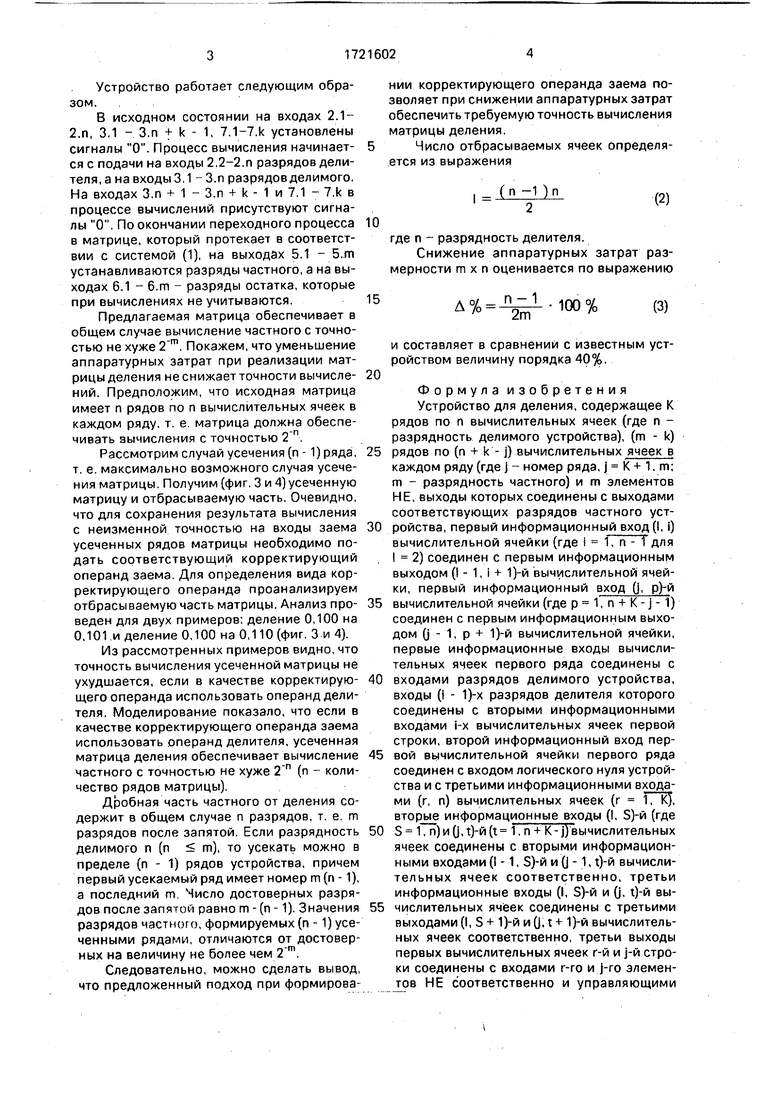

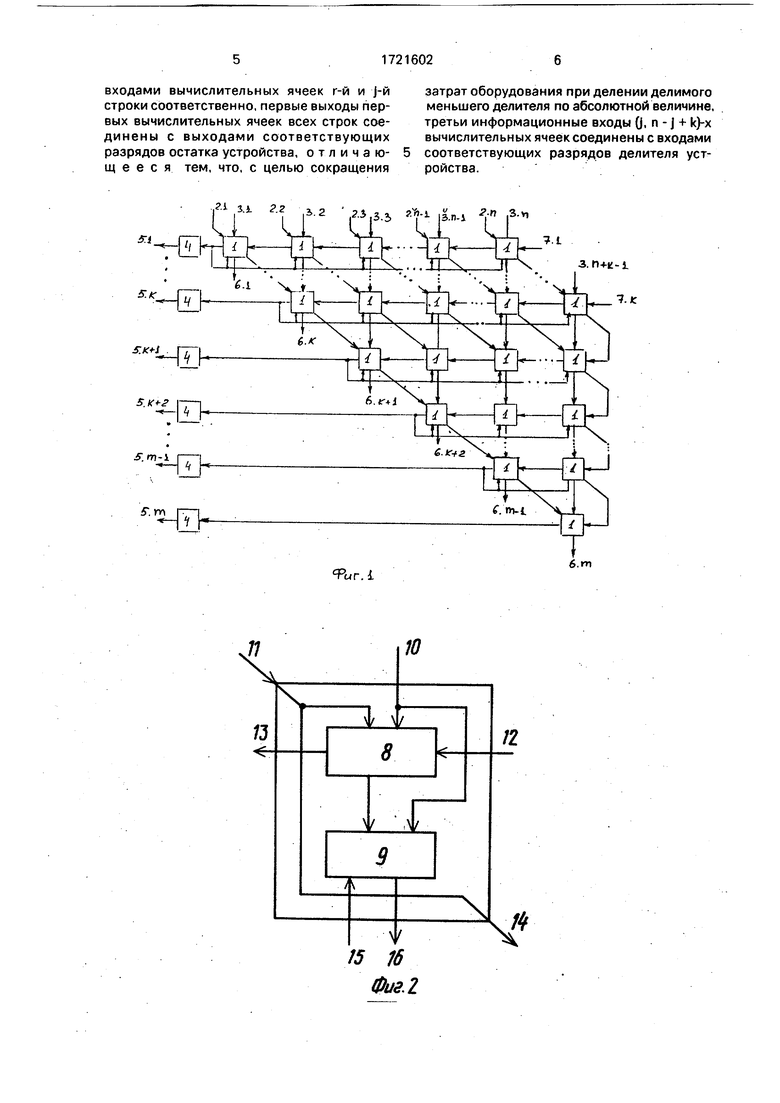

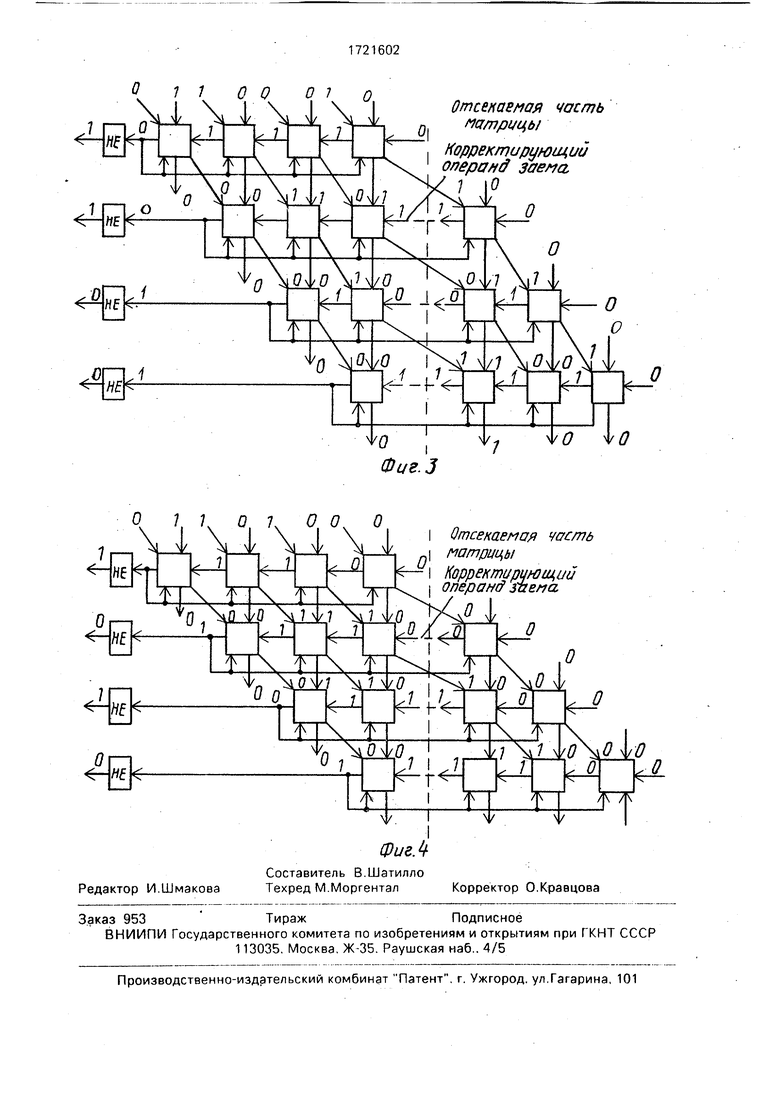

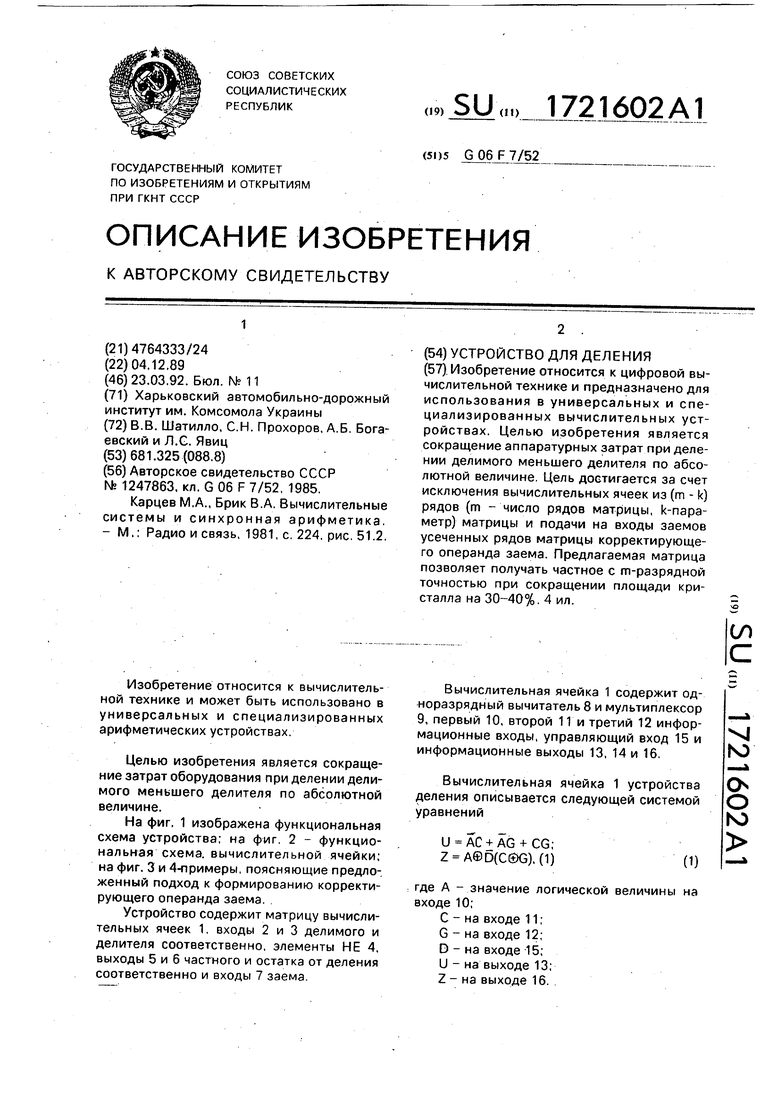

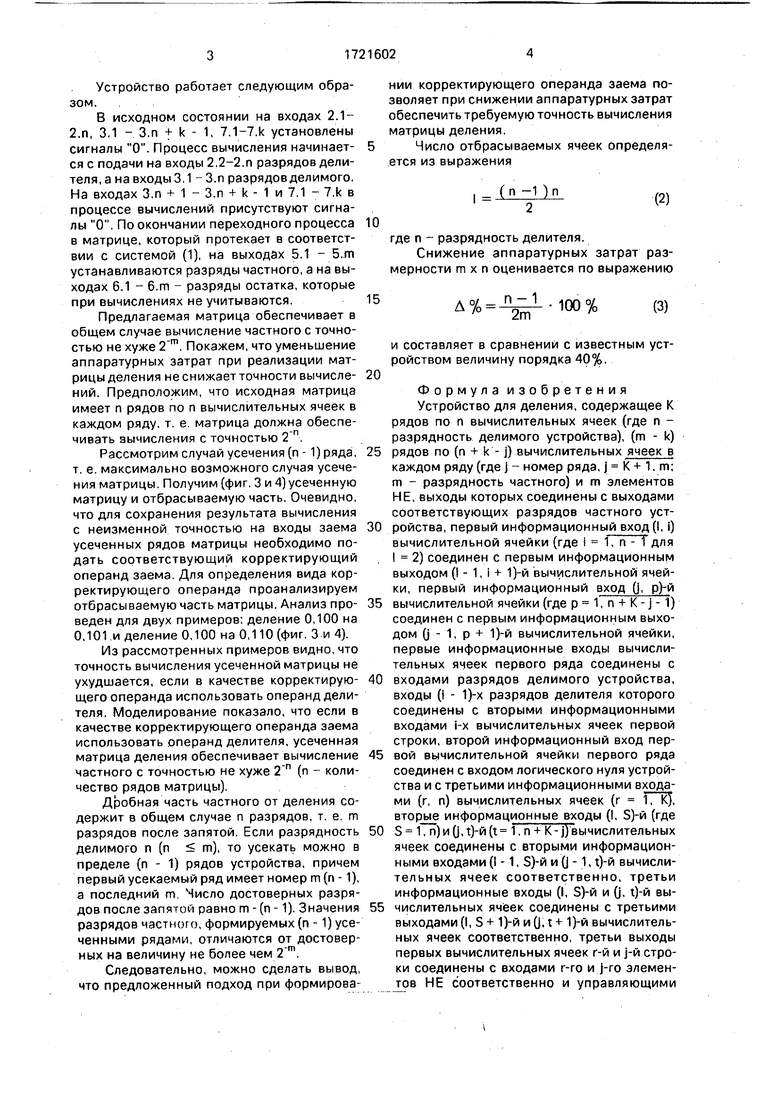

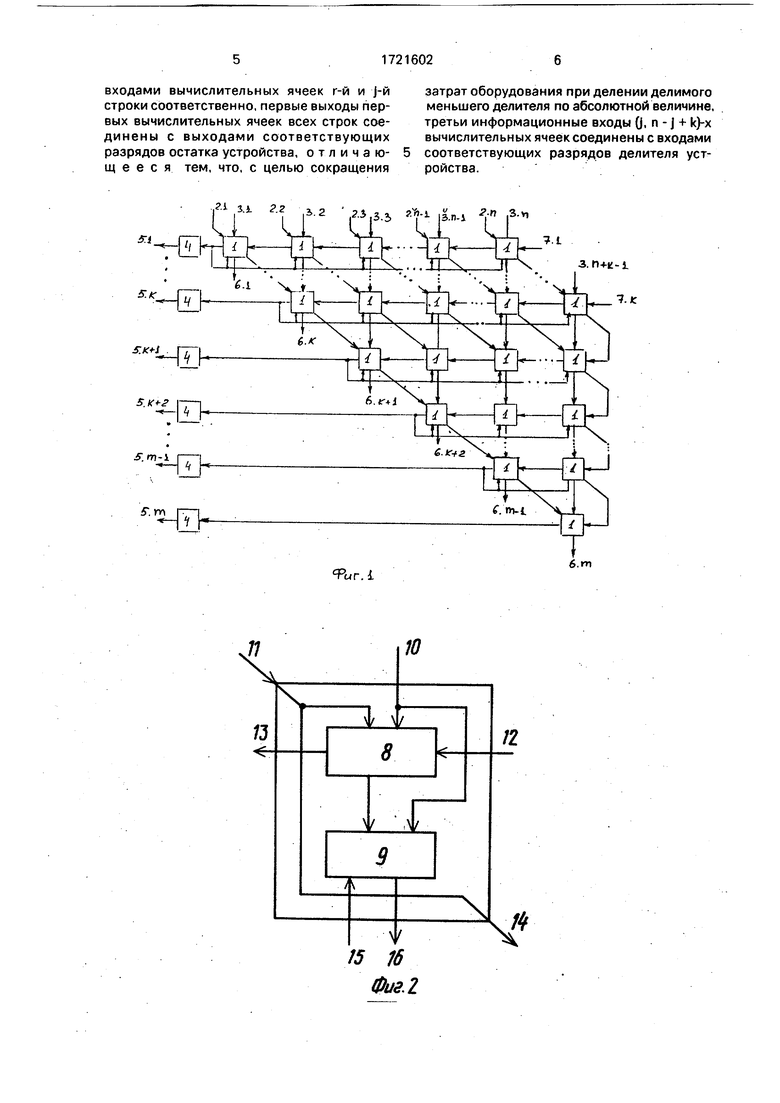

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема, вычислительной ячейки; на фиг. 3 и 4-примеры, поясняющие предложенный подход к формированию корректирующего операнда заема.

Устройство содержит матрицу вычислительных ячеек 1. входы 2 и 3 делимого и делителя соответственно, элементы НЕ 4, выходы 5 и 6 частного и остатка от деления соответственно и входы 7 заема.

Вычислительная ячейка 1 содержит одноразрядный вычитатель 8 и мультиплексор 9, первый 10, второй 11 и третий 12 информационные входы, управляющий вход 15 и информационные выходы 13, 14 и 16.

Вычислительная ячейка 1 устройства деления описывается следующей системой уравнений

U AC + AG + CG; Z A©D(C@G), (1)

(1)

VI

ГО

сь о ю

где А - значение логической величины на входе 10;

С - на входе 11;

G - на входе 12;

D - на входе 15;

U - на выходе 13;

2- на выходе 16.

Устройство работает следующим образом.

В исходном состоянии на входах 2.1- 2.п, 3.1 - З.п + k - 1, 7.1-7.k установлены сигналы О. Процесс вычисления начинается с подачи на входы 2.2-2.П разрядов делителя, а на входы 3.1 -З.п разрядов делимого. На входах З.п + 1 - З.п + k - 1 и 7.1 - 7,k в процессе вычислений присутствуют сигналы О. По окончании переходного процесса в матрице, который протекает в соответствии с системой (1), на выходах 5.1 - 5,т устанавливаются разряды частного, а на выходах 6.1 - б.пл - разряды остатка, которые при вычислениях не учитываются.

Предлагаемая матрица обеспечивает в общем случае вычисление частного с точностью не хуже . Покажем, что уменьшение аппаратурных затрат при реализации матрицы деления не снижает точности вычислений. Предположим, что исходная матрица имеет п рядов по п вычислительных ячеек в каждом ряду. т. е. матрица должна обеспечивать вычисления с точностью 2 п.

Рассмотрим случай усечения (п -1) ряда, т. е. максимально возможного случая усечения матрицы. Получим (фиг. 3 и 4) усеченную матрицу и отбрасываемую часть. Очевидно, что для сохранения результата вычисления с неизменной точностью на входы заема усеченных рядов матрицы необходимо подать соответствующий корректирующий операнд заема. Для определения вида корректирующего операнда проанализируем отбрасываемую часть матрицы. Анализ проведен для двух примеров: деление 0,100 на 0.101 .и деление 0,100 на 0,110 (фиг. 3 и 4).

Из рассмотренных примеров видно, что точность вычисления усеченной матрицы не ухудшается, если в качестве корректирующего операнда использовать операнд делителя. Моделирование показало, что если в качестве корректирующего операнда заема использовать операнд делителя, усеченная матрица деления обеспечивает вычисление частного с точностью не хуже (п - количество рядов матрицы).

Дробная часть частного от деления содержит в общем случае п разрядов, т. е. m разрядов после запятой. Если разрядность делимого п (п т), то усекать можно в пределе (п - 1) рядов устройства, причем первый усекаемый ряд имеет номер m (п -1), а последний т. Число достоверных разрядов после запятой равно m - (п -1). Значения разрядов частного, формируемых (п -1) усеченными рядами, отличаются от достоверных на величину не более чем .

Следовательно, можно сделать вывод, что предложенный подход при формировании корректирующего операнда заема позволяет при снижении аппаратурных затрат обеспечить требуемую точность вычисления матрицы деления.

5Число отбрасываемых ячеек определяется из выражения

10

. (п-1)п 2

(2)

где п - разрядность делителя.

Снижение аппаратурных затрат размерности m x n оценивается по выражению

А% - --100%(3)

0

5

0

5

0

5

0

5

и составляет в сравнении с известным устройством величину порядка 40%.

Формула изобретения Устройство для деления, содержащее К рядов по п вычислительных ячеек (где п - разрядность делимого устройства), (m - k) рядов по (п + k - j) вычислительных ячеек в каждом ряду (где - номер ряда, j К + 1, т; т - разрядность частного) и m элементов НЕ, выходы которых соединены с выходами соответствующих разрядов частного устройства, первый информационный вход (I, i) вычислительной ячейки (где I 1, п - Т для I 2) соединен с первым информационным выходом (1-1,1+ 1)-й вычислительной ячейки, первый информационный вход (j, р)-й вычислительной ячейки (где р 1, п + К - j -1) соединен с первым информационным выходом 0 - 1. Р + 1)-й вычислительной ячейки, первые информационные входы вычислительных ячеек первого ряда соединены с входами разрядов делимого устройства, входы (i - 1)-х разрядов делителя которого соединены с вторыми информационными входами i-x вычислительных ячеек первой строки, второй информационный вход первой вычислительной ячейки первого ряда соединен с входом логического нуля устройства и с третьими информационными входами (г, п) вычислительных ячеек (г if, K}, вторые информационные входы (I, 5)-й (где 3 1, п)и()д)-й(г 1 п + К - j) вычислительных ячеек соединены с вторыми информационными входами (I -1, 5)-й и (j -1, т,)-й вычисли- тельных ячеек соответственно, третьи информационные входы (I, 3)-й и (j. tj-й вычислительных ячеек соединены с третьими выходами (I, S + 1)-й и (j, t + 1)-й вычислительных ячеек соответственно, третьи выходы первых вычислительных ячеек r-й и j-й строки соединены с входами г-го и j-ro элемен- JTOB НЕ соответственно и управляющими

затрат оборудования при делении делимого меньшего делителя по абсолютной величине.

входами вычислительных ячеек r-й и j-й строки соответственно, первые выходы первых вычислительных ячеек всех строк сое-третьи информационные входы 0. п - j + k)-x динены с выходами соответствующихвычислительных ячеек соединены с входами разрядов остатка устройства, отличаю-5 соответствующих разрядов делителя уст- щ е е с я тем, что, с целью сокращенияройства.

затрат оборудования при делении делимого меньшего делителя по абсолютной величине.

третьи информационные входы 0. п - j + k)-x вычислительных ячеек соединены с входами соответствующих разрядов делителя уст- ройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1989 |

|

SU1667057A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Мультиконвейерный делитель | 1988 |

|

SU1587499A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1988 |

|

SU1635183A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах. Целью изобретения является сокращение аппаратурных затрат при делении делимого меньшего делителя по абсолютной величине. Цель достигается за счет исключения вычислительных ячеек из (т - к) рядов (т - число рядов матрицы, к-пара- метр) матрицы и подачи на входы заемов усеченных рядов матрицы корректирующего операнда заема. Предлагаемая матрица позволяет получать частное с т-разрядной точностью при сокращении площади кристалла на 30-40%. 4 ил.

, 3.J. 2.Z

.2 2.5,3.5 2%-l i&n.j гл 3.V,

С Г U СГ Т Г ГГ „

Pur.i

б.гп

О 11 00 01 о

VI

0

U 41 М Vi.

Отсекаемая часть патрщы

Корректирующий операнд заепа,

1 0 А О

-

о

Отсекаемая часть питрщы

Корректирующий операнд тепа

О

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| - М.: Радио и связь, 1981, с | |||

| Фотореле для аппарата, служащего для передачи на расстояние изображений | 1920 |

|

SU224A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1992-03-23—Публикация

1989-12-04—Подача