Изобретение относится к вычислительной технике и обеспечивает построение микропрограммных устройств управления.

Целью изобретения является сокращение аппаратурных затрат за счет уменьшения емкости блока памяти.

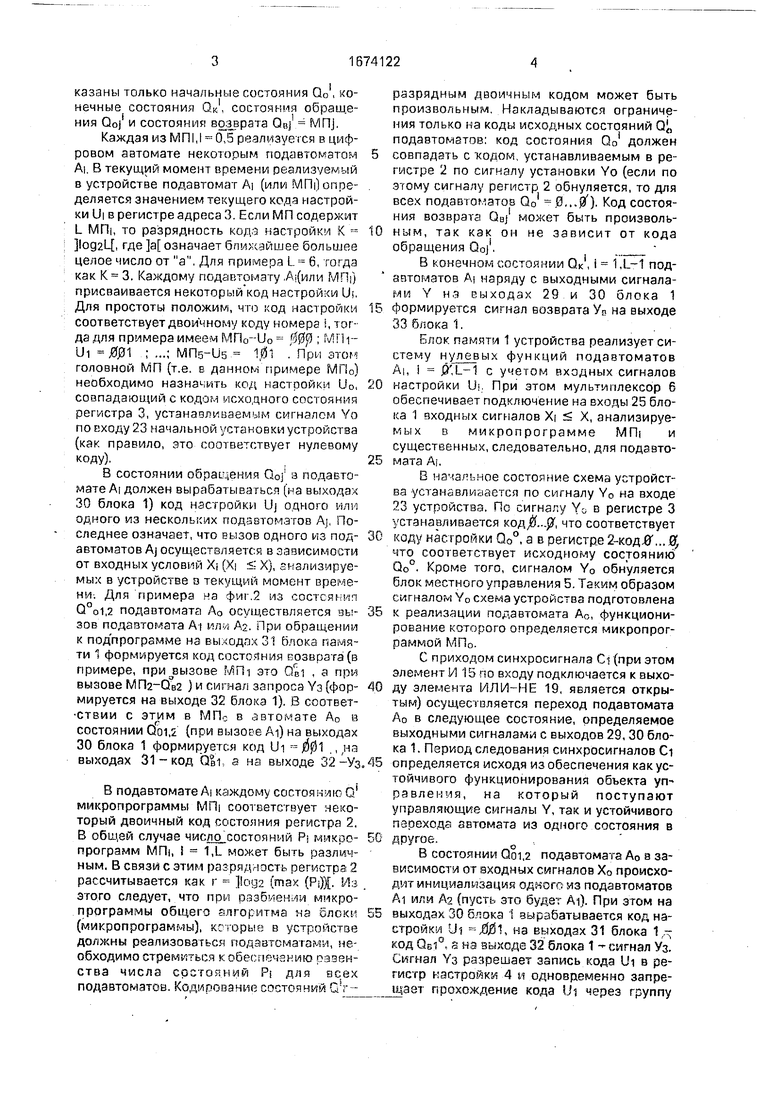

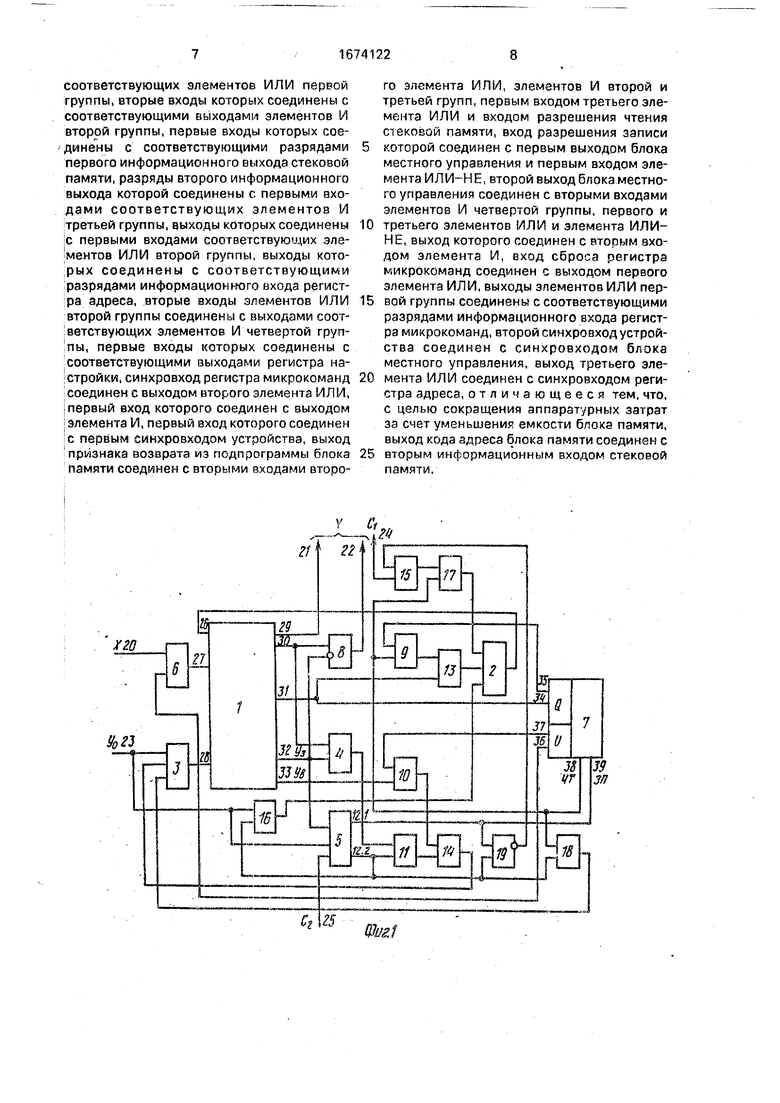

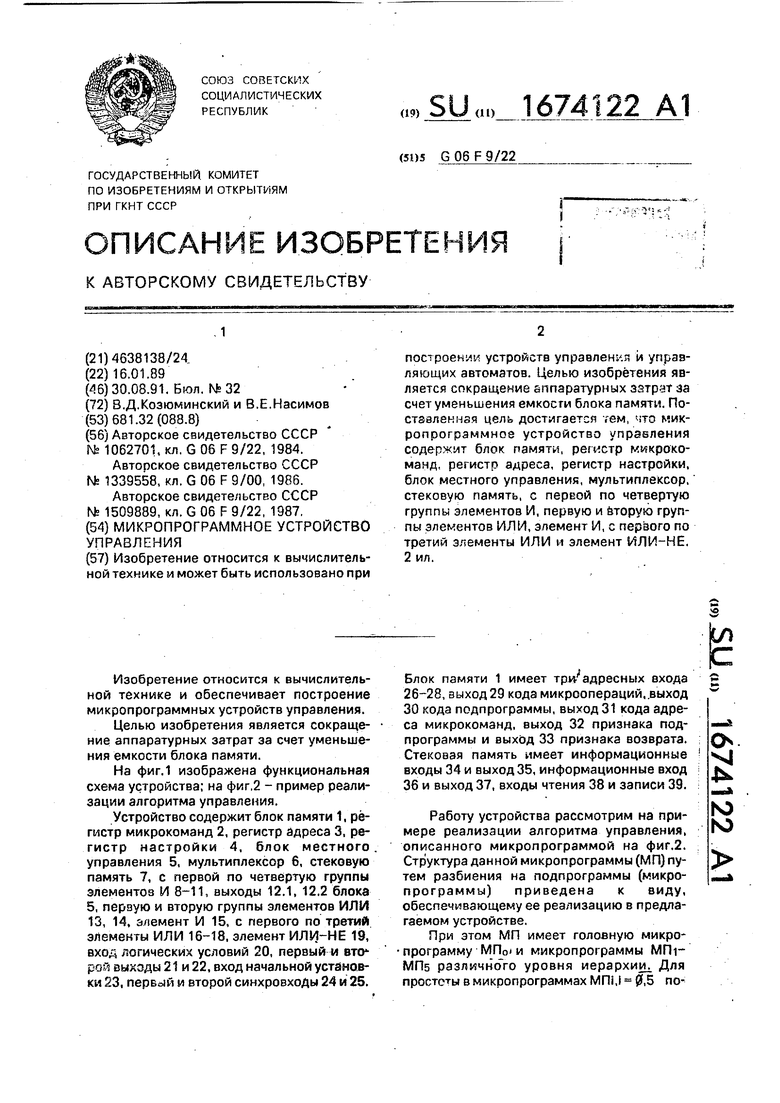

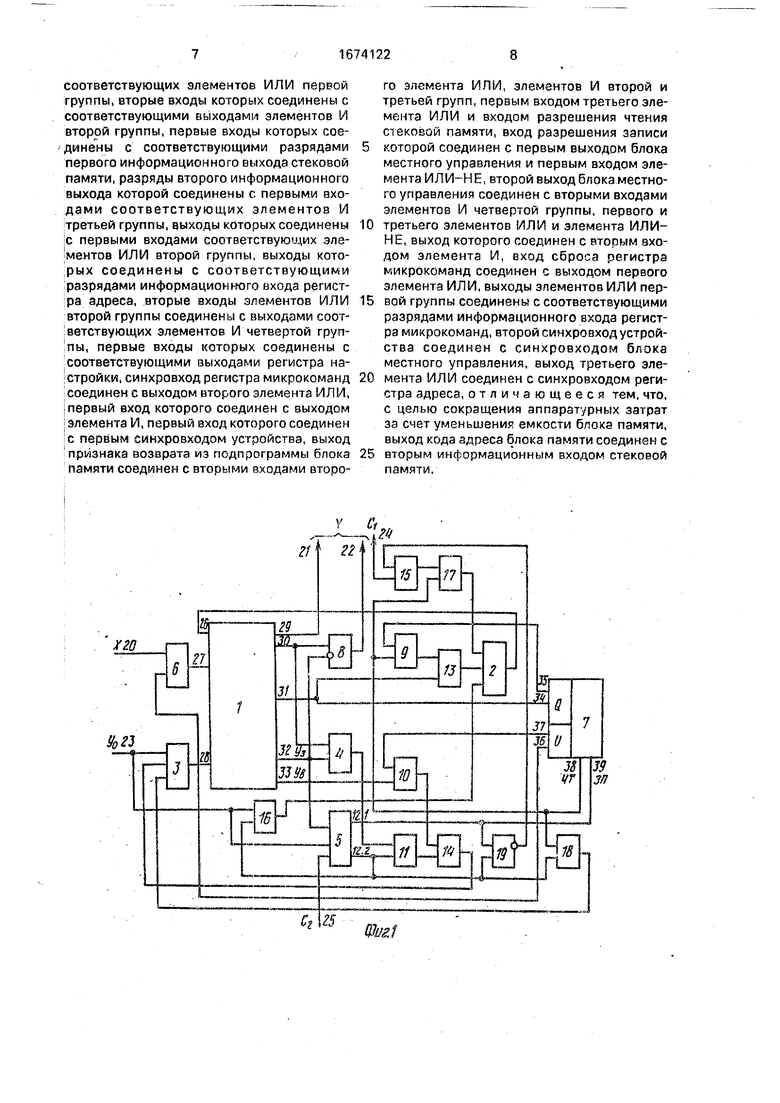

На фиг.1 изображена функциональная схема устройства; на фиг,2 - пример реализации алгоритма управления.

Устройство содержит блок памяти 1, регистр микрокоманд 2, регистр адреса 3, регистр настройки 4, блок местного. управления 5, мультиплексор 6, стековую память 7, с первой по четвертую группы элементов И 8-11, выходы 12.1, 12.2 блока 5, первую и вторую группы элементов ИЛИ 13, 14, энемент И 15. с первого по третий элементы ИЛИ 16-18, элемент ИЛИ-НЕ 19, вхо логических условий 20, первый и вто р о сыходы 21 и 22, вход начальной установки 23, первый и второй синхровходы 24 и 25.

Блок памяти 1 имеет три-11 адресных входа 26-28, выход 29 кода микроопераций,.выход 30 кода подпрограммы, выход 31 кода адреса микрокоманд, выход 32 признака подпрограммы и выход 33 признака возврата. Стековая память имеет информационные входы 34 и выход 35, информационные вход 36 и выход 37, входы чтения 38 и записи 39.

Работу устройства рассмотрим на примере реализации алгоритма управления, описанного микропрограммой на фиг.2. Структура данной микропрограммы (МП) путем разбиения на подпрограммы (микропрограммы) приведена к виду, обеспечивающему ее реализацию в предлагаемом устройстве.

При этом МП имеет головную микро программу МП0 и микропрограммы MfliМПб различного уровня иерархии Для

простоты в микропрограммах МП, 0,5 поOv

2

Ю Ю

казаны только начальные состояния Q0 , конечные состояния QK , состояния обращения Qo) и состояния возврата QB МП.

Каждая из МП, 0,5 реализуемы в цифровом автомате некоторым подавтоматом AI. В текущий момент времени реализуемый в устройстве подавтомат AI (или МГЬ) определяется значением текущего кода настройки Ui в регистре адреса 3. Если МП содержит L МП|, то разрядность кода настройки К JlogaU, где а означает ближайшее большое целое число от а. Для примера 1 6, тогда как К 3. Каждому подавтомату А|(или МП|) присваивается некоторый код настройки Ui, Для простоты положим, что код настройки соответствует двоичному коду номера i, тогда для примера имеем МПо-Uo- 00J3; МГН- Ui 001 ; ...; MHs-Us 101 . При этом головной МП (т.е. в данном примере МПо) необходимо назначить код настройки Do, совпадающий с кодом исходного состояния регистра 3, устанавливаемым сигналом Yo по сходу 23 начальной установки устройства (как правило, это соответствует нулевому коду).

В состоянии обращения Q0j в подавтомате AI должен вырабатываться (на выходах 30 блока 1) код настройки DJ одного или одного из нескольких подавтоматов AJ Последнее означает, что вызов одного из подавтоматов AJ осуществляется в зависимости от входных условий Xj (Xi X), анализируемых в устройстве D текущий момент времени. Для примера на фиг.2 из состоянии Q°oi,2 подавтомата А0 осуществляется вызов подавтомата Ач или А2, При обращении к подпрограмме на выходах 31 блока памяти 1 формируется код состояния возврата (в примере, при вызове МП1 это Ов1 , а при вызове МП2-сГв2 )и сигнал запроса Уз (формируется на выходе 32 блока 1). В соответствии с этим в МП0 в автомате А0 в состоянии Qoi,2 (при вызове AI) на выходах 30 блока 1 формируется код Ui $01 , на выходах 31-код 6в1, а на выходе 32-Уз.

В подавтомате А каждому состоянию Q микропрограммы МП; соответствует некоторый двоичный код состояния регистра 2, В общей случае числр состояний PI микропрограмм МП|, I 1.L может быть различным. В связи с этим разрядность регистра 2 рассчитывается как г log2 (max (РДО. Из этого следует, что при разбиении микропрограммы общего алгоритма на блоки (микропрограммы), которые в устройстве должны реализоваться подавтоматами, необходимо стремиться к обеспечению равенства числа состояний PI для всех подавтоматов Кодирование состояний G r разрядным двоичным кодом может быть произвольным. Накладываются ограничения только на коды исходных состояний Q« подавтоматов: код состояния Q0 должен

совпадать с кодом устанавливаемым в регистре 2 по сигналу установки Yo (если по этому сигналу регистр 2 обнуляется, то для всех подавтоматов Q0 0.,.). Код состояния возврата QBj может быть произволь0 ным, так как он не зависит от кода

обращения Q0j .

В коночном состоянии QK , i 1.L-1 подавтоматов AI наряду с выходными сигналами У ня оыходах 29 и 30 блока 1

5 формируется сигнал возврата УР на выходе 33 блока 1,

Елок памяти 1 устройства реализует систему нулевых функций подавтоматов AI, i - $ ,L-1 с учетом входных сигналов

0 настройки DI При этом мультиплексор 6 обеспечивает подключение на входы 25 блока 1 пходных сигналов Х| X, энализируе- мых в микропрограмме МП| и существенных, следовательно, для подавто5 мата AI.

В чачзгм-.ное состояние схема устройства устанавливается по сигналу Y0 на входе 23 устройства. По сигналу Y0 в регистре 3 устанавливается к од Д..{У, что соответствует

0 коду настройки Q0°, а в регистре 2-кодЯ... 0, что соответствует исходному состоянию Q0°. Кроме того, сигналом Y0 обнуляется блок местного управления 5. Таким образом сигналом Yo схема устройства подготовлена

5 к реализации подавтомата А0, функционирование которого определяется микропрограммой МП0.

С приходом синхросигнала Ci (при этом элемент И 15 по входу подключается к выхо0 ду элемента ИЛИ-НЕ 19, является открытым) осущесюляется переход подавтомата АО в следующее состояние, определяемое выходными сигналами с выходов 29, 30 блока 1. Период следования синхросигналов Ci

5 определяется исходя из обеспечения как устойчивого функционирования объекта управления, на который поступают управляющие сигналы Y, так и устойчивого пэпехода автомата из одного состояния в

0 другое.

В состоянии Qoi,2 подавтомата А0 в зависимости от входных сигналов Х0 происходит инициализация одного из подавтоматов AI или А2 (пусть это будет AI). При этом на

5 выходах 30 блока еырабативается код на- стройки Ui --.0,01, на выходах 31 блока 1 -- код QB1°, а на выходе 32 блока 1 - сигнал УЗ. Сигнал УЗ разрешает запись кода Ui в регистр настройки 4 и одновременно запрещает прохождение кода Ui через группу

элементов И 8 на выход устройства 22, Тем самым исключается влияние выходных сигналов 30 блока 1 при формировании кода настройки на объект управления. При поступлении сигнала Уз на вход местного блока управления 5 на первом выходе блока 5 вырабатывается единичный потенциал. Этим сигналом по входу записи 39 стековой памяти 7 будет разрешена запись в стековую память кода состояния QB1° с выхода 31,а по входам 36 - кода настрой- ки из регистру 3. Одновременно по цепи элементов ИЛИ-НЕ 19 и А 15 блокируется прохождение очередного синхросигнала Ci на синуровход регистра 2 (тем самым блокируется возможность перо- хода подавтомата А0 ч другое состояние). С приходом синхросигнала С2, ко горый поступает на синхровход местного блока управления 5, единичный потенциал сбрасывается на первом выходе блока 5 и устанавливается на втором. Единичный сиг- нап со второго выхода блока 5 осуществляет по цепи элемента ИЛИ 16 обнуление регистра 2; по цепи элементов И 11 подключение выходов регистра 4 к информационным входам регистра 3; по цепи элемента ИЛИ 18 разрешается перезапись кода настройки Ui из регистра 4 в регистр 3. В результате в регистр 3 будет записан код настройки Ui J0F1. Схема устройства готоза к реализации подавтомата AL С приходом очередного синхросигнала С2 на втором выходе блока местного управления 5 установится нулевой потенциал, в результате чего положительным потенциалом с выхода элемента ИЛИ-НЕ 19 будет разрешено прохождение синхросигналов Ci на синхровход регистра 2. В дальнейшем устройство реализует подавтомат AL

Аналогичным образом в состоянии Q04.5 подавтомата At осуществляется инициализация, например, подавтомата As. При этом на выходе 30 блока 1 формируется код Us 1,01 , а на выходе 31 - код состояния возврата Ов51 или As. Состояние Овб1 и код Ui J0jJ1 запишутся в первую ячейку стековой памяти 7, а коды Uo /Oj3j2f и QB1° перезапишутся во вторую ячейку стековой памяти. Число ячеек стековой памяти 7 кодом состояний и настроек возврата определяется глубиной вложенности (или обращений) микропрограмм алгоритма управления. Например, глубина обращений, а следовательно, число ячеек узла памяти для. изображенной ча фиг.2 микропрограммы равно дьум.

I конечном состоянии функционирования подавтомата As (в состоянии QK5 микропрограммы МПб) на выходе 33 блока 1 будет .

сформирован сигнал YB. Этим сигналом информационные выходы 35 и 37 стековой памяти 7 бурут подключены к информационным входам соответственно 5 регистра 2 и регистра 3. Этим же сигналом будет разрешена запись с выхода стековой памяти в регистры 2 и 3. Задним фронтом сигнала YB будет осуществлена перезапись содержимого ячеек стековой памяти, Таким

0 образом, в регистр 2 будет записан код Ов51 подавтомата AI, а в регистр 3 - код Ui $& . В первую ячейку стековой памяти 7 будут записаны из второй ячейки коды QB1° и U0 0jHQ. В дальней5 шем в устройстве реализуется подавтомат AI Аналогично осуществляется возврат из подавтомата AI в подавтомат А0.

Таким образом, в устройстве реализуется иерархически организованная сеть из L

0 подавтоматов, технически реализуемых на основе одного L-функционального автомата.

Формула изобретения Микропрограммное устройство управ5 ления, содержащее блок памяти, регистр микрокоманд, регистр адреса, регистр настройки, блок месг ного управления, мультиплексор, стековую память, с первой по четвертую группы элементов И, первую и

0 вторую группы злемеитов ИЛИ, элемент И, с первого п& третий элементы ИЛИ и элемент ИЛИ-НЕ, причем вход логических условий устройства соединен с информационным входом мультиплексора,

5 выход которого соединен с первым адресным входом блока памяти, выход кода микроопераций которого соединен с первым выходом микроопераций устройства, выход регистра адреса соединен с управляющим

0 входом мультиплексора, с первым информационным входом стековой памяти и с вторым адресным входом блока памяти, третий адресный вход которого соединен с выходом регистра микрокоманд, а вход началь5 ной установки регистра адреса соединен с одноименным входом блока местного управления, с первым входом первого элемента ИЛИ и с входом начальной установки устройства, второй выход микроопераций

0 которого образуют выходы элементов И первой группы, первые входы которых соединены с выходами кода подпрограммы блока памяти и информационными входами регистра настройки, вход разрешения запи5 си которого соединен с входом задания режима блока местного управления, с .вторыми входами элементов И первой группы и с выходом признака подпрограммы блока памяти, выход кода адреса которого поразрядно соединен с первыми входами

соответствующих элементов ИЛИ первой группы, вторые входы которых соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с соответствующими разрядами первого информационного выхода стековой памяти, разряды второго информационного выхода которой соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с соответствующими разрядами информационного входа регистра адреса, вторые входы элементов ИЛИ второй группы соединены с выходами соответствующих элементов И четвертой группы, первые входы которых соединены с соответствующими выходами регистра настройки, синхровход регистра микрокоманд соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом элемента И, первый вход которого соединен с первым синхровходом устройства, выход признака возврата из подпрограммы блока памяти соединен с вторыми входами второго элемента ИЛИ, элементов И второй и третьей групп, первым входом третьего элемента ИЛИ и входом разрешения чтения стековой памяти, вход разрешения записи которой соединен с первым выходом блока местного управления и первым входом элемента И Л И-Н Е, второй выход блока местного управления соединен с вторыми входами элементов И четвертой группы, первого и третьего элементов ИЛИ и элемента ИЛИ- НЕ, выход которого соединен с вторым входом элемента И, вход сброса регистра микрокоманд соединен с выходом первого элемента ИЛИ, выходы элементов ИЛИ первой группы соединены с соответствующими разрядами информационного входа регистра микрокоманд, второйсинхровходустройства соединен с синхровходом блока местного управления, выход третьего элемента ИЛИ соединен с синхровходом регистра адреса, отличающееся тем, что, с целью сокращения аппаратурных затрат за счет уменьшения емкости блока памяти, выход кода адреса блока памяти соединен с вторым информационным входом стекорой памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1509889A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления и управляющих автоматов. Целью изобретения является сокращение аппаратурных затрат за счет уменьшения емкости блока памяти. Поставленная цель достигается тем, что микропрограммное устройство управления содержит блок памяти, регистр микрокоманд, регистр адреса, регистр настройки, блок местного управления, мультиплексор, стековую память, с первой по четвертую группы элементов И, первую и вторую группы элементов ИЛИ, элемент И, с первого по третий элементы ИЛИ и элемент ИЛИ-НЕ. 2 ил.

v Л.

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программное устройство управления | 1986 |

|

SU1339558A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1509889A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-01-16—Подача