фае.1

Изобретение относится к вычислительной технике и обеспечивает построение устройств микропрограммного управления.

Цель изобретения - сокращение объема памяти микропрограмм за счет совмещения различных подпрограмм в одном блоке памяти.

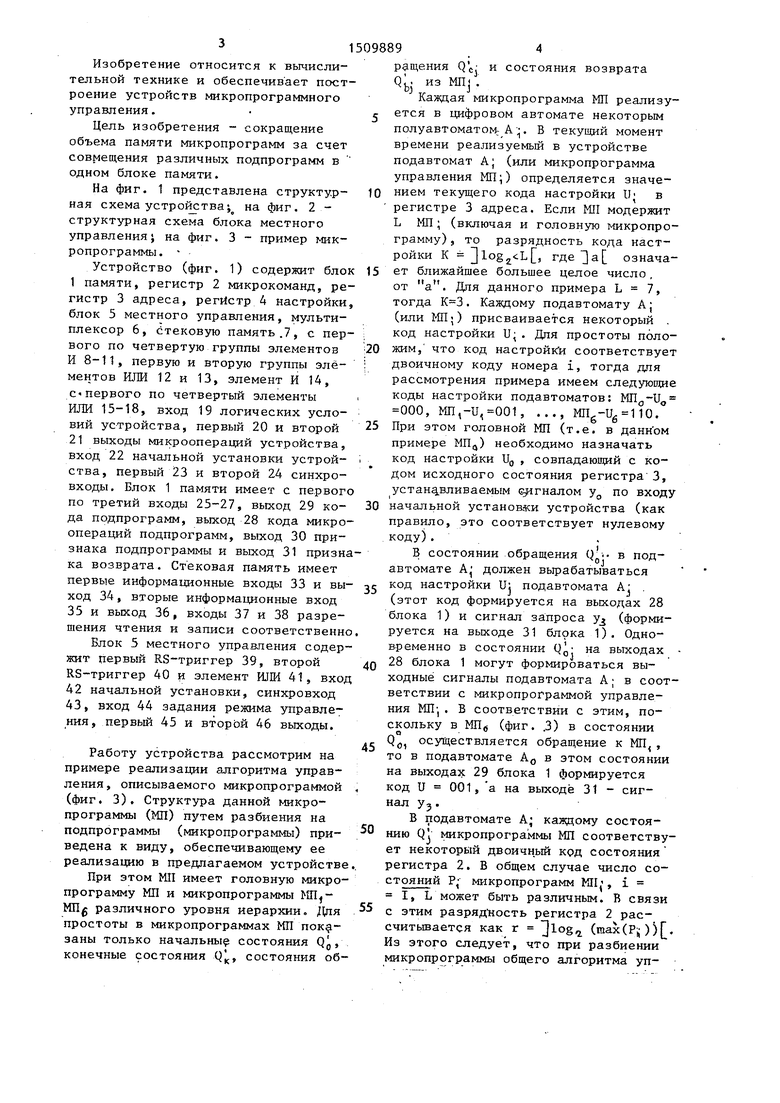

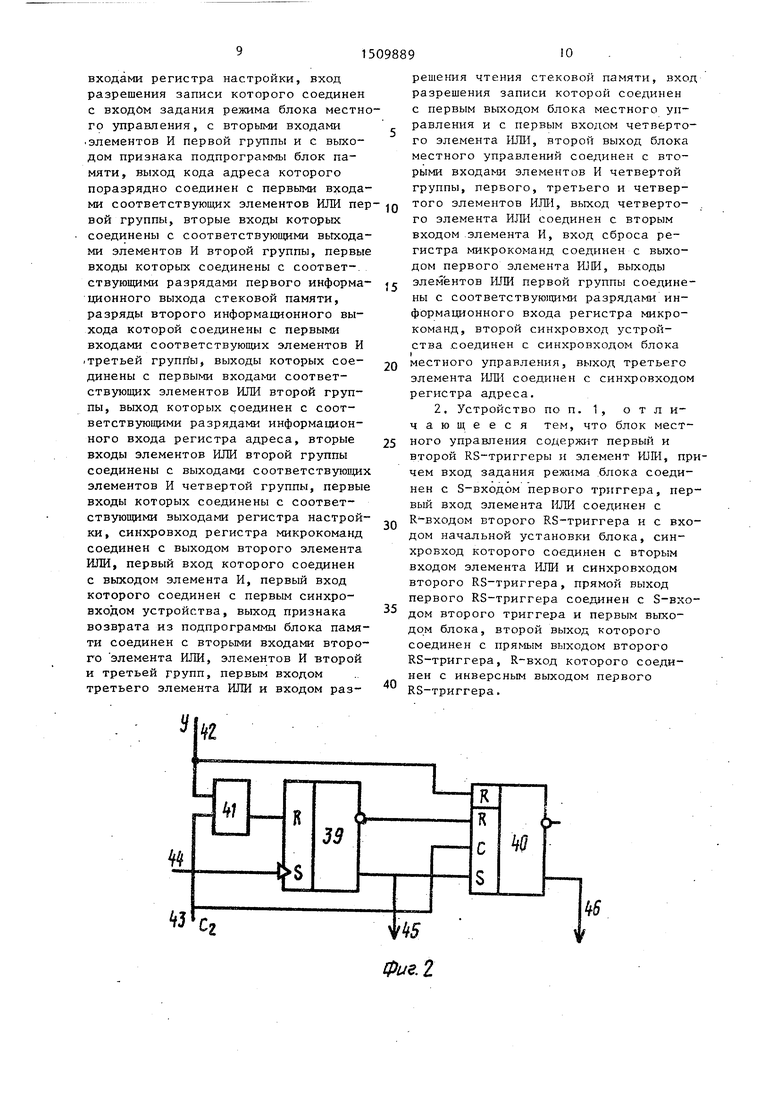

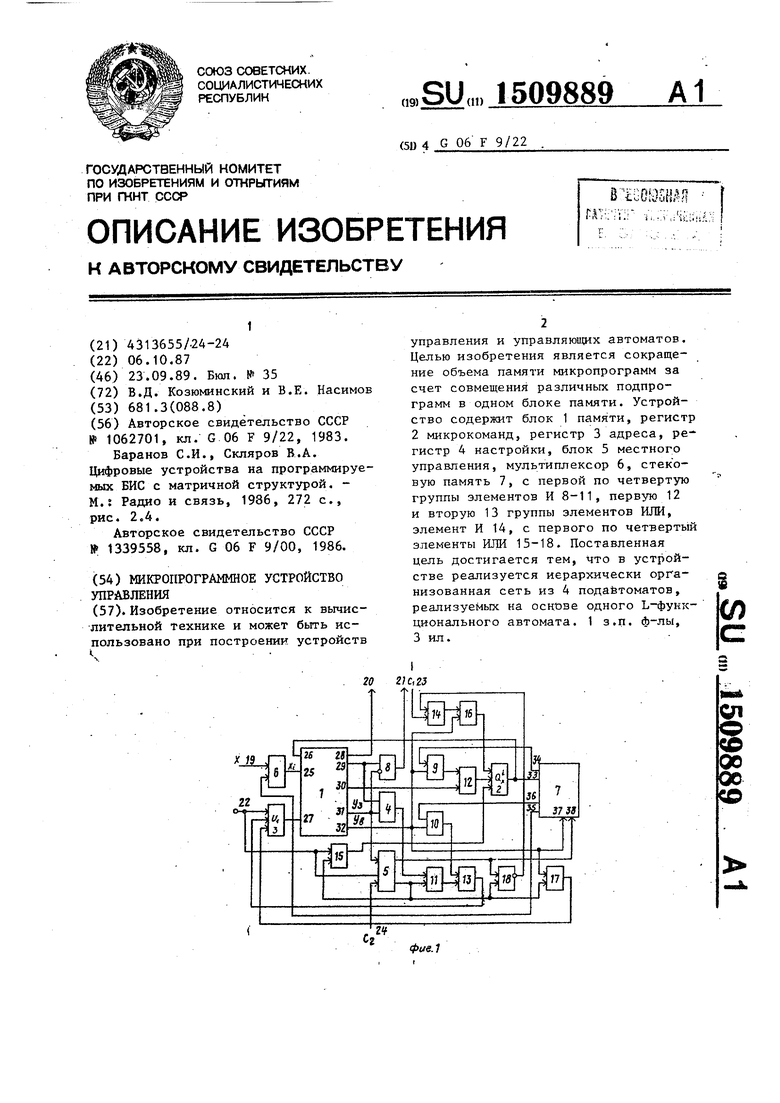

На фиг. 1 представлена структурная схема ус тройства; на фиг. 2 - структурная схема блока местного управленияJ на фиг. 3 - пример микКаждая микропрограмма МП реализуется в цифровом автомате некоторым полуавтоматом; А . В текущий момент времени реализуемый в устройстве подавтомат А; (или микропрограмма управления МП-) определяется значением текущего кода настройки U; в регистре 3 адреса. Если Mil модержит L МП; (включая и головную микропрограмму) 5 то разрядность кода настройки К , где означаропрограммы.

Устройство (фиг. 1) содержит блок 15 ет ближайшее большее целое число, 1 памяти, регистр 2 микрокоманд, ре- от а. Для данного примера L 7,

тогда . Каждому подавтомату AJ (или МП;) присваивается некоторый . ; код настройки U; . Дня простоты поло- ;20 жим, что код настройки соответствует i двоичному коду номера i, тогда для рассмотрения примера имеем следуюоще коды настройки подавтоматов: 000, МП,-и, 001, ..., MIIg-Ug 110. 25 При этом головной МП (т.е. в данн ом примере МП) необходимо назначать код настройки Ug , совпадающий с кодом исходного состояния регистра 3,

гистр 3 адреса, регистр 4 настройки, блок 5 местного управления, мультиплексор 6, стековую память.7, с первого по четвертую группы элементов И 8-11, первую и вторую группы элементов ИШ. 12 и 13, элемент И 14, с Первого по четвертый элементы ИЛИ 15-18, вход 19 логических условий устройства, первый 20 и второй 21 выходы микроопераций устройства, вход 22 начальной установки устрой- i ства, первый 23 и второй 24 синхро- входы. Блок 1 памяти имеет с первого по третий входы 25-27, выход 29 кода подпрограмм, выход 28 кода микроопераций подпрограмм, выход 30 признака подпрограммы и выход 31 признаустан вливаемым с 1гналом у по входу 30 начальной устаноа и устройства (как правило, это соответствует нулевому .коду).

в состоянии обращения QQ в подавтомате А, должен вьграбатываться

в состоянии обращения QQ в подавтомате А, должен вьграбатываться

ка возврата. Стековая память имеет

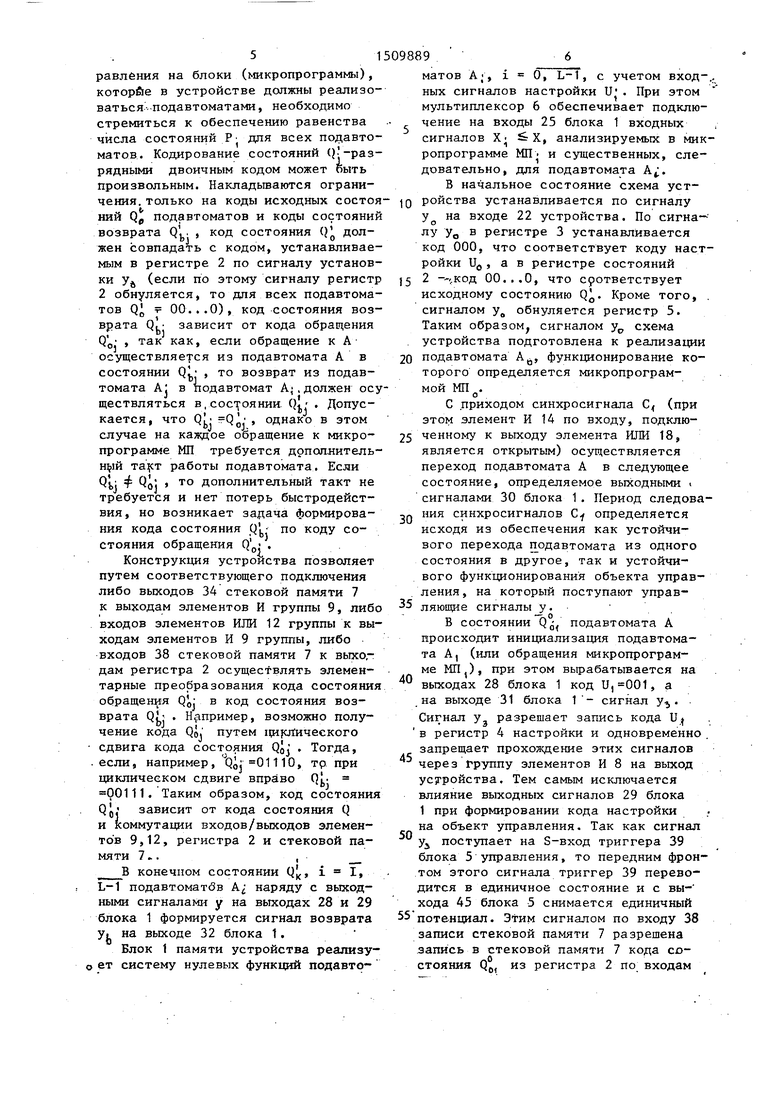

первые информационные входы 33 и вы- 05 ° настройки Uj подавтомата Aj ход 34, вторые информационные вход (этот код формируется на выходах 28 35 и выход 36, входы 37 и 38 разрешения чтения и записи соответственно. Блок 5 местного управления содержит первый RS-триггер 39, второй 40 RS-триггер 40 и элемент ИЛИ 41, вход 42 начальной установки, синхровход 43, вход 44 задания режима управления, первый 45 и вторьй 46 выходы.

блока 1) и сигнал за:проса (форми руется на выходе 31 блока 1). Одновременно в состоянии Qg на выходах 28 блока 1 могут формироваться выходные сигналы подавтомата А; в соот ветствии с микропрограммой управления МП , . В соответствии с этим, поскольку в МПе (фиг. .3) в состоянии f. Q осуществляется обращение к МП, , то в подавтомате Ад в этом состоянии на выхода: 29 блока 1 формируется код и 001, а на выходе 31 - сигнал yj.

Работу устройства рассмотрим на примере реализации алгоритма управления, описываемого микропрограммой (фиг. 3). Структура данной микропрограммы (МП) путем разбиения на подпрограммы (микропрограммы) при- ведена к виду, обеспечивающему ее реализацию в предлагаемом устройстве

При этом МП имеет головную микропрограмму МП и микропрограммы MHg различного уровня иерархии. Дпя простоты в микропрограммах МП заны только начальны состояния Qg, конечные состояния Q , состояния об

ращения Qc и состояния возврата Qy из Mnj .

Каждая микропрограмма МП реализуется в цифровом автомате некоторым полуавтоматом; А . В текущий момент времени реализуемый в устройстве подавтомат А; (или микропрограмма управления МП-) определяется значением текущего кода настройки U; в регистре 3 адреса. Если Mil модержит L МП; (включая и головную микропрограмму) 5 то разрядность кода настройки К , где означаустан вливаемым с 1гналом у по входу 30 начальной устаноа и устройства (как правило, это соответствует нулевому .коду).

в состоянии обращения QQ в подавтомате А, должен вьграбатываться

° настройки Uj подавтомата Aj (этот код формируется на выходах 28

блока 1) и сигнал за:проса (формируется на выходе 31 блока 1). Одновременно в состоянии Qg на выходах 28 блока 1 могут формироваться вы5 ° настройки Uj подавтомата Aj (этот код формируется на выходах 28 0

ходные сигналы подавтомата А; в соответствии с микропрограммой управления МП , . В соответствии с этим, поскольку в МПе (фиг. .3) в состоянии f. Q осуществляется обращение к МП, , то в подавтомате Ад в этом состоянии на выхода: 29 блока 1 формируется код и 001, а на выходе 31 - сигнал yj.

В подавтомате А; каждому состоянию Q , микропрограммы МП соответствует некоторый двоичн.ый код состояния регистра 2. В общем случае число со- стояний Р| микропрограмм МП, i I, L может быть различным. В связи 5 с этим разрядность регистра 2 рас- считьтается как г Jlog (max(Pjj )). Из этого следует, что при разбиении микропрограммы общего алгоритма управления на блоки (микропрограммы), которйе в устройстве должны реализоваться -.-подавтоматами, необходимо стремиться к обеспечению равенства числа состояний PJ дпя всех подавтоматов. Кодирование состояний (-разрядными двоичным кодом может быть произвольным. Накладьтаются ограничения, только на коды исходных состояний QP подавтоматов и коды состояний возврата Q j. , код состояния (Jj, должен совпадать с кодом, устанавливаемым в регистре 2 по сигналу установки у (если по этому сигналу регистр 2 обнуляется, то для всех подавтоматов Q т 00. ..0), код состояния возврата Q

Ь

зависит от кода обращения

Q o , так как, если обращение к А осуществляется из подавтомата А в состоянии , то возврат из подавтомата А: в подавтомат А; , должен осуществляться в, состоянии. QI . Допускается, что QO 9 однако в этом случае на каждое обращение к микропрограмме МП требуется допопнитель- работы подавтомата. Если bi 0| дополнительный такт не требуется и нет потерь быстродействия, но возникает задача формирования кода состояния QL по коду состояния обращения Q .

Конструкция устройства позволяет путем соответствующего подключения либо выходов 34 стековой памяти 7 к выходам элементов И группы 9, либо входов элементов ИЛИ 12 группы к выходам элементов И 9 группы, либо входов 38 стековой памяти 7 к вько,- дам регистра 2 осуществлять элемен- . тарные преобразования кода состояния обращения в код состояния возврата Qtj . Н 1пример, возможно получение кода Qi, путем ци о1ического сдвига кода состояния Qoj . Тогда, если, например, 01110, тр при циклическом сдвиге вправо Qj,- 00111. Таким образом, код состояния Qj,- зависит от кода состояния Q и коммутации входов/выходов элементов 9,12, регистра 2 и стековой памяти 7..,

В конечном состоянии QJ, i I, .

L-1 подавтоматов наряду с выходными сигналами у на выходах 28 и 29 блока 1 формируется сигнал возврата У на выходе 32 блока 1.

Блок 1 памяти устройства реализу- ет систему нулевых функций подавтоматов А;, 1 0, L-1, с учетом вход-., ных сигналов настройки U . При этом мультиплексор 6 обеспечивает подключение на входы 25 блока 1 входных сигналов X;; -X, анализируемых в микропрограмме МП;; и существенных, следовательно, для подавтомата А,;.

В начальное состояние схема устQ ройства устанавливается по сигналу у на входе 22 устройства. По сигна лу УО в регистре 3 устанавливается код 000, что соответствует коду настройки UQ, а в регистре состояний

5 2 -- ,код 00...О, что С9ответствует исходному состоянию . Кроме того, сигналом Уд обнуляется регистр 5. Таким образом, сигналом Ур схема . устройства подготовлена к реализации

0 подавтомата А, функционирование которого определяется микропрограммой МПдС приходом синхросигнала С, (при этом элемент И 14 по входу, подклю5 ченному к выходу элемента ИЛИ 18, является открытым) осуществляется переход подавтомата А в следующее состояние, определяемое выходными сигналами 30 блока 1. Период следования синхросигналов С определяется исходя из обеспечения как устойчивого перехода подавтомата из одного состояния в другое, так и устойчивого функционирования объекта управления , на который поступают управляющие сигналы у. В состоянии Q подавтомата А происходит инициализация подавтомата А, (или обращения микропрограмме МП,), при этом вьфабатывается на выходах 28 блока 1 код U,001, а на выходе 31 блока 1 - сигнал у. . Сигнал у разрешает запись кода U в регистр 4 настройки и одновременно . запрещает прохождение этих сигналов через группу элементов И 8 на выход устройства. Тем самым исключается влияние выходных сигналов 29 блока 1 при формировании кода настройки на объект управления. Так как сигнал Уд поступает на S-вход триггера 39 блока 5 управления, то передним фронтом этого сигнала триггер 39 переводится в единичное состояние и с вы- хода 45 блока 5 снимается единичный

5 потенциал. Этим сигналом по входу 38 записи стековой памяти 7 разрешена запись в стековой памяти 7 кода состояния Qg, из регистра 2 по входам

0

5

0

5

0

32, а по входам 35 - кода настройки из регистра 4. Одновременно по цепи элементов ИЛИ 18 и И 14 блокируется прохождение очередного синхросигнала С на синхровход регистра 2 (тем самым блокируется возможный переход подавтомата А, в другое состояние). С приходом синхросигнала Cj , который поступает на jg синхровход 43 блока 5, осуществляется сдвиг (перезапись) содержимого триггера 39 в триггер 40. При этом по R-входу сигналом С триггер 39 обнуляется. Сигнал с выхода 46 блока г 5 осуществляет по цепи элемента ЛИ 15 обнуление регистра состояний 2, по цепи элементов И 11 подключение- выходов регистра 4 к информационным входам регистра 3, по цепи элемента 17 разрешает перезапись кода настройки Uj из регистра 4 в регистр 3. В результате в регистр 3 записывается код настройки . Схема устройства готова к реализации подавтома- 25 та А. (микропрограммы МП). С приходом очередного синхросигнала С в триггер 40 записьшается состояние О из триггера 39, в результате чего положительным потенциалом с выхода элемента 18 разрешено прохождение синхросигналов С, на синхровход регистра 2. В дальнейшем устройство реализует подавтомат А . Аналогичным образом в состоянии Q J подавтомата А осуществляется инициализация подавтомата А, при этом на выходах 29 блока 1 формируется, код . Состояние . код записываются в первую ячейку стековой цамяти, а коды и Q° переписьшаются во 40 вторую ячейку стековой памяти. Число ячеек стековой памяти 7 кодов состояний и настроек возврата определяется глубиной.вложенности (или обращений) микропрограмм алгоритма 5 управления, Например, глубина обра- рений, а следовательно, и число яче- ек узла памяти, для изображенной на фиг. 3 микропрограммы, равна трем.

В конечном состоянии функциониро- 50 вания подавтомата А (в состоянии Q микропрограмм МП) на выходе 32 блока 1 формируется сигнал возврата у, . Этим сигналом информационные i выходы 34 и 35 стековой памяти 7 под-55 ключаются к информационным входам соответственно регистров 2 и 3. Этим же сигналом разрешается запись с выхода стековой памяти в регистры 2

30

35

g г 5 0 5

0 5

0

5

и 3. Задним фронтом сигнала у осу- ществляетс я перезапись содержимого ячеек стековой памяти. Таким образом,i в регистр 2 записан код 0- подавтомата А,, а в регистр 3 - код . В первую ячейку переписаны из второй ячейки стековой памяти коды ()д, и . В дальнейшем в устройстве реализуется подавтомат А..

Аналогично осуществляется возврат из подавтомата А в подавтомат А.

Таким.образом, в устройстве реализуется иерархически организованная сеть из L подавтоматов, технически реализуемых на основе одного L-функ- ционального автомата.

Формула изобретени-я

1. Микропрограммное устройство . управления, содержащее блок местного управления, регистр микрокоманд, блок памяти, регистр адреса, мультиплексор, первую группу элементов И, причем вход Логических условий устройства соединен с информационным входом мультиплексора, выход которого соединен с первым адресным входом блока памяти, выход кода микроопераций подпрограмм которого соединен с первым выходом микроопераций устройства, выход кода адреса регистра микрокоманд/соединен с вторым адрес- , ным входом блока памяти, третий адресный вход которого соединен с выходом регистра адреса, о т л и ч а- ю щ е е с я тем, что, с целью сокращения объема памяти микропрограмм,, .она содержит стековую память, регистр настройки, с второго по четвертую группы элементов И, первую и вторую группы .элементов ИЛИ, элемент И, с первого по третий элементы ИЛИ и элемент ИЛИ-НЕ, причем выход кода адреса регистра микрокоманд соединен с первым информационным входом стековой, памяти, второй информационный вход которой соединен с управляющим ВХОДОМ мультиплексора и с выходом регистра адреса, вход начальной установки которого соединен с одноимен- нь1М входом блока местного управления, с-первым входом первого элемента ИЛИ и с .входом начальной установки устройства, второй выход микроопераций которого образует выходы элементов И первой группы, первые входы которых соединены с выходами кода подпрограмт мы блока памяти и информадаонными входами регистра настройки, вход разрешения записи которого соединен с входом задания режима блока местного управления, с вторыми входами .элементов И первой группы и с выходом признака подпрограммы блок памяти, выход кода адреса которого поразрядно соединен с первыми входами соответствующих элементов ИЛИ первой группы, вторые входы которых соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с соответ-. ствующими разрядами первого информационного выхода стековой памяти, разряды второго информационного выхода которой соединены с первыми входами соответствующих элементов И .третьей групп ы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ второй группы, выход которых соединен с соответствующими разрядами информационного входа регистра адреса, вторые входы элементов ИЛИ второй группы соединены с выходами соответствующих элементов И четвертой группы, первые входы которых соединены с соответствующими выходами регистра настройки, синхровход регистра микрокоманд соединен с выходом второго элемента ИЛИ, первый вход которого соединен с вьпсодом элемента И, первьш вход которого соединен с первым синхро- входом устройства, выход признака возврата из подпрограммы блока памяти соединен с вторыми входами второго элемента ИЛИ, элементов И второй и третьей гРУПП, первым входом третьего элемента РШИ и входом раз

5

0

5

0

35

40

решения чтения стековой памяти, вход разрешения записи которой соединен с первым выходом блока местного управления и с первым входом четвертого элемента ИЛИ, второй выход блока местного управлений соединен с вторыми входами элементов И четвертой группы, первого, третьего и четвертого элементов ИЛИ, выход четверто- , го элемента ИЛИ соединен с вторым входом элемента И, вход сброса регистра микрокоманд соединен с выходом первого элемента ИШ, выходы элементов ИЛИ первой группы соединены с соответствую1Г(ими разрядами информационного входа регистра микрокоманд, второй синхровход устройства .соединен с синхровходом блока местного управления, выход третьего элемента ИЛ1-1 соединен с синхровходом регистра адреса.

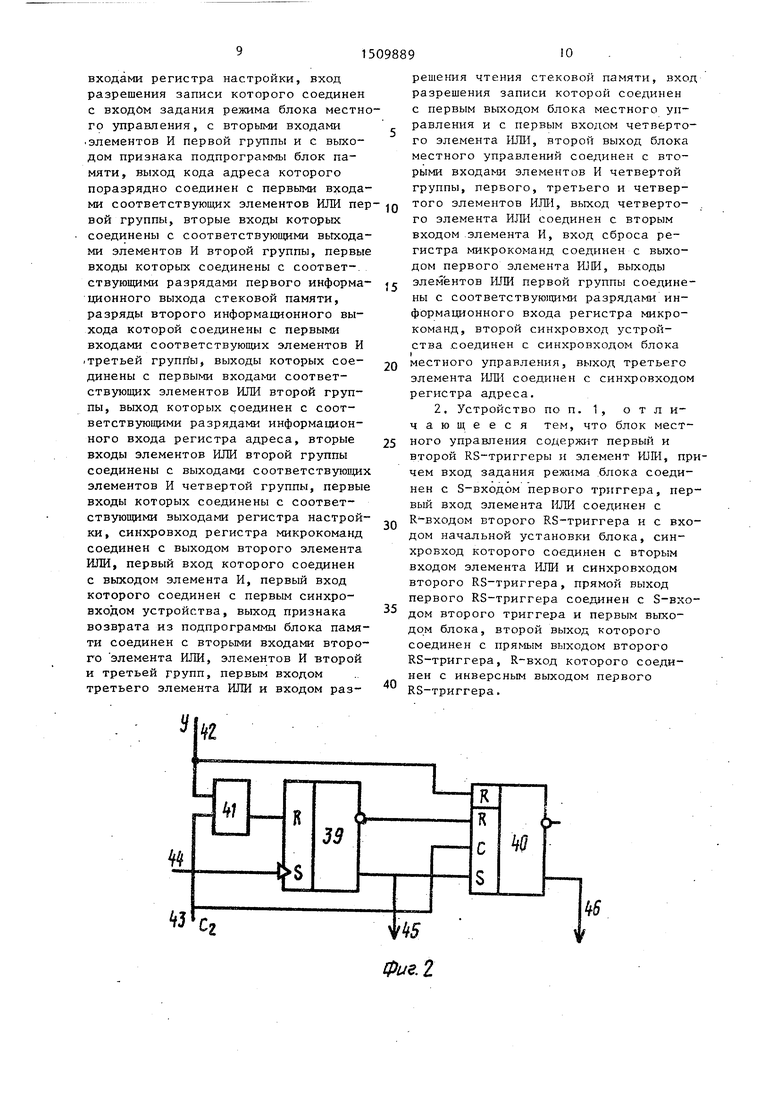

2. Устройство по п, 1, отличающееся тем, что блок местного управления содержит первый и второй RS-триггеры и элемент ИЛИ, причем вход задания режима блока соединен с S-входбм первого триггера, первый вход элемента ИЛИ соединен с К входом второго RS-триггера и с входом начальной установки блока, синхровход которого соединен с вторым входом элемента ИЛИ и синхровходом второго RS-триггера, прямой выход первого RS-триггера соединен с S-BKO- дом второго триггера и первым выходом блока, второй выход которого соединен с прямым выходом второго RS-триггера, R-вход которого соединен с инверсным выходом первого RS-триггера.

уГг--±

Гт1

Л-11

та

.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1989 |

|

SU1674122A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления и управляющих автоматов. Целью изобретения является сокращение объема памяти микропрограмм за счет совмещения различных подпрограмм в одном блоке памяти. Устройство содержит блок 1 памяти, регистр 2 микрокоманд, регистр 3 адреса, регистр 4 настройки, блок 5 местного управления, мультиплексор 6, стековую память 7, с первой по четвертую группы элементов И 8-11, первую 12 и вторую 13 группы элементов ИЛИ, элемент И 14, с первого по четвертый элементы ИЛИ 15-18. Поставленная цель достигается тем, что в устройстве реализуется иерархически организованная сеть из 4 подавтоматов, реализуемых на основе одного L - функционального автомата. 1 з.п. ф-лы, 3 ил.

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Баранов С.И., Скляров В.А | |||

| Цифровые устройства на программируемых БИС с матричной структурой | |||

| - М | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регенеративный теплообменник | 1986 |

|

SU1339358A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1987-10-06—Подача