Ч

ю ел

VI

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на МДП-тран- зисторах для усиления сигналов считываемой информации.

Цель изобретения - повышение надежности усилителя считывания.

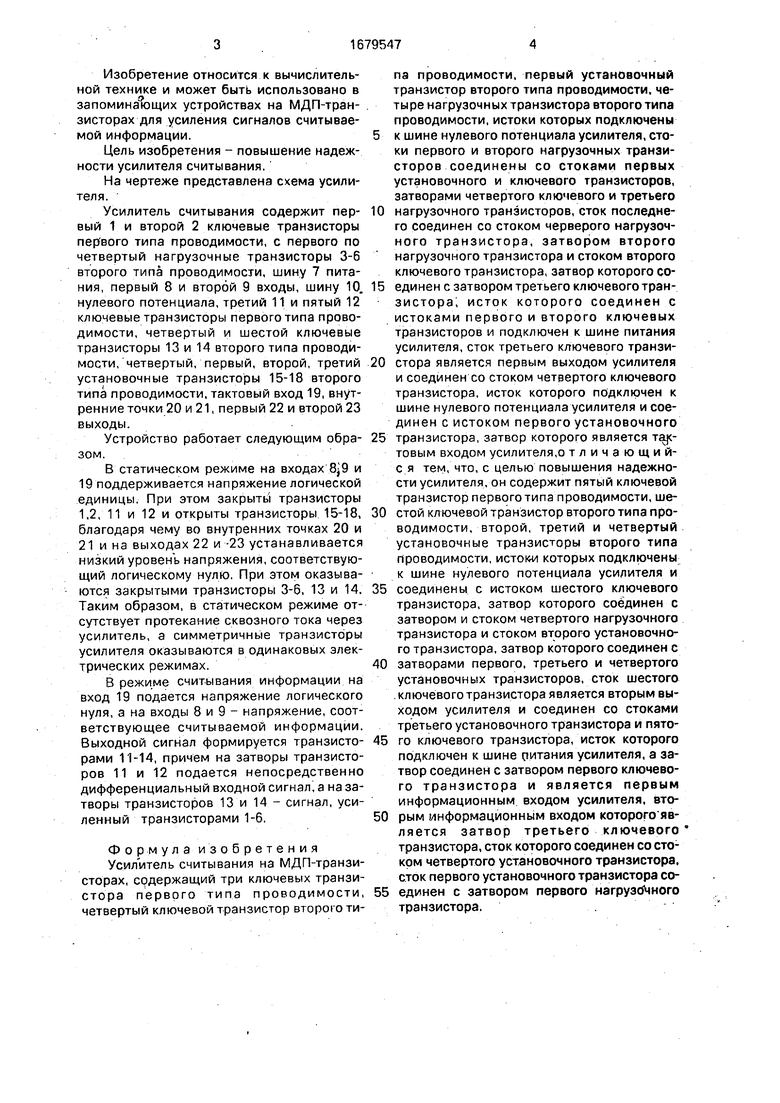

На чертеже представлена схема усилителя.

Усилитель считывания содержит первый 1 и второй 2 ключевые транзисторы первого типа проводимости, с первого по четвертый нагрузочные транзисторы 3-6 второго типа проводимости, шину 7 питания, первый 8 и второй 9 входы, шину 10. нулевого потенциала, третий 11 и пятый 12 ключевые транзисторы первого типа проводимости, четвертый и шестой ключевые транзисторы 13 и 14 второго типа проводимости, четвертый, первый, второй, третий установочные транзисторы 15-18 второго типа проводимости, тактовый вход 19, внутренние точки 20 и 21, первый 22 и второй 23 выходы.

Устройство работает следующим образом.

В статическом режиме на входах и 19 поддерживается напряжение логической единицы. При этом закрыты транзисторы 1,2, 11 и 12 и открыты транзисторы 15-18, благодаря чему во внутренних точках 20 и 21 и на выходах 22 и -23 устанавливается низкий уровень напряжения, соответствующий логическому нулю. При этом оказываются закрытыми транзисторы 3-6, 13 и 14. Таким образом, в статическом режиме отсутствует протекание сквозного тока через усилитель, а симметричные транзисторы усилителя оказываются в одинаковых электрических режимах.

В режиме считывания информации на вход 19 подается напряжение логического нуля, а на входы 8 и 9 - напряжение, соответствующее считываемой информации. Выходной сигнал формируется транзисторами 11-14, причем на затворы транзисторов 11 и 12 подается непосредственно дифференциальный входной сигнал, а на затворы транзисторов 13 и 14 - сигнал, усиленный транзисторами 1-6.

Формула изобретения Усил итель считывания на МДП-транзи- сторах, содержащий три ключевых транзистора первого типа проводимости, четвертый ключевой транзистор второго типа проводимости, первый установочный транзистор второго типа проводимости, четыре нагрузочных транзистора второго типа проводимости, истоки которых подключены

к шине нулевого потенциала усилителя, стоки первого и второго нагрузочных транзисторов соединены со стоками первых установочного и ключевого транзисторов, затворами четвертого ключевого и третьего

нагрузочного транзисторов, сток последнего соединен со стоком черверого нагрузочного транзистора, затвором второго нагрузочного транзистора и стоком второго ключевого транзистора, затвор которого соединен с затвором третьего ключевого тран- зистора, исток которого соединен с истоками первого и второго ключевых транзисторов и подключен к шине питания усилителя, сток третьего ключевого транзистора является первым выходом усилителя и соединен со стоком четвертого ключевого транзистора, исток которого подключен к шине нулевого потенциала усилителя и соединен с истоком первого установочного

транзистора, затвор которого является тактовым входом усилителя,о тличающий- с я тем, что, с целью повышения надежности усилителя, он содержит пятый ключевой транзистор первоготипа проводимости, шестой ключевой транзистор второго типа проводимости, второй, третий и четвертый установочные транзисторы второго типа проводимости, истокм которых подключены к шине нулевого потенциала усилителя и

соединены с истоком шестого ключевого транзистора, затвор которого соединен с затвором и стоком четвертого нагрузочного транзистора и стоком второго установочного транзистора, затвор которого соединен с

затворами первого, третьего и четвертого установочных транзисторов, сток шестого ключевого транзистора является вторым выходом усилителя и соединен со стоками третьего установочного транзистора и пятого ключевого транзистора, исток которого подключен к шине питания усилителя, а затвор соединен с затвором первого ключевого транзистора и является первым информационным входом усилителя, вторым информационным входом которого яв- ляется затвор третьего ключевого транзистора, сток которого соединен со стоком четвертого установочного транзистора, сток первого установочного транзистора соединен с затвором первого нагрузбчного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на МДП-тран- зисторах для усиления сигналов считываемой информации. Целью изобретения является повышение надежности усилителя считывания. Для этого в усилитель введены пятый и шестой ключевые транзисторы 12, 14 и второй, третий и четвертый установочные транзисторы 17, 18, 15 с соответствующими связями. Затворы транзисторов 12,11 являются парафазным входом усилителя, а стоки транзисторов 13, 14 - парафазным выходом. Усиление парафазного сигнала обеспечивает большую чувствительность усилителя. 1 ил.

| Патент США № 4479202, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Авторское свидетельство СССР № 1200333, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-09-23—Публикация

1989-08-03—Подача