Изобретение относится к вычислительной технике и может быть использовано для сопряжения видеоконтроллера и процессора через общую память в системах обработки данных, в частности в видеотерминалах, дисплеях, персональных ЭВМ.

Цель изобретения - расширение области применения за счет использования с быстродействующими процессором и видеоконтроллером.

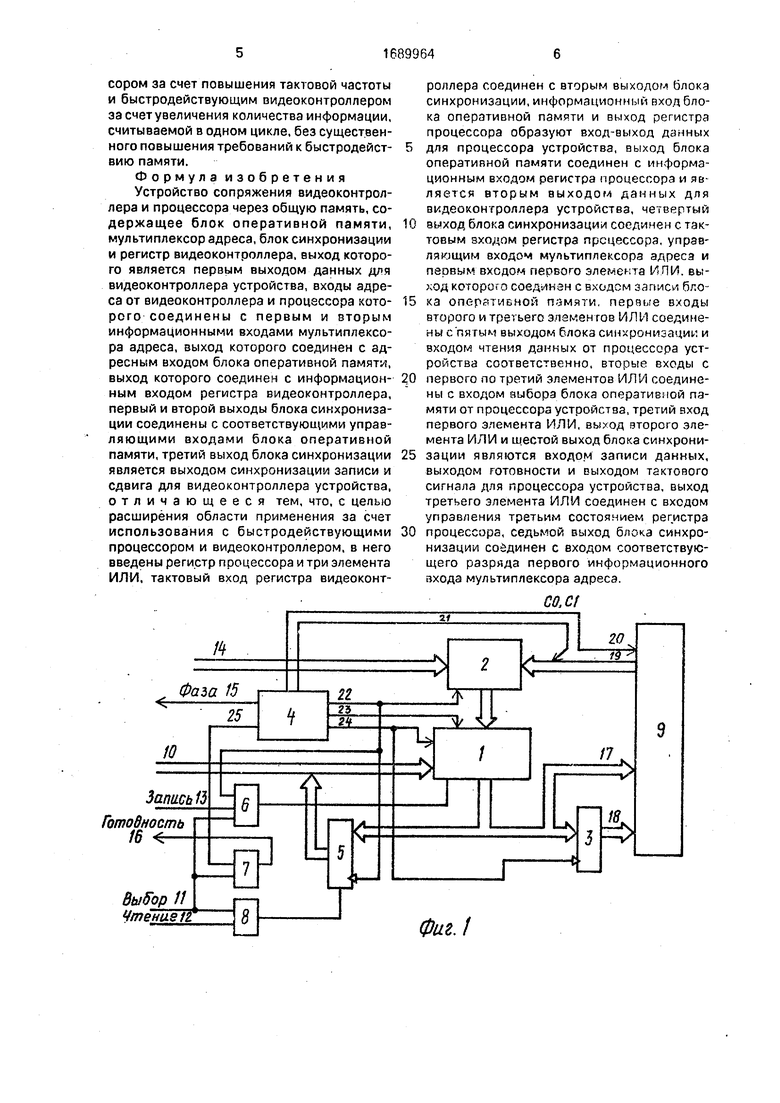

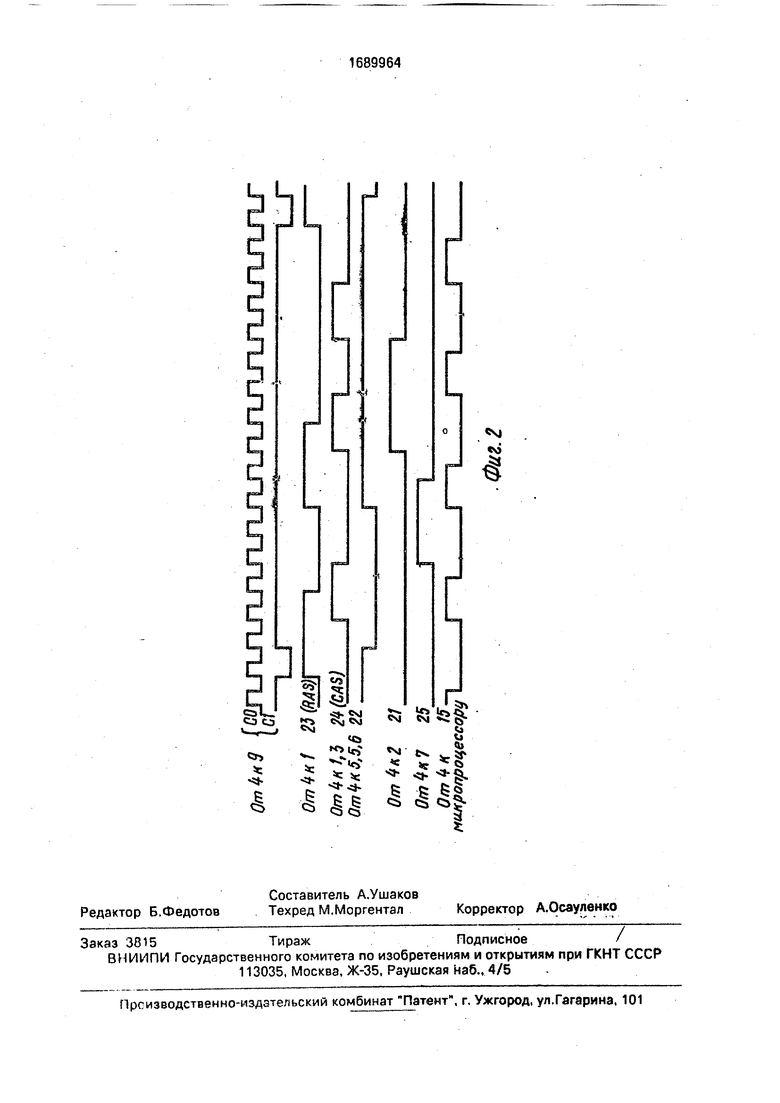

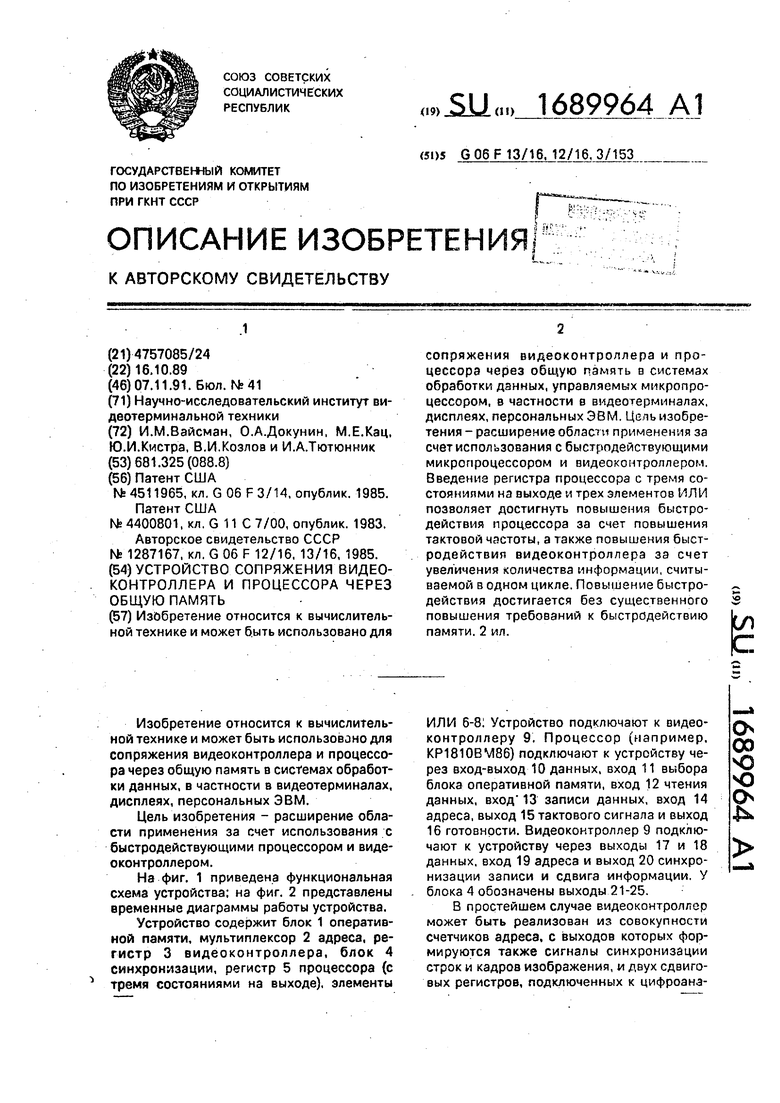

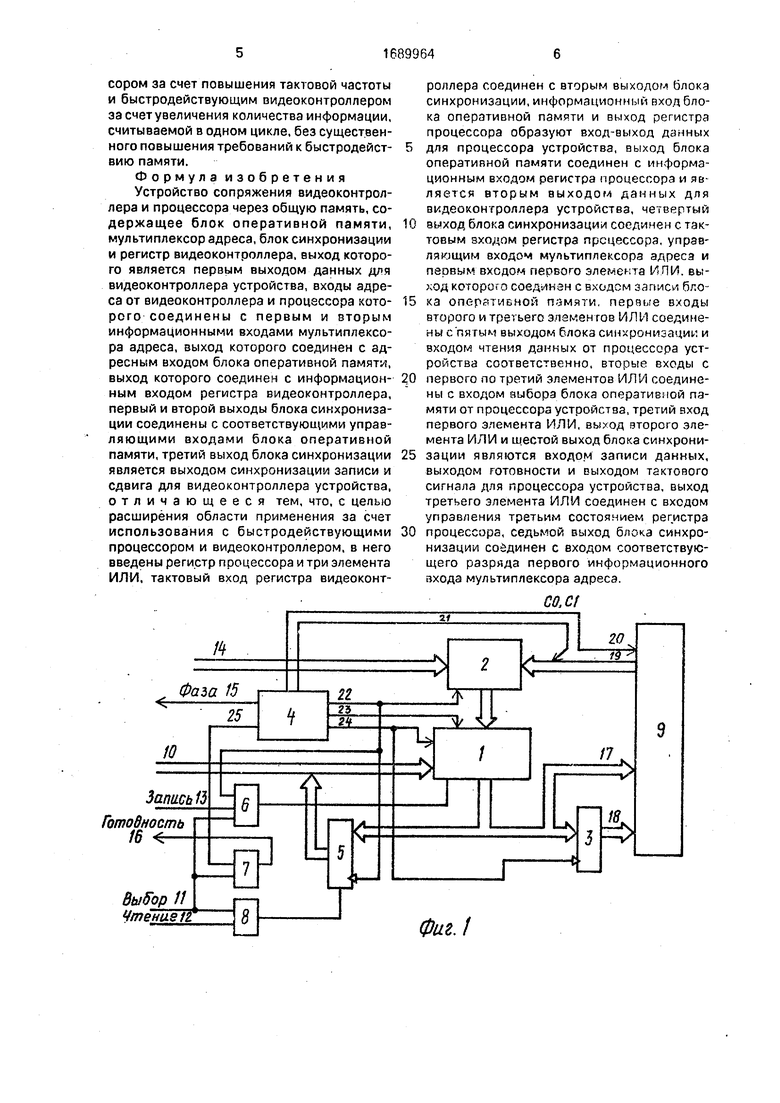

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 представлены временные диаграммы работы устройства.

Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3 видеоконтроллера, блок 4 синхронизации, регистр 5 процессора (с тремя состояниями на выходе), элементы

ИЛИ 6-8 Устройство подключают к видеоконтроллеру 9. Процессор (например, КР1810ВМ86) подключают к устройству через вход-выход 10 данных, вход 11 выбора блока оперативной памяти, вход 12 чтения данных, вход 13 записи данных, вход 14 адреса, выход 15 тактового сигнала и выход 16 готовности. Видеоконтроллер 9 подключают к устройству через выходы 17 и 18 данных, вход 19 адреса и выход 20 синхронизации записи и сдвига информации. У блока 4 обозначены выходы 21-25.

В простейшем случае видеоконтроллер может быть реализован из совокупности счетчиков адреса, с выходов которых формируются также сигналы синхронизации строк и кадров изображения, и двух сдвиговых регистров, подключенных к цифроанаО 00 О

ю о

N

логовому преобразователю, на выходе которого формируется видеосигнал.

Устройство работает следующим образом. Блок А синхронизации на выходах 20 формирует (фиг. 2) сигнал с частотой растровых точек СО и сигнал загрузки видеоконтроллера С1, поступающие на вход видеоконтроллера 9. По сигналу С1 видеоконтроллер 9 формирует адрес следующей отображающей ячейки и выдает его на мультиплексор 2 адреса. Мультиплексор 2 подает на блок 1 оперативной памяти либо адрес процессора, либо адрес видеоконтроллера 9. При этом к адресу видеоконтроллера 9 прибавляется в качестве старшего адресного разряда сигнал с выхода 21 блока 4 синхронизации. Переключение источника адреса (процессор или видеоконтроллер 9) происходит по сигналу с выхода 22 блока 4 синхронизации. Блок 4 синхронизации обеспечивает формирование сигналов управления на выходах 23, 24 для блока 1 оперативной памяти (RAS - строб адреса строк, CAS - строб адреса столбцов), а также тактового сигнала на выходе 15, поступающего на процессор.

Частота тактового сигнала на выходе 15 в четыре раза больше частоты сигнала загрузки С1 видеоконтроллера 9. Таким образом, цикл обращения к памяти видеоконтроллера 9 равен машинному циклу процессора (четыре такта). Блок 4 синхронизации формулирует также сигнал подсинхрон- низации на выходе 25, поступающий на первый вход элемента ИЛИ 7. На второй вход этого элемента поступает сигнал выбора блока 1 оперативной памяти от процессора. Сигнал с элемента ИЛИ 7 поступает на вход управления готовностью процессора. При наличии сигнала ВЫБОР низкого уровня готовность на выходе элемента ИЛИ 7 отсутствует до тех поо, пока сигнал под- синхронизации на его втором входе имеет низкий уровень. В интервале, предназначенном для обращения процессора к блоку

Iоперативной памяти, сигнал подсинхро- низации переходит в 1, появляется готовность, и процессор переходит к следующему машинному циклу. При выполнении записи в блок 1 оперативной памяти процессор выставляет сигналы ВЫБОР и ЗАПИСЬ низкого уровня, поступающие через входы

IIи 13 на второй и третий входы элемента ИЛИ 6. На первый вход этого элемента поступает сигнал с выхода 22, имеющий низкий уровень в интервале обращения процессора. Таким образом, на выходе элемента ИЛИ б формируется сигнал записи, поступающий на соответствующий вход блока 1 оперативной памяти. В блок 1 oneративной памяти записывается информация, поступающая по шине данных через вход-выход 10 от процессора. При этом на адресные входы блока 1 оперативной памяти поступает через мультиплексор 2 адрес с адресной шины процессора. При считывании информации из блока 1 оперативной памяти процессор выставляет сигналы ВЫБОР и ЧТЕНИЕ низкого уровня, поступа0 ющие на входы элемента ИЛИ 8. Сигнал низкого уровня на выходе этого элемента выводит регистр 5 процессора из третьего состояния, и его выходы подключаются в шине данных процессора через вход-выход

5 10. По фронту сигнала на выходе 22, соответствующему окончанию интервала, предназначенного для обращения процессора к блоку 1 оперативной памяти, информация с выходов блока 1 оперативной памяти запи0 сывается в регистр 5 процессора и поступает через него на шину данных процессора. Эта информация сохраняется в регистре 5 микропроцессора и присутствует на шине данных до тех пор, пока процессор не сни5 мет сигналы ЧТЕНИЕ или ВЫБОР на входах 12 и 11. Если процессор находится в состоянии ожидания, нто используется, в частности, при отладке программ в пошаговом режиме, информация на выходе регистра 5

0 процессора также остается неизменной, т.к. по каждому следующему фронту сигнала с выхода 22 информация в регистре 5 дублируется.

Первый и второй интервалы доступа ви5 деоконтроллера 9 в блок 1 оперативной памяти отличаются тем, что чигнал RAS на выходе 23 формируется только в первом интервале. Во втором интервале используется страничный режим считывания, когда пере0 ключается только сигнал CAS на выходе 24. Этот режим позволяет снизить требования к быстродействию памяти. В первом и втором интервалах видеоконтроллера 9 сигнал с выхода 21, используемый в качестве стар5 шего адресного разряда, имеет различные значения. Таким образом, в первом и втором интервалах считываются различные ячейки памяти. Информация, считываемая в , первом интервале видеоконтроллера 9 по

0 фронту сигнала CAS с выхода 24, записывается в регистр 3 видеоконтроллера. Информация, считываемая во втором интервале, поступает непосредственно на видеоконтроллер 9. Таким образом, к моменту форми5 рования блоком 4 синхронизации сигнала С1 (с выхода 20) загрузки видеоконтроллера 9 на его входах 16 и 17 присутствует информация, считанная из двух ячеек памяти.

Таким образом, устройство можно использовать с быстродействующим процессором за счет повышения тактовой частоты и быстродействующим видеоконтроллером за счет увеличения количества информации, считываемой в одном цикле, без существенного повышения требований к быстродейст- вию памяти.

Формула изобретения Устройство сопряжения видеоконтроллера и процессора через общую память, содержащее блок оперативной памяти, мультиплексор адреса, блок синхронизации и регистр видеоконтроллера, выход которого является первым выходом данных для видеоконтроллера устройства, входы адреса от видеоконтроллера и процессора кото- рого соединены с первым и вторым информационными входами мультиплексора адреса, выход которого соединен с адресным входом блока оперативной памяти, выход которого соединен с информацион- ным входом регистра видеоконтроллера, первый и второй выходы блока синхронизации соединены с соответствующими управляющими входами блока оперативной памяти, третий выход блока синхронизации является выходом синхронизации записи и сдвига для видеоконтроллера устройства, отличающееся тем, что, с целью расширения области применения за счет использования с быстродействующими процессором и видеоконтроллером, в него введены регистр процессора и три элемента ИЛИ, тактовый вход регистра видеоконтроллера соединен с вторым выходом блока синхронизации, информационный вход блока оперативной памяти и выход регистра процессора образуют вход-выход данных для процессора устройства, выход блока оперативной памяти соединен с информационным входом регистра процессора и является вторым выходом данных для видеоконтроллера устройства, четвертый выход блока синхронизации соединен с тактовым входом регистра процессора, управляющим входом мультиплексора адреса и первым входом первого элемента И ПИ. выход которого соедугнэн с входом записи блока оперативной памяти, первые входы второго и третьего эламен гов ИЛИ соединены снятым выходом блока синхронизации и входом чтения данных от процессора устройства соответственно, вторые входы с первого по третий элементов ИЛИ соединены с входом выбора блока оперативной памяти от процессора устройства, третий вход первого элемента ИЛИ, второго элемента ИЛИ и шестой выход блока синхронизации являются входом записи данных, выходом готовности и выходом тактового сигнала для процессора устройства, выход третьего элемента ИЛИ соединен с входом управления третьим состоянием регистра процессора, седьмой выход блока синхронизации соединен с входом соответствующего разряда первого информационного входа мультиплексора адреса.

CQ.C1

«sj «si

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора и видеоконтроллера | 1988 |

|

SU1522225A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1709325A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Вычислительная система | 1989 |

|

SU1734101A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| СИСТЕМА ДЛЯ РАСПРЕДЕЛЕННОЙ ОБРАБОТКИ ДАННЫХ С ОБЩИМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1992 |

|

RU2037876C1 |

| Таймер | 1985 |

|

SU1357939A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения видеоконтроллера и процессора через общую память в системах обработки данных, управляемых микропроцессором, в частности в видеотерминалах, дисплеях, персональных ЭВМ. Цель изобретения - расширение области применения за счет использования с быстродействующими микропроцессором и видеоконтроллером. Введение регистра процессора с тремя состояниями на выходе и трех элементов ИЛИ позволяет достигнуть повышения быстродействия процессора за счет повышения тактовой частоты, а также повышения быстродействия видеоконтроллера за счет увеличения количества информации, считываемой в одном цикле. Повышение быстродействия достигается без существенного повышения требований к быстродействию памяти. 2 ил. Ё

| Патент США № 4511965, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Патент США № 4400801,кл, G 11 С 7/00, опублик | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-07—Публикация

1989-10-16—Подача