Изобретение относится к вычислительной технике и может быть использовано в микроэвм с графическим дисплеем большой разрешающей способнос-- ти,.

Целью изобретения является повышение быстродействия и сокращение объема оборудования.

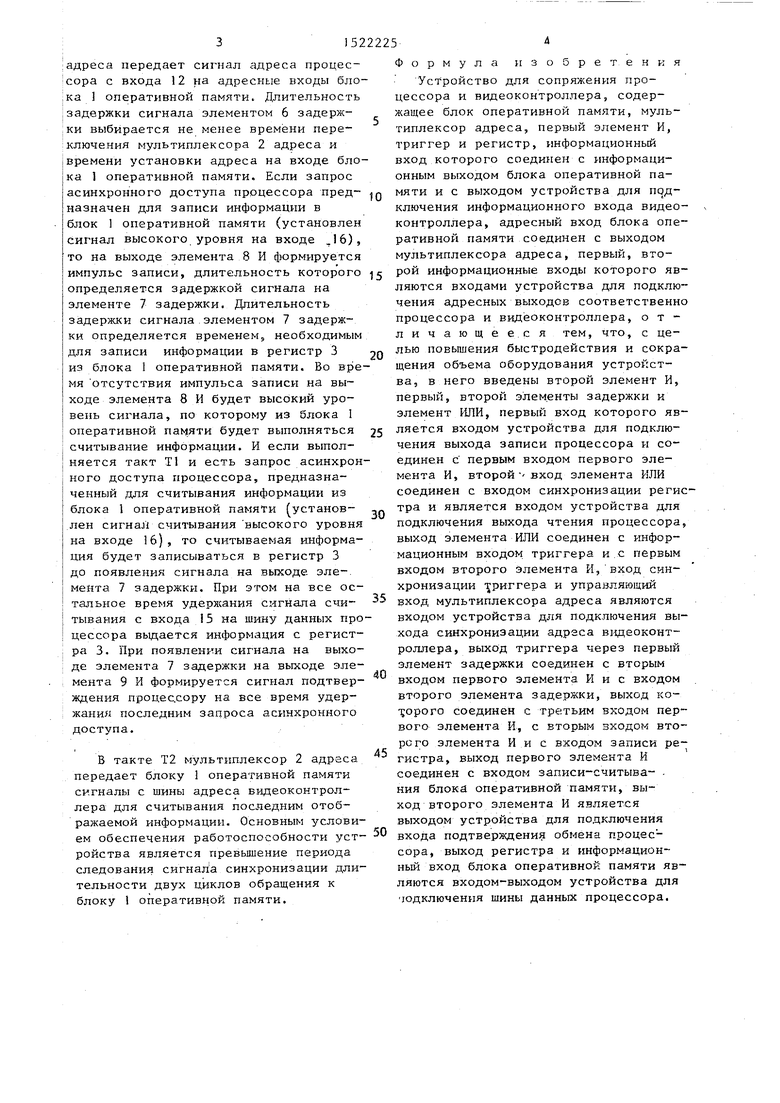

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3, элемент 4 ИЛИ, триггер 5, первый, второй элементы задержки 6, 7, первый, второй элементы И 8, 9, вход-выход 10 устройства для подключения шины данных процессора, выход 11 устройства для подключения информационного входа видеоконтроллера, входы 12,. 13 устройства для подключения адресных выходов процессора и видеоконтроллера, вход 14 устройства для подключения выхода синхронизации адреса видеоконтроллера, входы 15, 16 устройства для подключения выходов чтения и записи процессора, выход 17 устройства для подключения входа подтверждения обмена процессора.

Устройство работает следующим образом.

Период следования сигнала синхронизации с входа 14 делится на два такта Т1 и Т2. Такт Т1 отдается процессору для считывания (записи) информации из блока 1 оперативной памяти. Такт Т2 отдается видеоконтроллеру для считывания отображаемой информации. Видеоконтроллер считывает данные из блока I оперативной памяти с частотой отображения на экране ин- ди dTopa. По запросу.асинхронного доступа процессора триггер 5 с наступлением такта Т устанавливается в единичное состояние. По сигналу с входа 14 в такте T1 мультиплексор 2

О1

to to to

lN5

сд

:адреса передает сигнал адреса процессора с входа 12 на адресньзе входы бло;Ка 1 оперативной памяти. Длительность задержки сигнала элементом 6 задержки выбирается не менее времени переключения мультиплексора 2 адреса и

iвремени установки адреса на входе блока 1 оперативной памяти. Если запрос асинхронного доступа процессора предназначен для записи информации в блок 1 оперативной памяти (установлен сигнал высокого уровня на входе ,16), то на выходе элемента 8 И формируется импульс записи, длительность которого определяется задержкой сигнала на элементе 7 задержки. Длительность задержки сигнала,элементом 7 задержки определяется временем, необходимым для записи информации в регистр 3 из блока 1 оперативной памяти. Во время отсутствия импульса записи на выходе элемента 8 И будет высокий уровень сигнала, по которому из блока 1

оперативной памяти будет выполняться считывание информации. И если выполняется такт 11 и есть запрос асинхронного доступа процессора, предназначенный для считывания информации из блока 1 оперативной памяти установлен сигнал считывания высокого уровня на входе 16), то считываемая информация будет записываться в регистр 3 до появления сигнала на выходе эле- мента 7 задержки. При этом на все остальное время удержания сигнала считывания с входа 15 на шину данных процессора выдается информация с регистра 3. При появлении сигнала на выходе элемента 7 задержки на выходе элемента 9 И формируется сигнал подтверждения процессору на все время удержания последним запроса асинхронного доступа.

В такте Т2 мультиплексор 2 адреса передает блоку 1 оперативной памяти сигналы с шины адреса видеоконтроллера для считывания последним отображаемой информации. Основным условием обеспечения работоспособности устройства является превьшение периода следования сигнал а синхронизации длительности двух циклов обращения к блоку 1 оперативной памяти.

10

j о 25

2225Л

Формула изобретения

Устройство для сопряжения процессора и видеоконтроллера, содержащее блок оперативной памяти, мультиплексор адреса, первый элемент И, триггер и регистр, информационный вход которого соединен с информационным выходом блока оперативной памяти и с выходом устройства для подключения информационного входа видеоконтроллера, адресный вход блока оперативной памяти соединен с выходом мультиплексора адреса, первый, второй информационные входы которого являются входами устройства для подключения адресных выходов соответственно процессора и видеоконтроллера, отличающееся тем, что, с целью повьш1ения быстродействия и сокращения объема оборудования устройства, в него введены второй элемент И, первый, второй элементы задержки и элемент ИЛИ, первый вход которого является входом устройства для подключения выхода записи процессора и соединен с первым входом первого элемента И, второй вход элемента ИЛИ соединен с входом синхронизации регистра и является входом устройства для подключения выхода чтения процессора, выход элемента ИЛИ соединен с информационным входом, триггера и .с первым входом второго элемента И, вход синхронизации ритгера и управляющий вход мультиплексора адреса являются входом устройства для подключения выхода синхронизации адреса видеоконтроллера, выход триггера через первый элемент задержки соединен с вторым входом первого элемента И и с входом второго элемента задержки, выход ко- joporo соединен с третьим входом пер вого элемента И, с вторым входом второго элемента И и с входом записи регистра, выход первого элемента И соединен с входом записи-считыва- . ния блока оперативной памяти, выход второго элемента И является выходом устройства для подключения входа подтверждения обмена процессора, выход регистра и информационный вход блока оперативной памяти являются входом-выходом устройства для юдключения шины данных процессора.

30

35

40

45

50

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Устройство сопряжения видеоконтроллера и процессора через общую память | 1989 |

|

SU1689964A1 |

| СИСТЕМА ДЛЯ РАСПРЕДЕЛЕННОЙ ОБРАБОТКИ ДАННЫХ С ОБЩИМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1992 |

|

RU2037876C1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1709325A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

Изобретение относится к вычислительной технике и может быть использовано в микроЭВМ с графическим дисплеем большой разрешающей способности. Целью изобретения является повышение быстродействия и сокращение объема оборудования. Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3, элемент ИЛИ 4, триггер 5, первый, второй элементы задержки 6, 7, первый, второй элементы И 8, 9. Устройство обеспечивает бесконтрольную работу процессора и видеоконтроллера через общую память. 1 ил.

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для сопряжения двух процессоров через общую память | 1985 |

|

SU1287167A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-15—Подача