Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах.

Целью изобретения является упрощение устройства за счет изменения технической реализации алгоритма обмена.

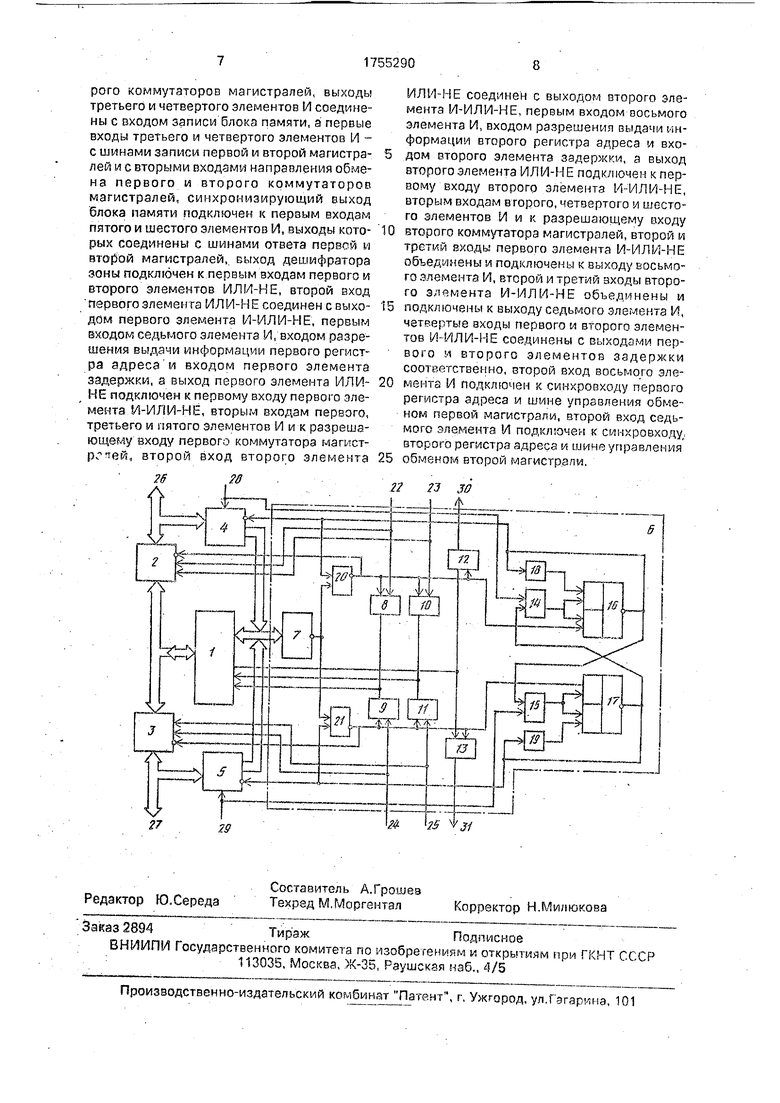

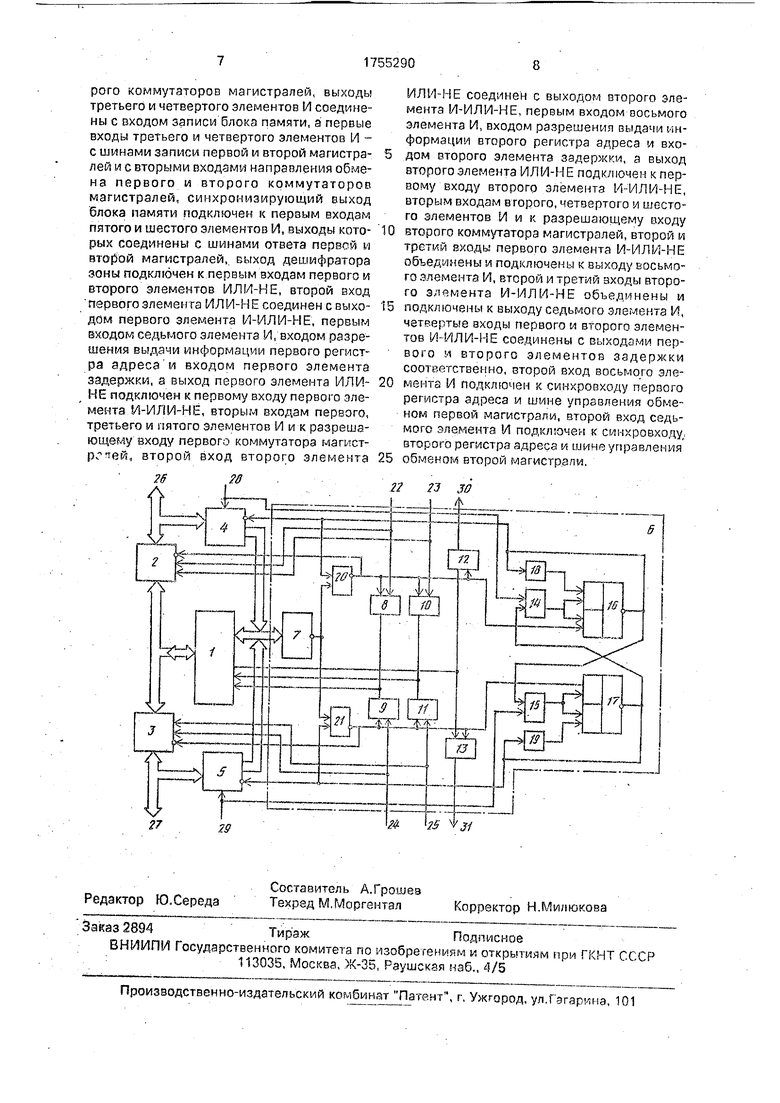

На чертеже представлена блок-схема устройства,

Устройство содержит блок 1 памяти, коммутаторы 2 и 3 магистралей, регистры 4 и 5 адреса, б коммутатором, состоящий из дешифратора зоны 7, с первого по восьмой элементы И 8-15, первого 16 и второго 17 И-ИЛИ-НЕ, первого 18 и второго 19 элемента задержки, первого 20 и второго 21 элементов ИЛИ-НЕ. На чертеже показаны шины 22 и 23, чтения л записи первой магистрали шины 24 и 25 чтения и записи второй магистрали, информационно-адресные шины 26 и 27, шины управления обменом 28 и

29, шины 30 и 31 ответа первой и второй магистралей.

Блок 1 памяти представляет собой набор микросхем памяти, имеющих вход адресных линий и двунаправленный информационный вход-выход (например К541РУ2) и схемы управления, вырабатывающей синхронизирующий сигнал, используемый как сигнал ответа.

Регистры 4 и 5 адреса представляют собой регистры с тремя состояниями на выходе. В качестве таких регистров могут быть использованы регистры К533ИР27.

Дешифратор 7 зоны адресов представляет собой компаратор (схему сравнения) адресов, на выходе которого появляется нулевой уровень напряжения при совпадении адреса на ее входе с заданным. В остальных случаях на выходе дешифратора присутствует высокий уровень напряжения.

кзквма

Элементы 18 и 19 задержки представляют собой интегрирующие PC цепочки, время задержки которых выбрано большим, чем сумма времени задержки прохождения сигнала синхронизации обмена через элементы И-ИЛИ-НЕ 16 или 17, времени дешифрации адреса на дешифраторе 7 и времени прохождения сигнала через элементы ИЛИ НЕ 20 и 21.

Остальные элементы схемы стандартны и выпускаются в виде интегральных микросхем.

Устройство работает следующим образом.

При отсутствии сигналов синхронизации обмена на линиях 28 и 29 присутствует сигнал низкого уровня, В результате на выходах восьмого и седьмого 15 элементов И сигналы низкого уровня и таким образом на выходах первого 16 и второго 17 элементов И ИЛИ НЕ сигналы высокого уровня, на выходах элементов ИЛИ НЕ 20 и 21 сигналы низкого уровня. На разрешающие входы первого 2 и второго 3 коммутаторов магистралей поступают сигналы низкого уровня и коммутаторы сохраняют отключенными информационно-адресные шины 26 и 27 магистралей от блока 1 памяти. Отсутствие единичных уровней на разрешающих входах элементов И 14-19 приводит к тому, что сигналы с линий 22, 23 и 24, 25 чтения и записи с первой и второй магистралей не проходят в блок 1 памяти, а выходные сигналы синхронизации блока 1 памяти не проходят на линии ответа 30 и 31.

Режим работы устройства сопряжения зависят от уровней сигналов синхронизации обмена на линиях 28 и 29. Возможны следующие случаи сочетания наличия сигналов синхронизации обмена, определяющие разные режимы работы устройства.

Появление сигнала синхронизации обмена со стороны одной магистрали, при отсутствии сигнала синхронизации обмена со стороны другой магистрали.

Появление сигнала синхронизации обмена со стороны обеих магистралей.

Рассмотрим случай появления сигнала синхронизации обмена со стороны первой магистрали, при отсутствии сигнала синхронизации обмена со стороны второй магистрали, Перепад сигнала синхронизации обмена из низкого уровня в высокий, поступающий по линии 28, записывает адрес устройства, к которому происходит обращение, присутствующий на информационно-адресной шине 26, в первый регистр адреса. Сигнал с линии 28 поступает . на второй вход седьмого элемента И 14. На первом входе этого элемента сигнал высокого уровня с выхода второго элемента И ИЛИ НЕ 17 (так как на линии 29 сигнал низкого уровня) и поэтому на выходе седьмого элемента И 4 и на втором и третьем

входах первого элемента И-ИЛИ-НЕ 16 устанавливается сигнал высокого уровня. Высокий уровень напряжения присутствует также на четвертом входе первого элемента И-ИЛИ-НЕ 16, так как на выходе линии 18

0 сигнал высокого уровня. Таким образом, на выходе первого элемента И-ИЛИ-НЕ 16 устанавливается сигнал низкого уровня. Этот сигнал поступает на вход разрешения выдачи первого регистра 4 адреса и в результате

5 адрес поступает на вход дешифратора 7 зоны. При совпадении адреса, поступающего с регистра А с адресом блока 1 памяти на выходе дешифратора вырабатывается сигнал низкого напряжения, а в случае яесов0 падения остается высокий уровень напряжения. Рассмотрим каждый из этих случаев.

Если адрес в регистре 4 не совпадает с адресом блока 1 памяти (то есть проходит

5 обращение не к устройству сопряжения) на выходе дешифратора останется высокий уровень напряжения. В результате на выходе элемента ИЛИ НЕ 20 и дальше будет присутствовать сигнал низкого уровня, по0 ступающий на входы разрешения первого коммутатора 2 магистрали, первого 8, третьего 10 и пятого 12 элемента И. В результате информационны входы-выходы блока памяти будут отключены от информационно5 адресной шины 26 первой магистрали, а на выходах первого 14, третьего 16 и пятого 18 элементов И будет сигнал низкого урорня вне зависимости от уровней напряжения на входах чтения 22, записи 23 и выходе синх0 ронизации обмена блока памяти 1, Сигнал низкого уровня поступает также па второй вход первого элемента И ИЛИ НЕ 16. По истечении времени дешифрации адреса на выходе первого элемента задержки 18 поя5 вится низкий уровень напряжения (так как на его входе низкий уровень напряжения с выхода первого элемента И-ИЛИ-НЕ 16) который поступает на четвертый вход элемента И-ИЛИ-НЕ 16. Поэтому на выходе

0 элемента И-ИЛИ-НЕ 16 появляется сигнал высокого уровня напряжения. Высокий уровень напряжения. Высокий уровень напряжения на выходе элемента И-ИЛИ-НЕ 16 сохранится до поступления следующего

5 сигнала синхронизации обмена на линию 28, После установки на выходе элемента И- ИЛИ-НЕ 16 сигнала высокого уровня устройство готово для принятия сигнала синхронизации обмена со стороны второй магистрали.

В случае совпадения адреса в регистре 4 с адресом блока памяти 1, через определенное время после появления сигнала низкого уровня на выходе элемента И-ИЛИ-НЕ 16 на выходе дешифратора 7 появится сигнал низкого уровня и на выходе элемента ИЛИ-НЕ 20 появится сигнал высокого уровня, Сигнал высокого уровня с выхода элемента ИЛИ-НЕ 20 поступает на первый вход первого элемента И ИЛИ-НЕ 16, обеспечивая на его выходе сигнал логического нуля, вне зависимости от уровня сигнала на четвертом входе (то есть на выходе первого элемента задержки 18). В данном случае сигнал низкого уровня будет присутствовать на выходе элемента И-ИЛИ-НЕ 16 до окончания сигнала синхронизации обмена на линии 28. Сигнал высокого уровня с выхода элемента ИЛИ-НЕ 20 поступает также на разрешающие входы первого коммутатора магистрали 2, первого 14, третьего 16 и пятого 18 элементов И. При этом информационные входы выходы блока 1 памяти будутподключеныкинформационно-адресной шине 26 первой магистрали, сигналы чтения,и записи с первой магистрали, поступающие по линиям 22 и 23 проходят в блок 1 памяти, а выходной сигнал синхронизации блока 1 памяти поступает на линию ответа 30 первой магистрали. По окончании цикла обращения к блоку 1 памяти снимается высокий уровень сигнала синхронизации обмена на линии 28. При этом на выходе седьмого элемента И 14 устанавливается низкий уровень напряжения, а на выходе первого элемента И-ИЛИ-НЕ 16 устанавливается высокий уровень напряжения, который проходит на выход элемента ИЛИ 20. В результате информационные входы выходы, входы записи, чтения и выход синхронизации блока памяти отключаются от первой магистрали. Устройство готово к следующему циклу обращения к блоку 1 памяти.

Работа устройства для случая появления сигнала синхронизации обмена со стороны второй магистрали по линии 29, при отсутствии единичного уровня на линии синхронизации обмена 28, будет происходить аналогично с той разницей, что будут задействованы элементы И-ИЛИ-НЕ 17, И19, 11, 13 и 15, элементы ИЛИ-НЕ 21 и элемент 19 задержки.

Рассмотрим случай появления сигнала синхронизации обмена на одной из магистралей, если присутствует сигнал синхрони- зации обмена на другой магистрали.

Если приходит сигнал синхронизации обмена на линию 28, при наличии сигнала синхронизации обмена на линии 29, то до

момента присутствия на выходе второго элемента И-ИЛИ-НЕ 17 нулевого уровня напряжения сигнал с линии 28 будет заблокирован на седьмом элементе 14. После

установки на выходе второго элемента сигнала высокого уровня работы устройства будет происходит как и для случая отсутствия сигнала синхронизации обмена на линии 29. Если же приходит сигнал синхронизации

0 обмена на линию 29, при наличии сигнала синхронизации обмена на линии 28, то до момента присутствия на выходе первого элемента И-ИЛИ-НЕ 16 нулевого уровня напряжения сигнала с линий 29 будет забло5 кирован на седьмом элемента 15.

Для случая одновременно появления сигналов синхронизации обмена на линиях 28 и 29 элементы И 14 и элементы И-ИЛИ- НЕ 16 и 17 представляют триггер, для кото0 рого нулевой уровень может появиться только на выходе одного из элементов И- ИЛИ-НЕ 16 и 17. Сигнал низкого уровня с выхода одного элемента установится сигнал высокого уровня на выходе другого элемен5 та. Дальнейшая работа устройства аналогична как и в случае Появления сигнала синхронизации обмена на одной из магистралей при присутствии этого сигнала на другой магистрали.

0

Формула изобретения Устройство для сопряжения двух магистралей, содержащее блок памяти, коммута- торы магистралей, первый и второй

5 регистры адреса, блок коммутаторов, состоящий из дешифратора зоны, с первого по шестой элементы И, причем информационные входы первого и второго регистров адреса соединены соответственно с первыми

0 группами информационных входов-выходов первого и второго коммутаторов магистралей с информационно-адресными шинами первой и второй магистралей, группа информационных входов-выходов блока

5 соединена с вторыми группами информационных входов первого и второго коммутаторов магистралей, отличающееся тем, что, с целью упрощения, в устройство введены первый и второй элементы И-ИЛИ-НЕ,

0 первый и второй элементы задержки, первый и второй элементы ИЛИ-НЕ, причем выходы первого и второго регистров адреса соединены с группой адресных входов блока памяти и информационным входам де5 шифратора зоны, выходы первого и второго элементов И соединены с входом чтения блока памяти, а первые входы первого и второго элементов И - с шинами чтения первой и второй магистралей и с первыми входами направления обмена первого и второго коммутаторов магистралей, выходы третьего и четвертого элементов И соединены с входом записи блока памяти, а первые входы третьего и четвертого элементов И - с шинами записи первой и второй магистралей и с вторыми входами направления обме- на первого и второго коммутаторов магистралей, синхронизирующий выход блока памяти подключен к первым входам пятого и шестого элементов И, выходы которых соединены с шинами ответа первой и второй магистралей, выход дешифратора зоны подключен к первым входам первого и второго элементов ИЛИ-НЕ, второй вход первого элемента ИЛИ-НЕ соединен с выходом первого элемента И-ИЛИ-НЕ, первым входом седьмого элемента И, входом разрешения выдачи информации первого регистра адреса и входом первого элемента задержки, а выход первого элемента ИЛИ- НЕ подключен к первому входу первого элемента И-ИЛИ-НЕ, вторым входам первого, третьего w пятого элементов И и к разрешающему входу первого коммутатора магист- ргтей, второй вход второго элемента

ИЛИ-НЕ соединен с выходом второго элемента И-ИЛИ-НЕ, первым входом восьмого элемента И, входом разрешения выдачи информации второго регистра адреса л входом второго элемента задержки, а выход второго элемента ИЛИ-НЕ подключен к первому входу второго элемента И-ИЛИ-НЕ, вторым входам второго, четвертого и шестого элементов И и к разрешающему входу

второго коммутатора магистралей, второй и третий входы первого элемента И-ИЛИ-НЕ объединены и подключены к выходу восьмого элемента И, второй и третий входы второго элемента И-ИЛИ-НЕ объединены и

подключены к выходу седьмого элемента И, четвертые входы первого и второго элементов И-ИЛИ-НЕ соединены с выходами первого и второго элементов задержки соответственно, второй вход восьмого элемента И подключен к синхровходу первого регистра адреса и шине управления обменом первой магистрали, второй вход седьмого элемента И подключен к синхровходу второго регистра адреса и шине управления

обменом второй магистрали.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619286A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619285A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных система. Цель изобретения - упрощение устройства за счет изменения технической реализации алгоритма обмена. Устройство содержит блок памяти, два коммутатора магистралей, два регистра адреса, блок коммутаторов, состоящий из дешифратора зоны, восьми элементов И, двух элементов 2И-ИЛИ-НЕ, двух элементов задержки, двух элементов ИЛИ-НЕ. 1 ил.

А I--jj----uJ:

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1990-03-21—Подача