Изобретение относится к электросвязи и может быть использовано в системах передачи информации с использованием параллельных каналов связи.

Целью изобретения является повышение достоверности приема информации.

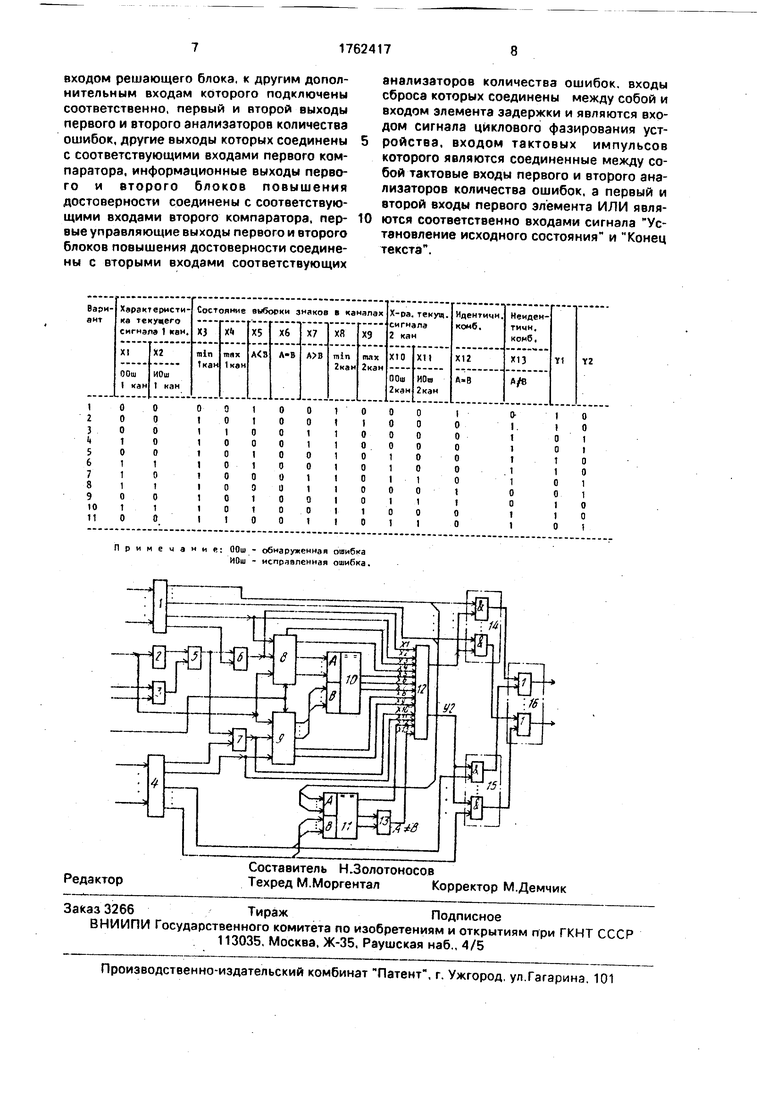

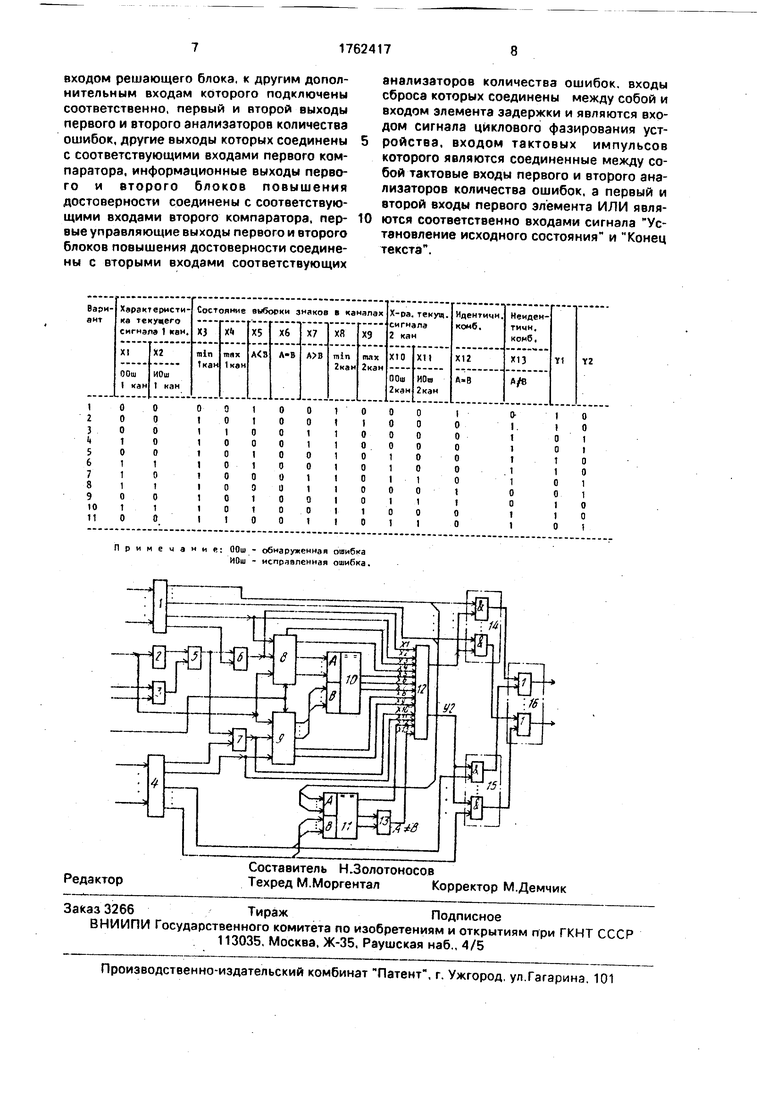

На чертеже представлена электрическая схема устройства.

Устройство содержит первый блок повышения достоверности 1, элемент задержки 2, первый элемент ИЛИ 3, второй блок повышения достоверности 4, триггер 5, первый элемент И 6, второй элемент И 7, первый анализатор количества ошибок 8, второй анализатор количества ошибок 9, первый компаратор 10, второй компаратор 11, решающий блок 12. второй элемент ИЛИ 13, первый блок элементов И 14, второй

блок элементов И 15, блок элементов ИЛИ 16.

Первый блок повышения достоверности 1 последовательно соединен с первым блоком элементов И 14 и блоком элементов ИЛИ 16, другие входы которого соединены с выходами второго блока повышения достоверности 4 через второй блок элементов И 15. Первые управляющие выходы первого 1 и второго 4 блоков повышения достоверности соединены с соответствующими входами решающего блока 12, выходы которого соединены соответственно с другими входами первого 14 и второго 15 блоков элементов И, а выход элемента задержки 2 соединен с единичным входом триггера 5, нулевой вход которого соединен с выходом первого элемента ИЛИ 3. Единичный выход триггера 5 соединен с первыми входами

v4 О Ю N

-л

первого 6 и второго 7 элементов И, второй вход каждого из которых соединен со вторым управляющим выходом соответствующего блока повышения достоверности 1 и 4. Выход первого элемента И 6 соединен с первым входом первого анализатора количества ошибок 8 и с соответствующим дополнительным входом решающего блока 12, выход второго элемента И 7 соединен с первым входом второго анализатора количества ошибок 9 и с соответствующим дополнительным входом решающего блока 12, к другим дополнительным входам которого подключены соответственно первый, второй и третий выходы первого компаратора 10 и первый выход второго компаратора 11, второй и третий выходы которого через второй элемент ИЛИ 13 соединены с соответствующими дополнительными входами решающего блока 12, к другим дополнительным входам которого подключены, соответственно первый и второй выходы первого 8 и второго 9 анализаторов количества ошибок, другие выходы которых соединены с соответствующими входами первого компаратора 10. Информационные выходы первого 1 и второго 4 блоков повышения достоверности соединены с соответствующими входами второго компаратора 11. Первые управляющие выходы первого 1 и второго 4 блоков повышения достоверности соединены со вторыми входами соответствующих анализаторов количества ошибок 8 и 9, входы сброса которых соединены между собой и со входом элемента задержки и является входом сигнала циклового фазирования устройства, входом тактовых импульсов которого являются соединенные между собой тактовые входы первого 8 и второго 9 анализаторов количества ошибок, а первый и второй входы первого элемента ИЛИ 3 являются соответственно входами сигнала установления исходного состояния и сигнала КОНЕЦ ТЕКСТА

Устройство работает следующим образом.

Исходное состояние устройства устанавливается сигналом УИС (установка исходного состояния), который переводит триггер 5 в нулевое состояние (нулевой потенциал на единичном выходе).

Поступлению на блоки повышения достоверности комбинаций информационного сообщения предшествует появление сигнала циклового фазирования (ЦФ), который осуществляет установку исходного состояния (СБРОС) первого 8 и второго 9 анализаторов количества ошибок. Воздействуя через элемент задержки 2 сигнал ЦФ устанавливает триггер 5 в единичное состояние, благодаря чему открываются по одному из входов первый 6 и второй 7 элементы И. Вслед за сигналом ЦФ на блоки повышения достоверности 1,4 начинают параллельно поступать комбинации сообщения.

С информационных выходов первого 1 (ПД-1) и второго 4 (ПД-2) блоков повышения достоверности на первые входы соответственно первого 14 и второго 15 блоков элементов И поступают информационные комбинации.

В случае обнаружения в очередной комбинации ошибки на соответствующих служебных выходах блоков ПД-1 и ПД-2

выставляются сигналы ООш (обнаруженная

ошибка) и ИОш (если ошибка обнаружена и

исправлена благодаря избыточности кода),

Сигнал ООш с выхода блока 1 (ПД-1)

через открытый по первому входу первый

элемент И б поступит на вход первого 8 анализатора количества ошибок. Аналогично воздействие сигнала ООш с выхода блока 4 (ПД-2), через второй элемент И 7 поступающего на второй 9 анализатор количества

ошибок.

Кроме того, сигналы ООш и ИОш с выходов ПД-1 и ПД-2 поступают на решающий блок 12 - соответственно входы XI, ХЮ, Х2, XII.

Первый и второй анализаторы количества ошибок 8, 9 подсчитывают количество ошибок в пределах некоторой заданной выборки знаков, при этом сигналы ИОш соответственно уменьшают это количество,

Для подсчета количества ошибок анализаторы 8, 9 содержат счетчики, разрядные выходы которых поступают на группы входов А и В первого 10 компаратора, который производит сравнение этих чисел, формируя один из трех возможных результирующих сигналов:

, , .

На выходах анализаторов количества ошибок 8, 9 возникают также сигналы, качественно оценивающие число ошибок относительно заданного уровня - минимальное (mIn) и максимальное (max).

Сигналы mln, max поступают на входы ХЗ, Х4.Х8, Х9 решающего блока 12; один из сигналов , , поступает соответственно на входы Х5. Хб, Х7.

Второй компаратор 11 производит сравнение самих информационных комби- наций с выходом ПД-1 (1) и ПД-2 (4).

К решающему блоку 12 поступит либо сигнал с выхода второго компаратора 11, либо сигнал АЈ8 - с выхода второго элемента ИЛИ 13.

Наличие альтернативного сигнала увеличивает надежность функционирования устройства.

Итак, поступление информационных комбинаций сопровождается появлением на входе решающего блока 12 комбинации из тринадцати служебных сигналов, на основе которых в решающем блоке 13 вырабатывается один из двух выходных сигналов - У1илиУ2.

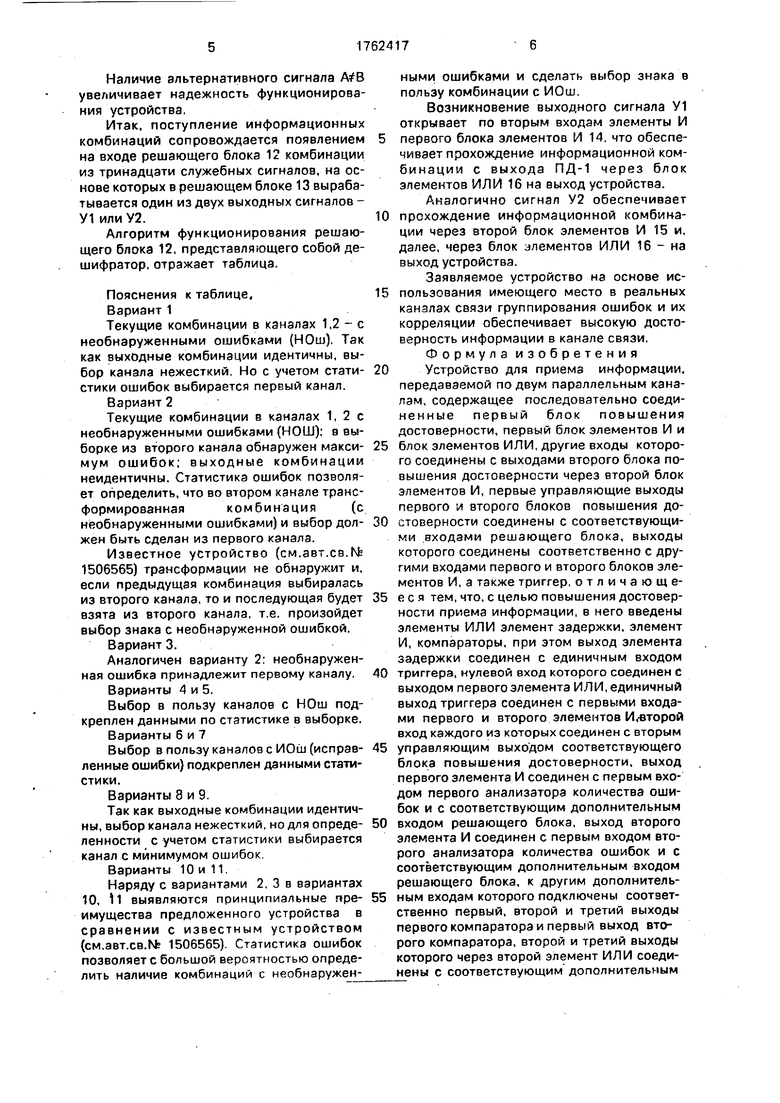

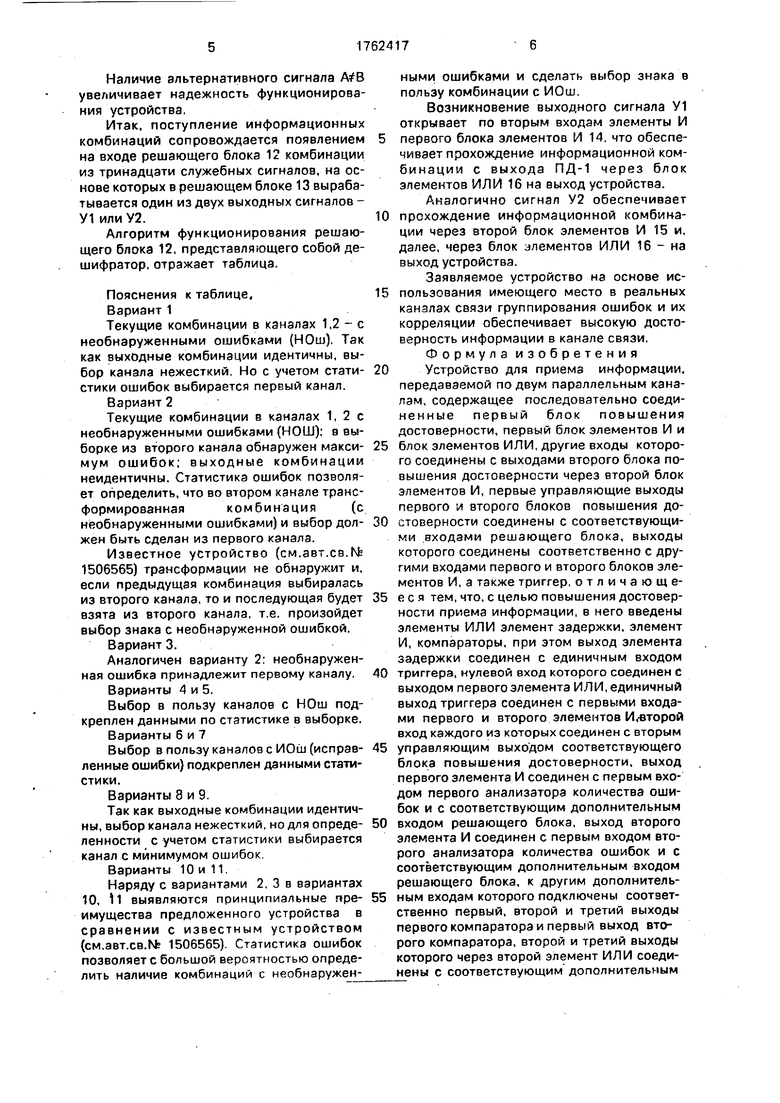

Алгоритм функционирования решающего блока 12, представляющего собой дешифратор, отражает таблица.

Пояснения к таблице,

Вариант 1

Текущие комбинации в каналах 1,2 - с необнаруженными ошибками (НОш). Так как выходные комбинации идентичны, выбор канала нежесткий. Но с учетом стати- стики ошибок выбирается первый канал.

Вариант 2

Текущие комбинации в каналах 1, 2 с необнаруженными ошибками (НОШ); в выборке из второго канала обнаружен макси- мум ошибок; выходные комбинации неидентичны. Статистика ошибок позволяет определить, что во втором канале трансформированнаякомбинация (с необнаруженными ошибками) и выбор дол- жен быть сделан из первого канала.

Известное устройство (см.авт.св.fsb 1506565) трансформации не обнаружит и, если предыдущая комбинация выбиралась из второго канала, то и последующая будет взята из второго канала, т.е. произойдет выбор знака с необнаруженной ошибкой.

Вариант 3.

Аналогичен варианту 2; необнаруженная ошибка принадлежит первому каналу.

Варианты 4 и 5.

Выбор в пользу каналов с НОш подкреплен данными по статистике в выборке.

Варианты б и 7

Выбор в пользу каналов с ИОш (исправ- ленные ошибки} подкреплен данными статистики.

Варианты 8 и 9.

Так как выходные комбинации идентичны, выбор канала нежесткий, но для опреде- ленности с учетом статистики выбирается канал с минимумом ошибок.

Варианты 10 и 11.

Наряду с вариантами 2, 3 в вариантах 10, 11 выявляются принципиальные яре- имущества предложенного устройства в сравнении с известным устройством (см.авт.св.М; 1506565). Статистика ошибок позволяет с большой вероятностью определить наличие комбинаций с необнаруженными ошибками и сделать выбор знака в пользу комбинации с ИОш.

Возникновение выходного сигнала У1 открывает по вторым входам элементы И первого блока элементов И 14, что обеспечивает прохождение информационной ком- бинации с выхода ПД-1 через блок элементов ИЛИ 16 на выход устройства.

Аналогично сигнал У2 обеспечивает прохождение информационной комбинации через второй блок элементов И 15 и, далее, через блок элементов ИЛИ 16 - на выход устройства.

Заявляемое устройство на основе использования имеющего место в реальных каналах связи группирования ошибок и их корреляции обеспечивает высокую достоверность информации в канале связи. Формула изобретения Устройство для приема информации, передаваемой по двум параллельным каналам, содержащее последовательно соединенные первый блок повышения достоверности, первый блок элементов И и блок элементов ИЛИ, другие входы которого соединены с выходами второго блока повышения достоверности через второй блок элементов И, первые управляющие выходы первого и второго блоков повышения достоверности соединены с соответствующими входами решающего блока, выходы которого соединены соответственно с другими входами первого и второго блоков элементов И, а также триггер, отличающееся тем, что, с целью повышения достоверности приема информации, в него введены элементы ИЛИ элемент задержки, элемент И, компараторы, при этом выход элемента задержки соединен с единичным входом триггера, нулевой вход которого соединен с выходом первого элемента ИЛИ, единичный выход триггера соединен с первыми входами первого и второго элементов И,«торой вход каждого из которых соединен с вторым управляющим выходом соответствующего блока повышения достоверности, выход первого элемента И соединен с первым входом первого анализатора количества ошибок и с соответствующим дополнительным входом решающего блока, выход второго элемента И соединен с первым входом второго анализатора количества ошибок и с соответствующим дополнительным входом решающего блока, к другим дополнительным входам которого подключены соответственно первый, второй и третий выходы первого компаратора и первый выход второго компаратора, второй и третий выходы которого через второй элемент ИЛИ соединены с соответствующим дополнительным

входом решающего блока, к другим дополнительным входам которого подключены соответственно, первый и второй выходы первого и второго анализаторов количества ошибок, другие выходы которых соединены с соответствующими входами первого компаратора, информационные выходы первого и второго блоков повышения достоверности соединены с соответствующими входами второго компаратора, первые управляющие выходы первого и второго блоков повышения достоверности соединены с вторыми входами соответствующих

анализаторов количества ошибок, входы сброса которых соединены между собой и входом элемента задержки и являются входом сигнала циклового фазирования устройства, входом тактовых импульсов которого являются соединенные между собой тактовые входы первого и второго анализаторов количества ошибок, а первый и второй входы первого элемента ИЛИ являются соответственно входами сигнала Установление исходного состояния и Конец текста.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью | 2018 |

|

RU2696329C2 |

| Устройство автовыбора | 1991 |

|

SU1786672A1 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ ПО ДВУМ ПАРАЛЛЕЛЬНЫМ КАНАЛАМ СВЯЗИ В СИСТЕМЕ ПЕРЕДАЧИ ДАННЫХ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ | 2018 |

|

RU2689809C1 |

| Логический анализатор | 1980 |

|

SU890396A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

Изобретение относится к электросвязи и может быть использовано в системах передачи информации с использованием параллельных каналов связи. Устройство для приема информации передаваемой по двум параллельным каналам связи содержит первый блок повышения достоверности 1, элемент задержки 2. первый элемент ИЛИ 3, второй блок повышения достоверности 4. триггер 5, первый и второй элементы И 6 и 7, первый и второй анализаторы количества ошибок 8 и 9, первый и второй компараторы 10 и 11, решающий блок 12. второй элемент ИЛИ 13, первый и второй блоки элементов И 14 и 15 и блок элементов ИЛИ 16. Устройство обеспечивс ет повышение достоверности приема информации благодаря использованию факта корреляции ошибок в реальных каналах связи и получения на этой основе дополнительных данных при выборе наиболее надежной комбинации при параллельном приеме. 1 табл.,1 ил. сл с

Примечание: ООш - обнаруженная ошибка ИОш - исправленная ошибка.

Г

| Устройство для приема информации, передаваемой по двум параллельным каналам связи | 1986 |

|

SU1506565A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-09-15—Публикация

1990-08-06—Подача