-o2S

фиг{

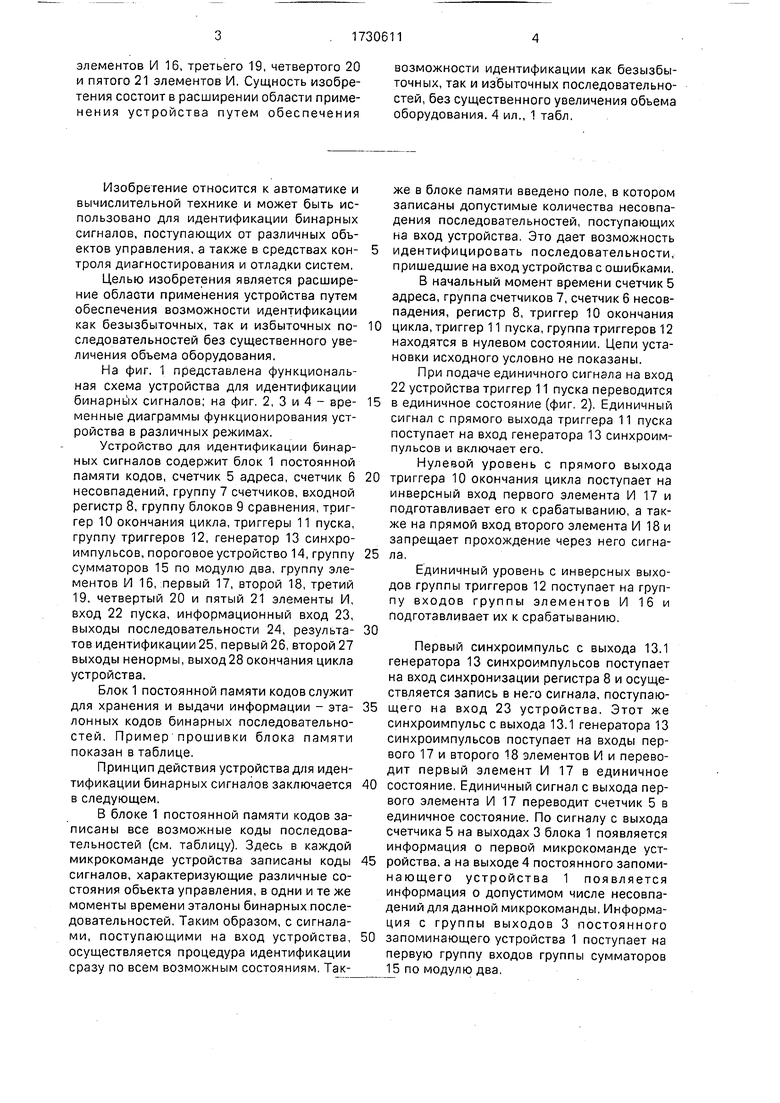

элементов И 16, третьего 19, четвертого 20 и пятого 21 элементов И. Сущность изобретения состоит в расширении области применения устройства путем обеспечения

возможности идентификации как безызбыточных, так и избыточных последовательностей, без существенного увеличения объема оборудования. 4 ил., 1 табл.

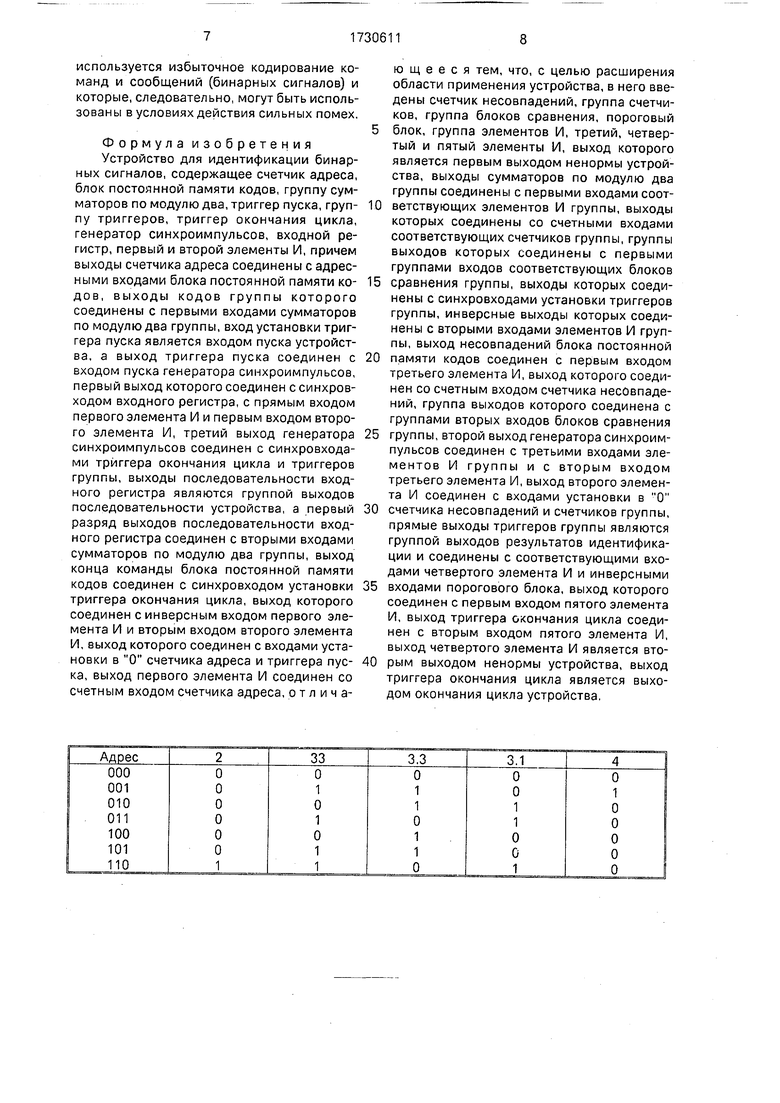

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации аналоговых сигналов | 1991 |

|

SU1789985A1 |

| Устройство для контроля аналогового сигнала | 1990 |

|

SU1797097A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля сигналов | 1989 |

|

SU1667078A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для идентификации бинарных сигналов, поступающих от различных объектов управления, а также в средствах контроля, диагностирования и отладки систем. Цель изобретения - расширение области применения устройства. Цель изобретения достигается введением счетчика 6 несовпадений, группы счетчиков 7, группы блоков 9 сравнения, порогового блока 14, группы

Изобретение относится к автоматике и вычислительной технике и может быть использовано для идентификации бинарных сигналов, поступающих от различных объектов управления, а также в средствах кон- троля диагностирования и отладки систем.

Целью изобретения является расширение области применения устройства путем обеспечения возможности идентификации как безызбыточных, так и избыточных по- следовательностей без существенного увеличения объема оборудования,

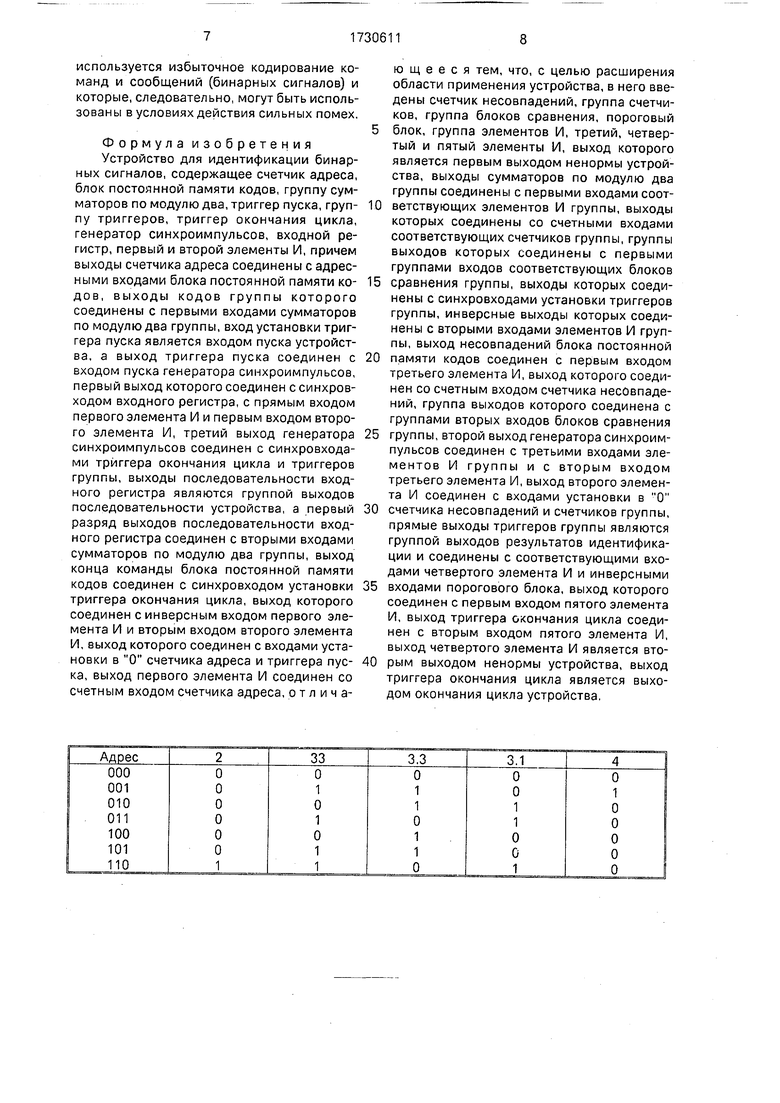

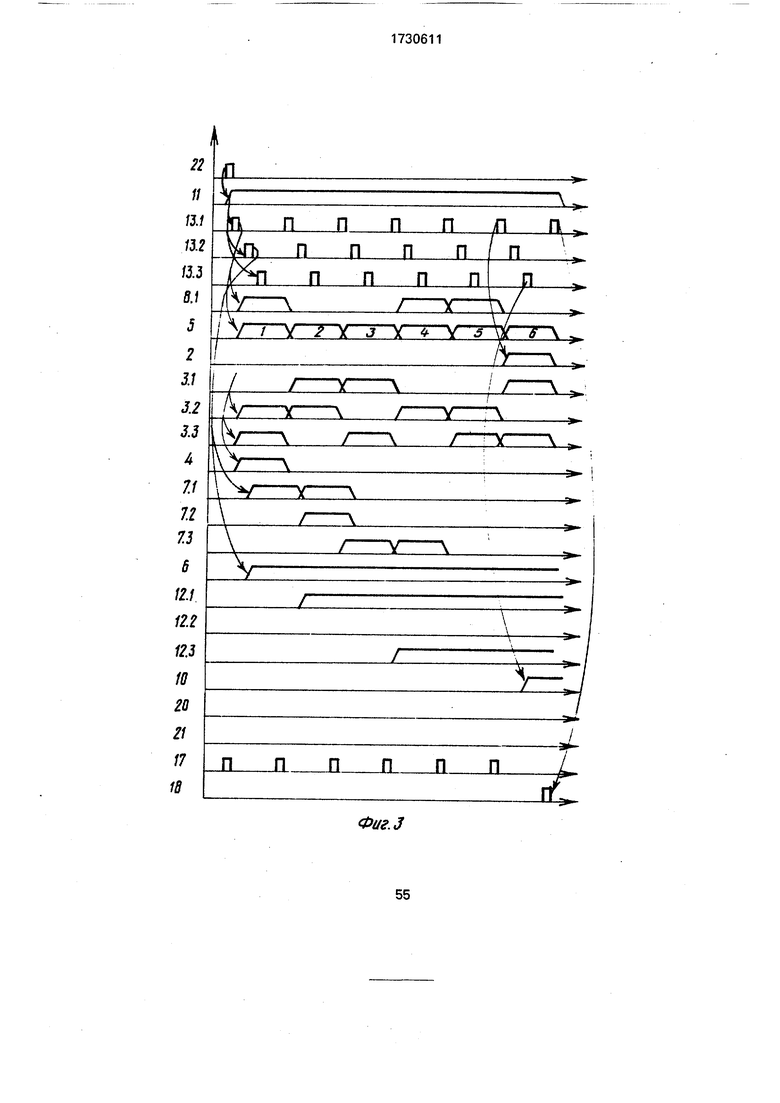

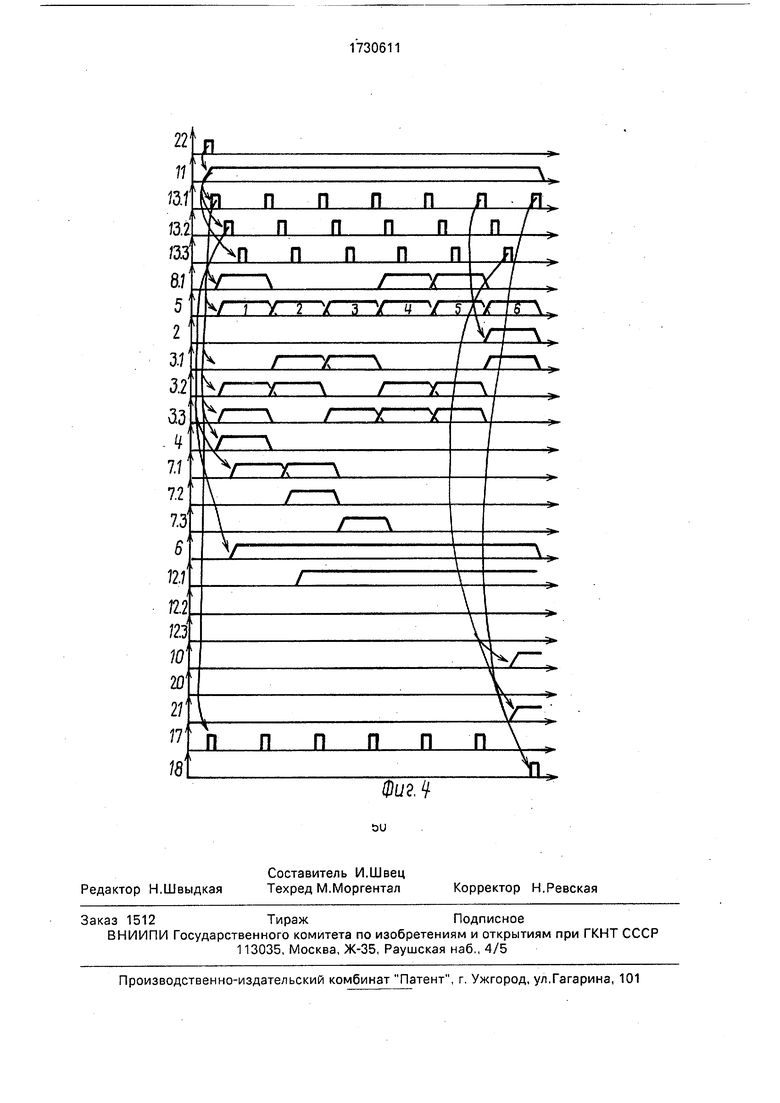

На фиг. 1 представлена функциональная схема устройства для идентификации бинарных сигналов; на фиг. 2, 3 и 4 - вре- менные диаграммы функционирования устройства в различных режимах.

Устройство для идентификации бинарных сигналов содержит блок 1 постоянной памяти кодов, счетчик 5 адреса, счетчик 6 несовпадений, группу 7 счетчиков, входной регистр 8, группу блоков 9 сравнения, триггер 10 окончания цикла, триггеры 11 пуска, группу триггеров 12, генератор 13 синхроимпульсов, пороговое устройство 14, группу сумматоров 15 по модулю два, группу элементов I/I 16, первый 17, второй 18, третий 19, четвертый 20 и пятый 21 элементы И, вход 22 пуска, информационный вход 23, выходы последовательности 24, результа- тов идентификации 25, первый 26, второй 27 выходы ненормы, выход 28 окончания цикла устройства.

Блок 1 постоянной памяти кодов служит для хранения и выдачи информации - эта- лонных кодов бинарных последовательностей. Пример прошивки блока памяти показан в таблице.

Принцип действия устройства для идентификации бинарных сигналов заключается в следующем.

В блоке 1 постоянной памяти кодов записаны все возможные коды последовательностей (см. таблицу). Здесь в каждой микрокоманде устройства записаны коды сигналов, характеризующие различные состояния объекта управления, в одни и те же моменты времени эталоны бинарных последовательностей. Таким образом, с сигналами, поступающими на вход устройства, осуществляется процедура идентификации сразу по всем возможным состояниям. Также в блоке памяти введено поле, в котором записаны допустимые количества несовпадения последовательностей, поступающих на вход устройства. Это дает возможность идентифицировать последовательности, пришедшие на вход устройства с ошибками.

В начальный момент времени счетчик 5 адреса, группа счетчиков 7, счетчик 6 несовпадения, регистр 8, триггер 10 окончания цикла, триггер 11 пуска, группа триггеров 12 находятся в нулевом состоянии. Цепи установки исходного условно не показаны.

При подаче единичного сигнала на вход 22 устройства триггер 11 пуска переводится в единичное состояние (фиг. 2). Единичный сигнал с прямого выхода триггера 11 пуска поступает на вход генератора 13 синхроимпульсов и включает его.

Нулевой уровень с прямого выхода триггера 10 окончания цикла поступает на инверсный вход первого элемента И 17 и подготавливает его к срабатыванию, а также на прямой вход второго элемента И 18 и запрещает прохождение через него сигнала.

Единичный уровень с инверсных выходов группы триггеров 12 поступает на группу входов группы элементов И 16 и подготавливает их к срабатыванию.

Первый синхроимпульс с выхода 13.1 генератора 13 синхроимпульсов поступает на вход синхронизации регистра 8 и осуществляется запись в него сигнала, поступающего на вход 23 устройства. Этот же синхроимпульс с выхода 13.1 генератора 13 синхроимпульсов поступает на входы первого 17 и второго 18 элементов И и переводит первый элемент И 17 в единичное состояние. Единичный сигнал с выхода первого элемента И 17 переводит счетчик 5 в единичное состояние. По сигналу с выхода счетчика 5 на выходах 3 блока 1 появляется информация о первой микрокоманде устройства, а на выходе 4 постоянного запоми- нающего устройства 1 появляется информация о допустимом числе несовпадений для данной микрокоманды. Информация с группы выходов 3 постоянного запоминающего устройства 1 поступает на первую группу входов группы сумматоров 15 по модулю два.

Сигнал, пришедший на вход устройства с выхода 8.1 регистра 8, поступает на вторую группу входов группы сумматоров 15 по модулю два. При этом в группе сумматоров 15 по модулю два осуществляется сравнение первых бинарных сигналов всех эталонных последовательностей, хранящихся в постоянном запоминающем устройстве.

На выходах тех сумматоров по модулю два 15,1, где произошло несравнение, появляются сигналы единичного уровня, которые поступают на соответствующие входы группы элементов И 16.

По синхроимпульсу с выхода 13.2 генератора 13 синхроимпульсов на соответствующих выходах группы элементов И 16.1, на которых произошло несравнение, появляются сигналы единичного уровня.

Эти сигналы поступают на соответствующие счетные входы группы счетчиков 7.1 и переадресуют их.

По этому же синхроимпульсу с выхода 13.2 генератора 13 синхроимпульсов на выходе третьего элемента И 19 поя вляется сиг- нал единичного уровня. Этот сигнал поступает на счетный вход счетчика 16 несовпадений и переадресует его.

Информация о числах несовпадений с выходов группы счетчиков 7 поступает на первые входы группы блоков 9 сравнения. На вторые входы группы блоков 9 сравнения поступает информация с выхода счетчика 6 несовпадений о допустимом числе несовпадений.

На выходах тех блоков сравнения, где число несовпадений больше допустимого числа несовпадений, появляются сигналы единичного уровня, которые поступают на 1-входы блока триггеров 12.

По синхроимпульсу с выхода 13.3 генератора синхроимпульсов 13 триггеры 12.i, на 1-входы которых поступили единичные сигналы, переводятся в единичное состояние.

После этого из процедуры идентификации исключаются те бинарные последовательности, где на первом же этапе произошло превышение допустимого числа несовпадений, Это возможно благодаря тому, что инверсные входы триггеров подключены к третьим входам группы элементов И 16.

Второй импульс с выхода 13.1 генератора синхроимпульсов через первый элемент И 17 поступает на счетный вход счетчика адреса 5 и переадресует его. Информация об адресе следующей микрокоманды с группы выходов счетчика 5 адреса поступает на группу адресных входов блока 1 постоянной памяти и переадресует его.

Дальнейшая работа устройства для идентификации бинарных сигналов осуществляется по указанному алгоритму.

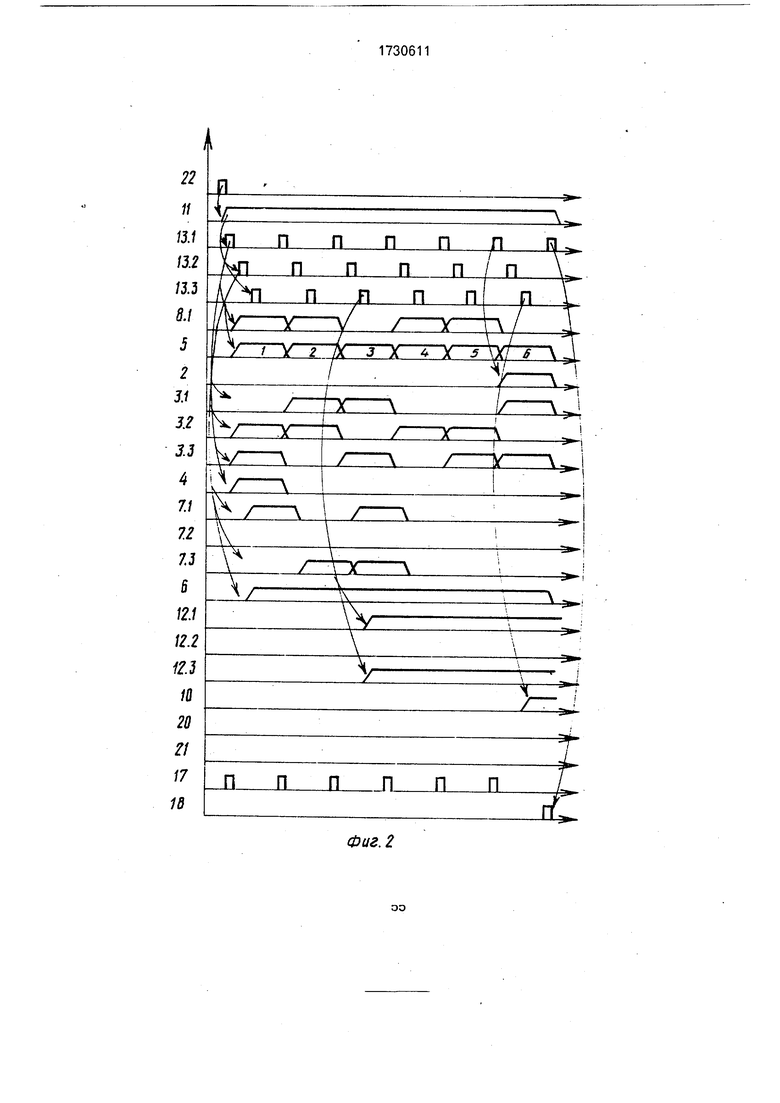

В процессе функционирования возможен прием последовательностей, в которых искажено допустимое число символов (в данном случае не более одного). Несмотря на это, устройство правильно идентифицирует последовательность с допустимым чис0 лом искажений (фиг. 3).

Останов устройства происходит следующим образом,

В последней микрокоманде устройства на выходе 2 конца команды блока 1 присут5 ствует сигнал единичного уровня. По импульсу с выхода триггера 10 окончания цикла поступает на инверсный вход первого элемента И 17 и на вход второго элемента И 18. По очередному синхроимпульсу с выхода

0 13.1 генератора 13 синхроимпульсов на выходе второго элемента И 18 появляется единичный сигнал, который поступая на входы установки в нуль счетчика 5, триггера 11 пуска, счетчика 6 несовпадений, группы

5 счетчиков 7, обнуляет их.

Единичный сигнал с выхода триггера 10 окончания цикла поступает на выход 28 устройства, сигнализируя об окончании цикла, а также на вход пятого элемента И 21, на

0 второй вход которого поступает информация с выхода порогового устройства 14 о возможности идентификации. Информация с выхода пятого элемента И 21 поступает на выход 27 устройства. Если на выходе 27

5 устройства присутствует единичный сигнал, то идентификацию повести невозможно. Это значит, что идентификация произошла по двум последовательностям и результат определить невозможно (фиг. 4).

0 Если до окончания цикла на выходе 26 устройства появляется единичный сигнал, снимаемый с выхода четвертого элемента И 20, то -это свидетельствует о том, что идентификация не произошла ни с одной после5 довательностью, хранящейся в блоке 1.

Это повышает быстродействие устройства.

Информация о результатах идентификации снимается с выходов группы триггеров

0 12 и поступает на выход 25 устройства.

Информацию о последовательности, поступившей на вход устройства, можно снять с группы выходов 24 устройства.

На фиг. 3 представлен случай, когда

5 происходит идентификация последовательности, пришедшей на вход устройства с ошибкой.

Техническое преимущество предлагаемого устройства состоит в расширении области применения на системы, в которых

используется избыточное кодирование команд и сообщений (бинарных сигналов) и которые, следовательно, могут быть использованы в условиях действия сильных помех.

Формула изобретения Устройство для идентификации бинарных сигналов, содержащее счетчик адреса, блок постоянной памяти кодов, группу сумматоров по модулю два, триггер пуска, труп- пу триггеров, триггер окончания цикла, генератор синхроимпульсов, входной регистр, первый и второй элементы И, причем выходы счетчика адреса соединены с адресными входами блока постоянной памяти ко- дов, выходы кодов группы которого соединены с первыми входами сумматоров по модулю два группы, вход установки триггера пуска является входом пуска устройства, а выход триггера пуска соединен с входом пуска генератора синхроимпульсов, первый выход которого соединен с синхров- ходом входного регистра, с прямым входом первого элемента И и первым входом второго элемента И, третий выход генератора синхроимпульсов соединен с синхровхода- ми триггера окончания цикла и триггеров группы, выходы последовательности входного регистра являются группой выходов последовательности устройства, а первый разряд выходов последовательности входного регистра соединен с вторыми входами сумматоров по модулю два группы, выход конца команды блока постоянной памяти кодов соединен с синхровходом установки триггера окончания цикла, выход которого соединен с инверсным входом первого элемента И и вторым входом второго элемента И, выход которого соединен с входами установки в О счетчика адреса и триггера пус- ка, выход первого элемента И соединен со счетным входом счетчика адреса, отличающееся тем, что, с целью расширения области применения устройства, в него введены счетчик несовпадений, группа счетчиков, группа блоков сравнения, пороговый блок, группа элементов И, третий, четвертый и пятый элементы И, выход которого является первым выходом ненормы устройства, выходы сумматоров по модулю два группы соединены с первыми входами соответствующих элементов И группы, выходы которых соединены со счетными входами соответствующих счетчиков группы, группы выходов которых соединены с первыми группами входов соответствующих блоков сравнения группы, выходы которых соединены с синхровходами установки триггеров группы, инверсные выходы которых соединены с вторыми входами элементов И группы, выход несовпадений блока постоянной памяти кодов соединен с первым входом третьего элемента И, выход которого соединен со счетным входом счетчика несовпадений, группа выходов которого соединена с группами вторых входов блоков сравнения группы, второй выход генератора синхроимпульсов соединен с третьими входами элементов И группы и с вторым входом третьего элемента И, выход второго элемента И соединен с входами установки в О счетчика несовпадений и счетчиков группы, прямые выходы триггеров группы являются группой выходов результатов идентификации и соединены с соответствующими входами четвертого элемента И и инверсными входами порогового блока, выход которого соединен с первым входом пятого элемента И, выход триггера окончания цикла соединен с вторым входом пятого элемента И, выход четвертого элемента И является вторым выходом ненормы устройства, выход триггера окончания цикла является выходом окончания цикла устройства,

fr

V

п п п п п 0ППП / П

П Л П П

/У 2 /X 3 X 4Х S XIJ

Фиг. 2

П

л

л

П П П П

П П П П

лаап.

Л

л

П

р

и

П

т

±

Л

Л

Фиг.З

ФигЛ

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1244666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1091346A2 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Устройство для контроля сигналов | 1989 |

|

SU1667078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-12-08—Подача