Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах для частотных измерений.

Целью изобретения является упрощение, :

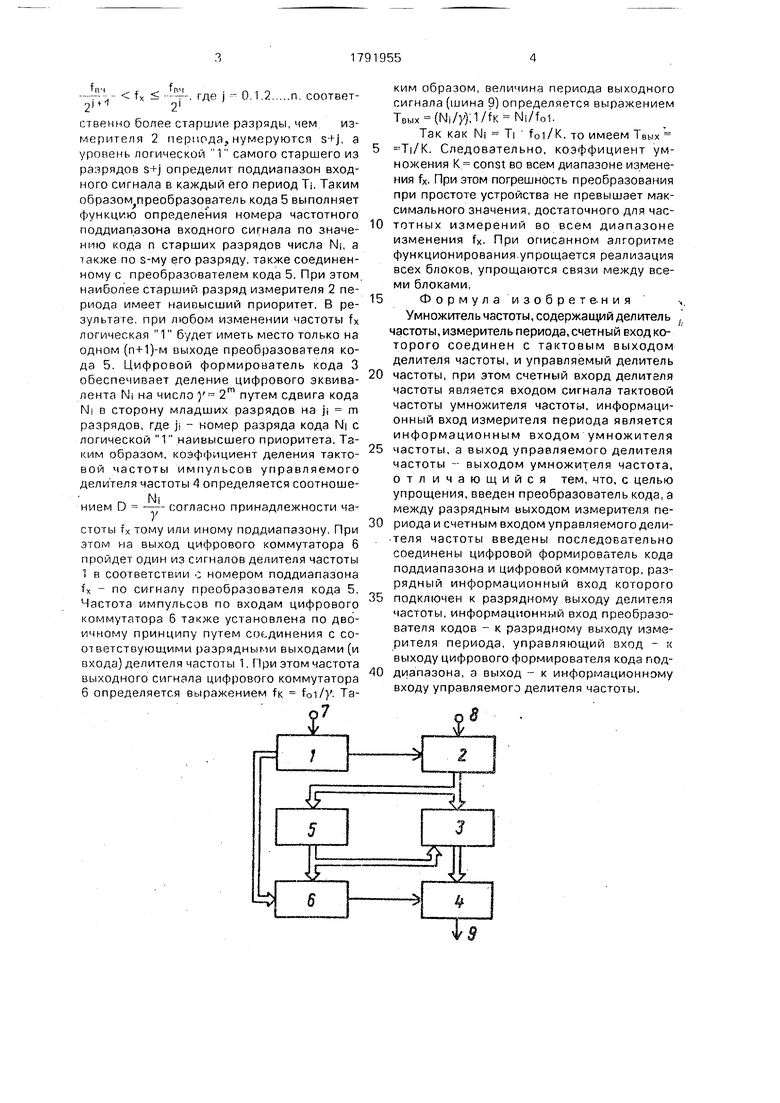

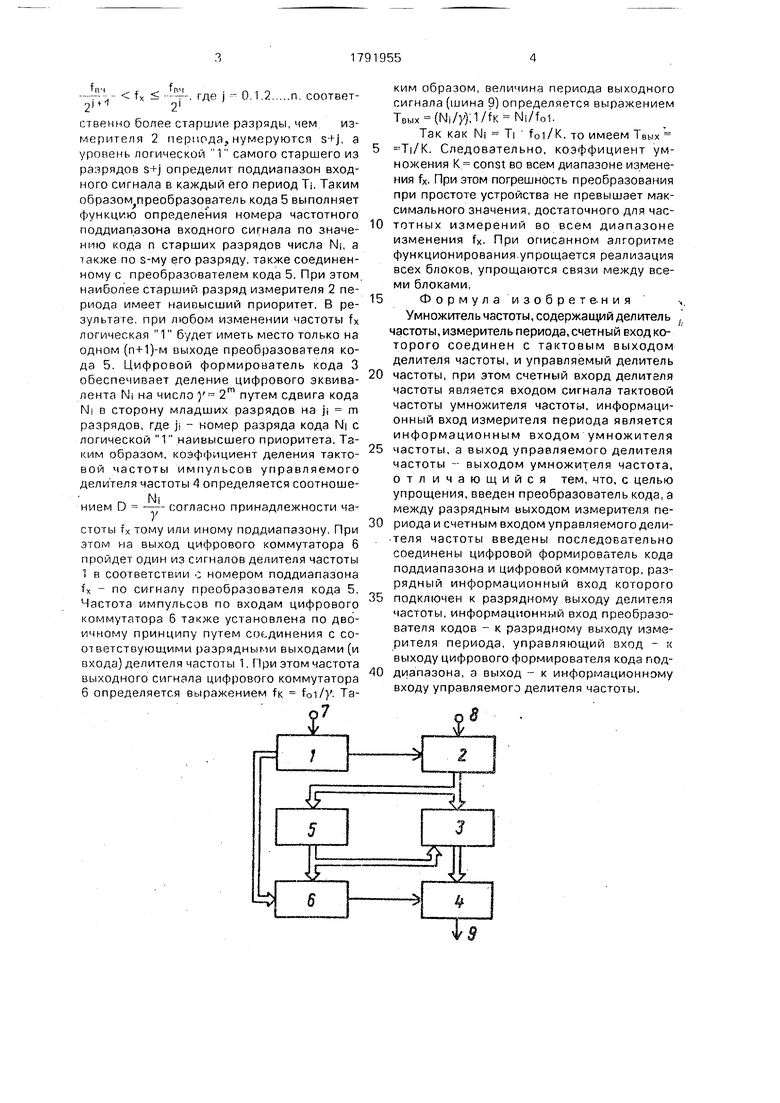

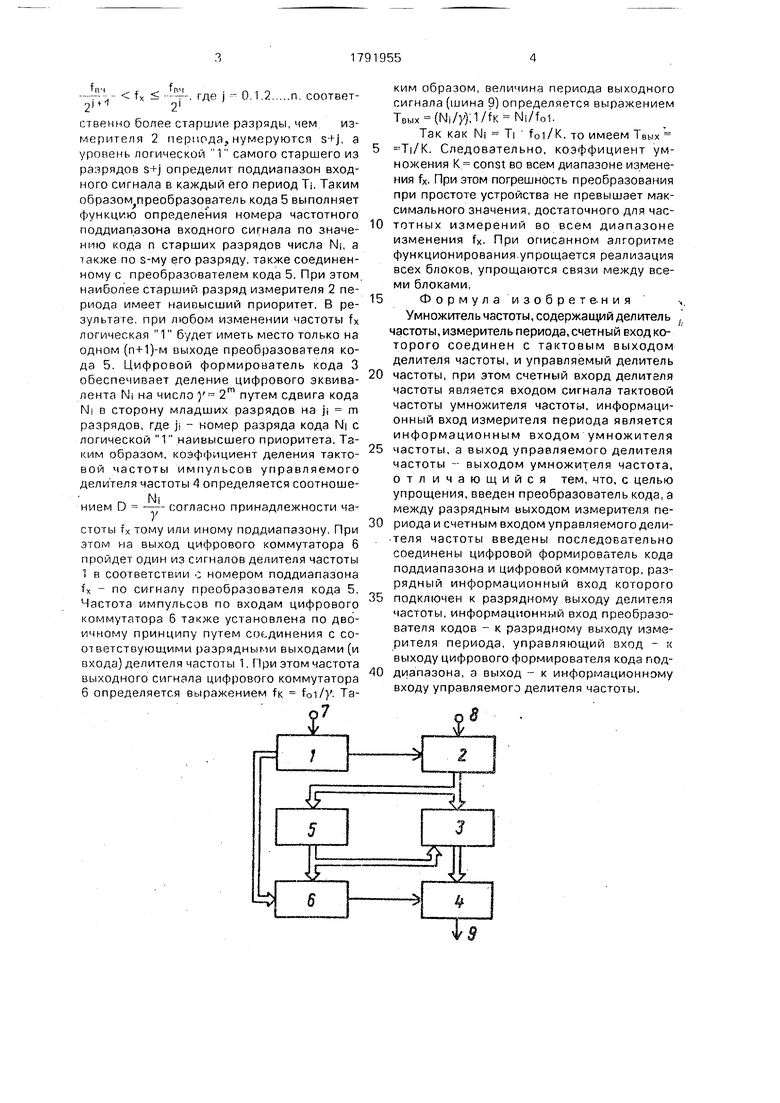

На .чертеже представлена структурная электрическая схема умножителя частоты.

Умножитель частоты содержит делитель частоты 1, измеритель 2 периода, цифровой формирователь кода 3 поддиапазона, управляемый делитель частоты 4, преобразователь кода 5, цифровой коммутатор б, счетный вход 7, информационный вход 8 и выход 9.

Умножитель частоты работает следующим образом.

Делитель частоты 1 делит частоту импульсов foi, поступающих со счетного входа делителя частоты 1, на число К, которое определяет коэффициент умножения. Измеритель 2 периода Tf входного сигнала с информационного входа 8 формирует цифровой эквивалент (,2...) этого периода путем счета импульсов f02 foi/K. Таким образом, на его выходе во время каждого

последующего периода Тц-i входного сигнала представлена информация о величине предыдущего периода Т входного сигнала в виде цифрового эквивалентам. Этот эквивалент формируется путем счёта импульсов с выхода делителя частоты 1. Число разрядов цифрового эквивалента NI определяется выражением q s+n, где s - число младших разрядов, п - число старших разрядов, соединенных с преобразователем кода 5. При

этомр 1од2 г- -р- Ь где fH4 - значение

fhlHК

частота нижней границы частотного диапазона входного сигнала умножителя частоты. Кроме того,

J

|Ю

JOT

ел

(ода

вч

foi

к

S Iog2 -

fa

foi

к

где ffi4 значение частоты верхней границы частотного диапазона входного сигнала. Таким образом, при - fx fen изменение

NJ осуществляется в s младших разрядах измерителя 2 периода, причем в- старшем s-омего разряде всегда логическая 1. При

k l. f ., где j -- 0,1,2.:..,n, соответ2м 2 / . твенно более старшие разряды, чем. измерителя 2 периода,нумеруются, s+j, a ровень логической 1 самого старшего из разрядов s+j определит поддиапазон входного сигнала в каждый его период Ti. Таким образом преобразоратель кода 5 выполняет функцию о еде Цния Домера частотного под циа/тазойа:ЪхШн:ЬУВ сигнала по значении кода, п старТиШ-разрядов числа Ni, a такЖе rio s-му его разр яду, также соединенному с преобразователем кода 5. При этом, наиболее старший разряд измерителя 2 периода имеет наивысший приоритет. В результате, при любом изменении частоты fx логическая 1 будет иметь место только на одном (п+1)-м выходе преобразователя кода 5. Цифровой формирователь кода 3 обеспечивает деление, цифрового, эквивалента NI на число у 2т путем сдвига кода N I в сторону младших разрядов на л т разрядов, где |i - номер разряда кода Ы с логической 1 наивысшего приоритета. Таким образом, коэффициент деления тактовой час тоты импульсов управляемого делителя частоты 4 определяется соотноше;NI

нием D - согласно принадлежности частоты fx тому или иному поддиапазону. При этом на выход цифрового коммутатора 6 пройдет один из сигналов делителя частоты 1 в соответствии о номером поддиапазона fx - no сигналу преобразователя кода 5. Частота импульсов по входам цифрового коммутатора 6 также установлена по дво-, йчнбму принципу путем соединения с соответствующими разрядными выходами (и входа) делителя частоты 1. При этом частота выходного сигнала цифрового коммутатора, 6 определяется выражением fK foi/y. Таким образом, величина периода выходного сигнала (шина 9) Определяется выражением TBb,x (Ni/y);1/fK Ni/fol.

Так как Ni Ti f0i/K, то имеем Твых

Т|/К. Следовательно, коэффициент умножения К - const во всем диапазоне изменения fx. При этом погрешность преобразования при простоте устройства не превышает максимального значения, достаточного для час0 тотных измерений во всем диапазоне изменения fx. При описанном алгоритме Ф9 нкй;йонирования.упрош,ается реализация всех блоков, упрощаются связи между всеми блоками.

5ф о р м у л а и з о б р е т ен и я ,

Умножитель частоты, содержащий делитель ; частоты, измеритель периода, счетный вход ко- торого соединен с тактовым выходом делителя частоты, и управляемый делитель

0 частоты, при этом счетный вхорд делителя частоты является входом сигнала тактовой частоты умножителя частоты, информационный вход измерителя периода является информационным входом умножителя

5 частоты, а выход управляемого делителя частоты - выходом умножителя частота, о т л и ч а ю щ и и с я тем, что, с целью упрощения, введен преобразователь кода, а между разрядным выходом измерителя пе0 риода и счетным входом управляемого дели- . -теля частоты введены последовательно соединены цифровой формирователь кода поддиапазона и цифровой коммутатор, разрядный информационный вход которого

5 подключен к: разрядному выходу делителя частоты, информационный вход преобразователя кодов - к разрядному выходу измерителя периода, управляющий вход - к выходу цифрового формирователя кода под0 диапазона, а выход - к информационному входу управляемого делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный умножитель частоты | 1989 |

|

SU1793538A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

Изобретение относите ; к области автоматики и вычислительной Техники. Цельно . ,;. . . /. 2 v изобретения является упрощение. Умножитель частоты содержит делитель 1 частоты, измеритель 2 периода, цифровой формирователь кода 3 поддиапазона, управляемый, делитель 4 частоты, преобразователь кода 5, цифровой коммутатор 6.-Цель изобретения достигается за счет упрощения алгоритма функционирования, упрощения реализации блоков и межблочных связей. 1 ил.

| Умножитель частоты | 1985 |

|

SU1443121A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-01-30—Публикация

1989-07-14—Подача