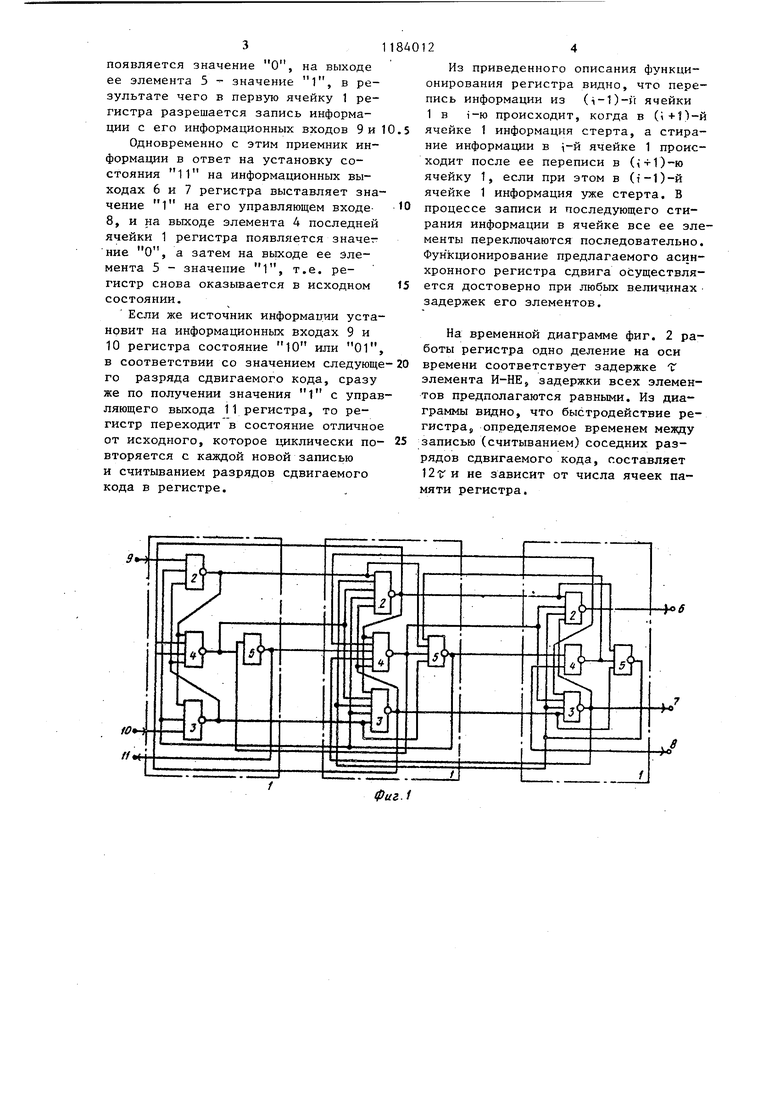

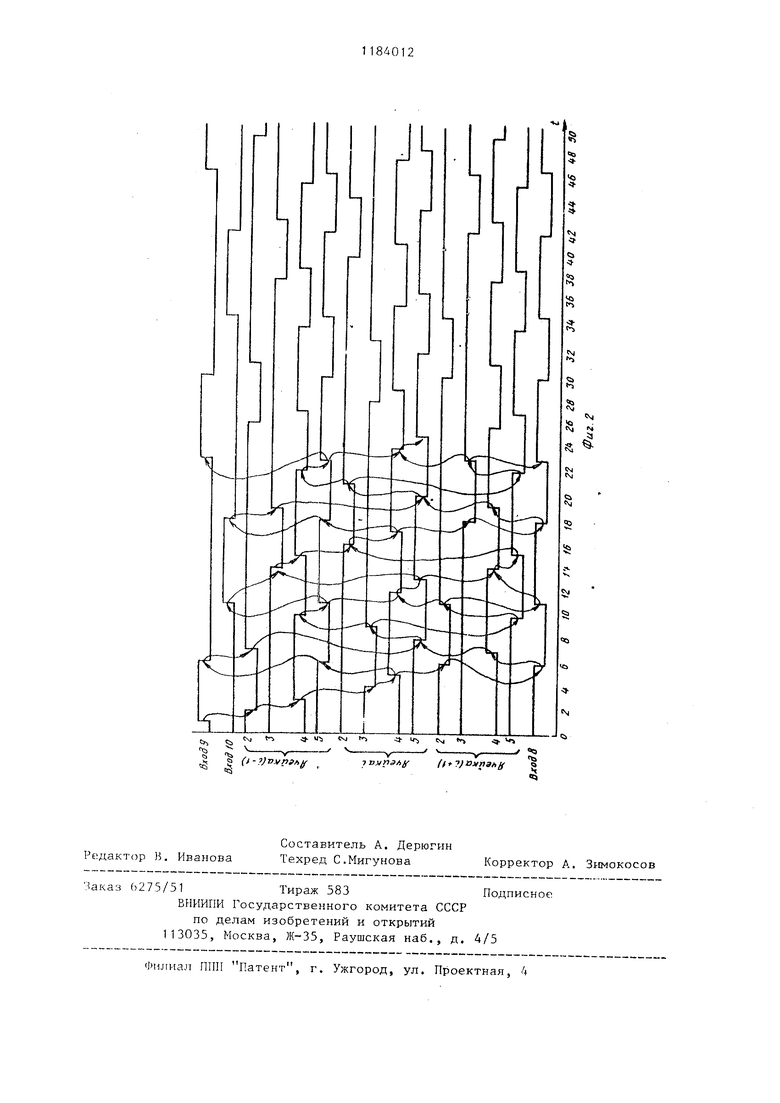

Ичобретоние относится к автомати :-:;П|;ii;TC,4btiC)U технике. , изобретения - повышение быГ1: регистра , Ф;и, при iiCLiC: ;;, схема .ц,па |;м/;;ого регистра; па фиг. 2 - време м );.MMa его iJaOoTbi. .,си1 хр1ми-1ын регистр сдгзига содер ::,; I ;nuiKu i памяти, каждая из кото :-:.i :.1месТ первый 2, второй 3, трети -I )i четиертьп 5 элементг; Ы-НЕ .() злемептоп 2 и 3 последней -;чс;;1ь; 1 г.амяти являются информационн П 1:1;.:-:олами 6 I- 7 регистра, а первы iixo/ зле-мента 4 этой ячейки - управ .| Н --:1- п. пхо.дом 8 регистра. Вторые , : I Л; :чептот 2 и 3 nopBoti ;;Ч;;Л ОТСЯ П1форМаЦИО ПП МИ ВХО .ui-iji 9 и 10 )егистра, а выход элеме управляюп им выАсилхроипый регистр сдвига рабо;:r;j cjKv; yhiHiUM образом. Пусть в исходном СОСТОЯ1П1И ИИ:ч:)рма1Д я т,о ясех я гейках 1 памяти р 1йГгра стерта.; т.е. ла выходах эле- iia;:MiUP и , а на выходах элем |ог 3 - значоитс . Это соcsoHinu- )1сгистра поддерживается тем чо :;;1ИОМ1Д- к информадии сохраняет значение 1, на управляющем входе 8 регистра в ответ на отсутствие инфорг. Fia его 1П1формационнь:х rt-i:;(:a.x 6 i 7 (состоянГ1е it этих вь ходпв) . а источник информадии не .1:и).яет информадию на инфорьпдиошчых рход.ах 9 и 10 регистра, т,е, (-охраняет состояние 00 этих MXOiiOB , Поскол.ьку на управляющем выходе i : (ра в исхо.дном Состоянии им :с.ч з1-;г чс;пи ; 1, источник информации г.О),:ет 11 ;мест ГГ1, на информадионiuic входы 9 1 10 регистра очередной рачрял, с;;г.игаемого ко,па, т.е. уста; ч :чги1, 1 ре;зул1 тате происходргг загигь инфо11х ап,ии Б первую ячейку 1 Т сргистра, nin-i ;)том на выходе одного из ;кчоме 1тоЕ 2 или 3 первой ячейки :1оя)ляется значение О, а затем ла rfbixor.o се элемеша значе;- ие Г, То.-ько после этого происходит гор ;:ись разряда сдвигаемого I i;;-:i, и Cjo;i.yi(iii;yi() ячеГку 1 регистра, Т:, .стаiH BKa isa выходе из ее элементов 2 или 3 значения О и последующая установка на выходе ее элемента 4 значения 1, Последнее приводит к тому, что на .выходе элемента 5 первой ячейки 1 регистра (на его управляющем выходе 11) появляется значение О, получив которое источник информации устанавливает на информационных входах 9 и 10 регистра состояние 00, чем вызывает стирание информации в перьой ячейке 1 регистра. В результате на выходах элементов 2 и 3 первой ячейки 1 регистра появится значение 1. Одновременно с этим очередной разряд сдвигаемого кода переписывается из второй ячейки 1 регистра в его третью (в нашем случае последнюю) ячейку 1. Этот процесс, аналогично рассмотренному выше, включает в себя установку значения О на выходе одного из элементов 2 или 3 третьей ячейки 1 и далее (поскольку эта ячейка 1 последняя) после получения приемником информации очередного разряда сдвигаемого кода с информацио} ных выходов 6 и 7 регистра и установки на управляющем входе 8 регистра значения О, появление значения 1 на выходе элемента 4 этой ячейки 1. Если к этому моменту в первой ячейке 1 информация уже стерта, то запись информации в третью ячейку 1регистра вызывает появление значения О на выходе элемента 5 второй ячейки 1 регистра и доследующее стирание 7з ней информации, т.е. установку значения 1 на выходе ее элементов 2 и 3. В результате этого на выходе элемента 4 первой ячейки 1 регистра появляется значение О, а затем на выходе ее элемента 5 значение 1, которое, поступая на управляющий выход 11 регистра, свидетельствует о готовности последнего к приему следующего разряда сдвигаемого крда. Одновременно с этим fia выходе элемента 5 третьей (последней) ячейки 1 регистра появляется значение О, а затем на выходе ее элементов 2и 3 - значение 1, т.е. в этой ячейке происходит стирание информации и на и фopмaциoнныx выходах 6 и 7 регистра устанавливается состояние 11. 1осле этого на выходе элемента 4 второГг ячейки 1 регистра i 3 появляется значение О, на выходе ее элемента 5 значение 1, в результате чего в первую ячейку 1 регистра разрешается запись информации с его информационных входов 9 и Одновременно с этим приемник информации в ответ на установку состояния 11 на информационных выходах 6 и 7 регистра выставляет зна чение 1 на его управляющем входе8, и на выходе элемента 4 последней ячейки 1 регистра появляется значег ние О, а затем на выходе ее элемента 5 - значепие 1, т.е. регистр снова оказывается в исходном состоянии. Если же источник информации уста новит на информационных входах 9 и 10 регистра состояние 10 или 01 в соответствии со значением следующ го разряда сдвигаемого кода, сразу же по получении значения 1 с упра ляющего выхода i1 регистра, то регистр переходит в состояние отлично от исходного, которое циклически по вторяется с каждой новой записью и считыванием разрядов сдвигаемого кода в регистре. 24 Из приведенного описания функционирования регистра видно, что перепись информации из (i-1)-i ячейки 1 в i-ю происходит, когда в (1+1)-й ячейке 1 информация стерта, а стирание информахдаи в i-й ячейке 1 происходит после ее переписи в {1т1)-ю ячейку 1, если при этом в (1-1)-й ячейке 1 информация уже стерта. В процессе записи и последующего стирания информации в ячейке все ее элементы переключаются последовательно. Функционирование предлагаемого асинхронного регистра сдвига осуществляется достоверно при любых величинах задержек его элементов. На временной диаграмме фиг. 2 работы регистра одно деление на оси времени соответствует задержке Т элемента И-НЕ, задержки всех элементов предполагаются равными. Из диаграммы видно, что быстродействие регистра, определяемое временем между записью (считыванием) соседних разрядов сдвигаемого кода, составляет IZf и не зависит от числа ячеек памяти регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1990 |

|

SU1805501A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1259337A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

АСИНХРОННЫЙ РЕГИСТР СДВИГА, содержащий ячейки памяти, каждая из которых состоит из четырех элементов И-НЕ, причем выходы первого и второго элементов И-НЕ каждой ячейки памяти соединены перекрестными связями с первыми входами данных элементов а выход третьего элемента И-НЕ - с первым входом четвертого элемента И-НЕ, выходы первого и второго элементов И-НЕ каждой ячейки памяти, кроме последней, соединены с первым и вторым входами третьего элемента И-НЕ данной ячейки памяти и с вторыми входами первого и второго элементов И-НЕ последующей ячейки памяти, а выход четвертого элемента И-НЕ - с третьим входом третьего элемента И-НЕ последующей ячейки памяти, отличающийся тем, что, с целью повышения быстродействия регистра, выходы первого и второго элементов И-ПЕ каждой ячейки памяти, кроме первой и последней, соединены с вторым и третьим входами четвертого элемента И-НЕ последующей ячейки памяти и с четвертым и пятым входами третьего элемента И-НЕ предыдущей - ,-..,, I ячейки памяти, выход третьего элемента И-НЕ данной ячейки соединен с третьими входами первого и второго элементов И-НЕ последующей ячейки памяти и с четвертым входом четвертого элемента И-НЕ предьщущей ячейки памяти, выход четвертого элемента И-НЕ соединен с четвертыми входами первого и второго элементов И-НЕ данной ячейки памяти и с пятыми входами первого и второго элементов И-НЕ предыдущей ячейки памяти, вторые входы первого и второго элементов И-НЕ первой ячейки памяти являются информационными входами регистра, а выходы этих элементов соединены с вторым и третьим (Л входами четвертого элемента И-НЕ второй ячейки памяти, выход третьего элемента И-НЕ первой ячейки памяти соединен с третьими входами первого и второго элементов И-НЕ второй ячейки, а выход четвертого элемента И-НЕ первой ячейки памяти является управляющим выходом регистра, выходы первого 00 и второго элементов И-НЕ последней 4 ячейки памяти соединены с четвертым и пятым входами третьего элемента И-НЕ предпоследней ячейки и являю ются информационными выходами регистра, выход третьего элемента И-НЕ , следней ячейки памяти соединен с третьими входами первого и второго элементов И-НЕ предпоследней ячейки памяти, ,а второй вход этого элемента является управляющим входом регистра, выход четвертого элемента И-НЕ последней ячейки памяти соединен с четвертыми входамипервого ивторого элементов И-НЕданной ячейкипамяти ис пя, тыми входами первого ивторого элемен-г тов И-НЕпредпоследней ячейкипамяти.

| ВСЕСОЮЗНАЯ | 0 |

|

SU374663A1 |

| G, 11 с 19/00, 1973 | |||

| Асинхронный регистр сдвига | 1978 |

|

SU728161A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-07—Публикация

1984-03-14—Подача