Изобретение относится к импульсной и вычислительной технике и может быть использовано в различных устройствах обработки и передачи информации.

Цель изобретения - упрощение схемы устройства.

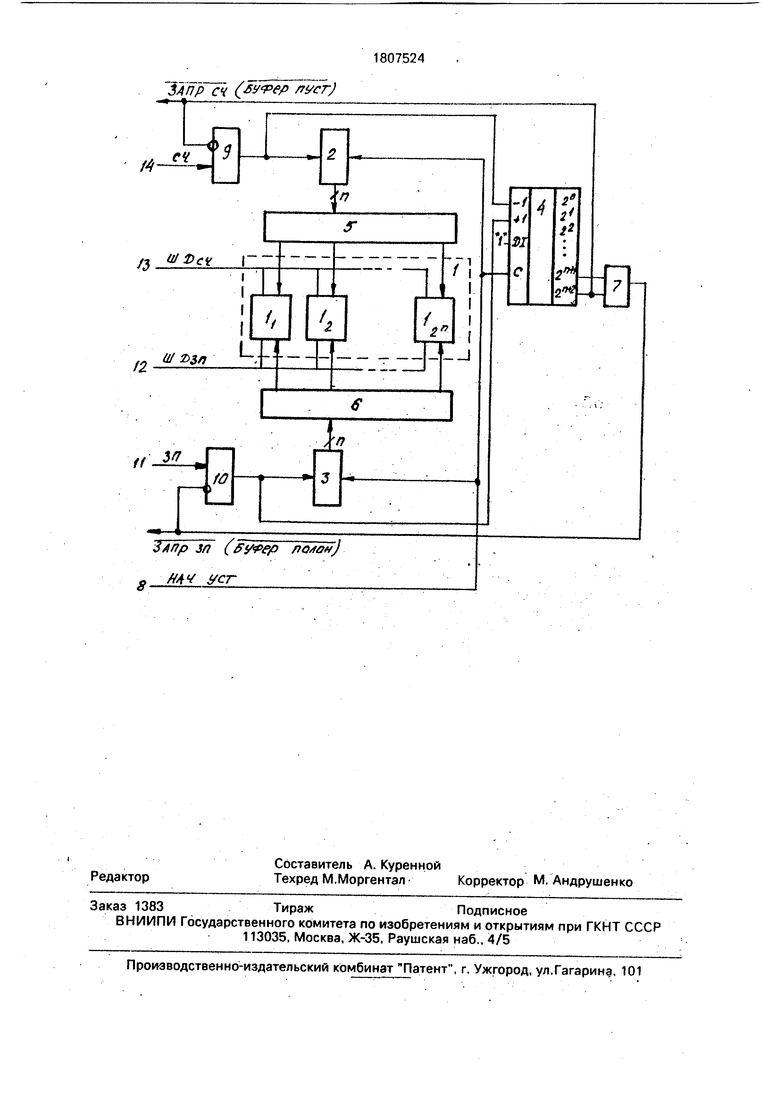

На чертеже приведена функциональная схема устройства.

Буферное запоминающее устройство содержит: 1 - блок накопителя, 2 - счетчик адреса считывания, 3 - счетчик адреса записи, 4 - реверсивный счетчик, 5, 6 - дешифраторы адресов считывания и записи, 7 - элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, 8 - шина установки, 9, 10 - элементы И, 11 - шина управления записью, 12 - шина данных записи, 13 - шина данных считывания, 14 - шина управлением считыванием.

Буферное запоминающее устройство работает следующим образом.

Перед началом работы по шине 8 поступает импульс установки, обнуляющий счетчики 2 и 3 и устанавливающий счетчик 4 в состояние, при котором на всех выходах устанавливается 1(по входу записи параллельного кода предустановки). Разрядность счетчика 4 берется на 2 больше, чем разрядная сетка накопителя для управления работой устройства. При этом при начальной установке старшие разряды счетчика, объединенные через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формируют разрешающий сигнала на запись, а старший разряд запрещает считывание (буфер пуст). При приходе импульса записи счетчик 4 устанавливается в нулевое состояние, при котором разрешается считывание (и запись), если следующим импульсом будет считывание, то после него счетчик 4 установится в состояние, при котором считывание будет запрещено старшим разря

дом, а запись разрешена. Рассмотрим ситуацию, при которой все разряды счетчика 4, кроме старших, установлены в 1. Если придет импульс записи, то счетчик 4 перейдет в состояние, когда 2n+1 - разряд установится в 1, и запретит запись (буфер полон). В остальном функционирование аналогично прототипу.

Таким образом, при сохранении функционирования устройства схемная реализация проще, чем в прототипе,

Формула изобретения Буферное запоминающее устройство, содержащее блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса записи, счетчик адреса считывания, счетчик управления, первый и второй элементы И, причем входы установки счетчиков адреса записи и считывания и счетчика управления объединены и являются входом установки устройства, вход прямого счета счетчика управления и счетный вход счетчика адреса записи объединены и подключены к выходу первого элемента И, первый вход которого является входом записи устройства, второй вход первого элемента И является входом запрета записи устройства,

входом запрета считывания которого является первый вход второго элемента И, второй вход которого является входом считывания устройства, выход второго элемента И соединен со счетным входом счетчика адреса считывания, выходы которого соединены с соответствующими входами дешифратора считывания, выходы которого соединены с адресными входами считывания

блока памяти, выходы которого являются информационными выходами устройства, информационными входами которого являются информационные входы блока памяти, адресные входы записи которого соединены с

выходами дешифратора записи, входы которого, соединены с выходами счетчика адреса записи, отличающееся тем, что, с целью упрощения устройства, в него введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом первого элемента И, предпоследний выход счетчика управления соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого и первый вход второго элемента И

объединены и подключены к последнему выходу счетчика управления, вход обратного счета которого соединен с выходом второго элемента И.

(Јyvep wcr)

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Буферное запоминающее устройство | 1991 |

|

SU1807523A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для выборки адресовиз блОКОВ пАМяТи | 1974 |

|

SU813504A1 |

| Устройство для отладки программ | 1985 |

|

SU1280637A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в различных устройствах обработки и передачи информации. Цель изобретения - упрощение устройства. Устройство предназначено для буферного запоминания входной информации и выдачи на устройствах обработки (накопления) при согласовании скоростей работы входных и выходных устройств. Устройство содержит блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса записи, счетчик адреса считывания, счетчик управления разрешением записи-считывания, первый и второй элементы И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, соответствующие связи. За счет реверсивного счетчика управления и изменения кода установки удалось исключить два блока совпадения, что упростило схему устройства. 1 ил.

-ЈЈ.

11

/3

ff « Н

Л

Злпр зп ( поло) W/ усг

-/

4f

3)1

/I

| Буферное запоминающее устройство | 1988 |

|

SU1550585A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1547031A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-04-07—Публикация

1991-01-18—Подача