1

Изобретение относится к цифровой ычислительной технике и может быть спользовано при отладке программ ВМ, в состав которых входят штатные локи постоянной памяти с рабочими рограммами,

Цель изобретения - сокращение ппаратурных затрат.

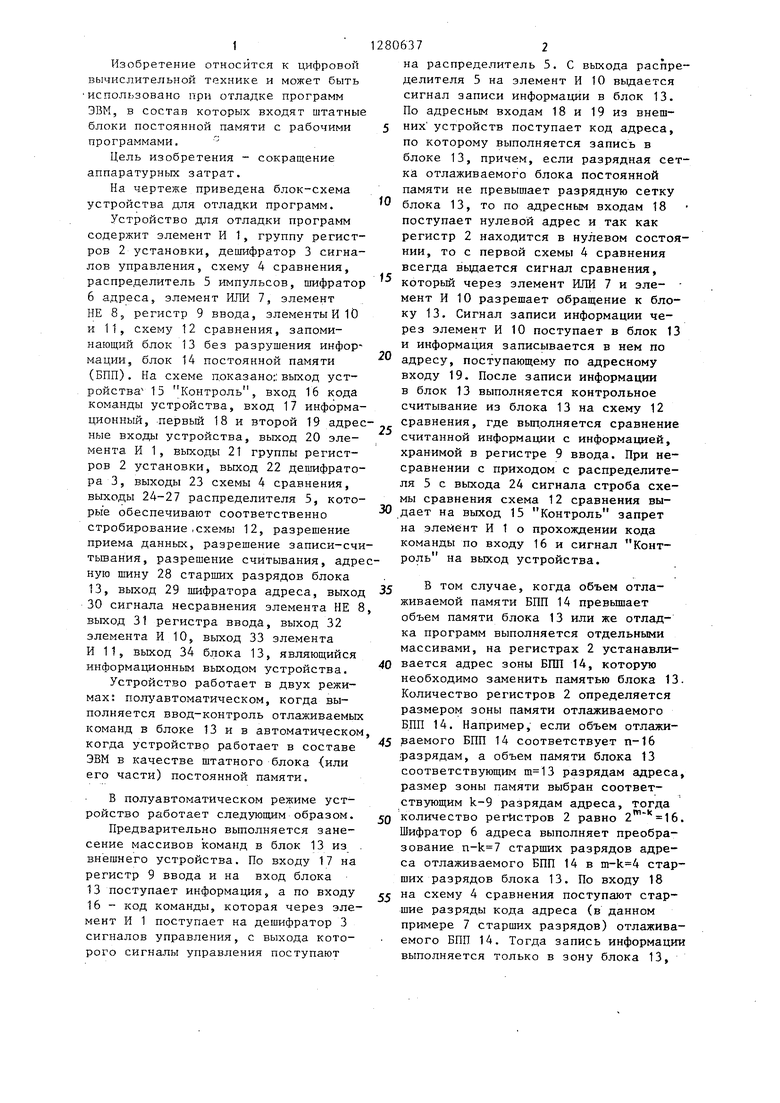

На чертеже приведена блок-схема стройства для отладки программ.

Устройство для отладки программ одержит элемент И 1, группу регистов 2 установки, дешифратор 3 сигнаов управления, схему 4 сравнения, аспределитель 5 импульсов, шифратор 6 адреса, элемент ИЛИ 7, элемент НЕ 8, регистр 9 ввода, элементы И 10 и 11, схему 12 сравнения, запоминающий блок 13 без разрушения информации, блок 14 постоянной памяти (БПП). На схеме доказано:; выход устройства 15 Контроль, вход 16 кода

команды устройства, вход 17 информационный, .первый 18 и второй 19 адресные входы устройства, выход 20 элемента И 1, выходы 21 группы регистров 2 установки, выход 22 дешифратора 3, выходы 23 схемы 4 сравнения, выходы 24-27 распределителя 5, которые обеспечивают соответственно стробирование.схемы 12, разрешение приема данных, разрешение записи-счи- тьшания, разрешение считывания, адресную шину 28 старших разрядов блока 13, выход 29 шифратора адреса, выход 30 сигнала несравнения элемента НЕ 8, выход 31 регистра ввода, выход 32 элемента И 10, выход 33 элемента И 11, выход 34 блока 13, являющийся информационным выходом устройства.

Устройство работает в двух режимах: полуавтоматическом, когда выполняется ввод-контроль отлаживаемых команд в блоке 13 и в автоматическом, когда устройство работает в составе ЭВМ в качестве штатного блока -(или его части) постоянной памяти.

В полуавтоматическом режиме устройство работает следующим образом.

Предварительно выполняется занесение массивов команд в блок 13 из . внешнего устройства. По входу 17 на регистр 9 ввода и на вход блока 13 поступает информация, а по входу 16 - код команды, которая через элемент И 1 поступает на дешифратор 3 сигналов управления, с выхода которого сигналы управления поступают

12

15

2806372

на распределитель 5. С выхода распределителя 5 на элемент И 10 выдается сигнал записи информации в блок 13. По адресным входам 18 и 19 из внеш5 них устройств поступает код адреса, по которому выполняется запись в блоке 13, причем, если разрядная сетка отлаживаемого блока постоянной памяти не превышает разрядную сетку

О блока 13, то по адресным входам 18 поступает нулевой адрес и так как регистр 2 находится в нулевом состоянии, то с первой схемы 4 сравнения всегда выдается сигнал сравнения, который через элемент ИЛИ 7 и эле- - мент И 10 разрешает обращение к блоку 13. Сигнал записи информации через элемент И 10 поступает в блок 13 и информация записывается в нем по адресу, поступающему по адресному входу 19. После записи информации в блок 13 выполняется контрольное считывание из блока 13 на схему 12 сравнения, где вып.олняется сравнение считанной информации с информацией, хранимой в регистре 9 ввода. При несравнении с приходом с распределителя 5 с выхода 24 сигнала строба схемы сравнения схема 12 сравнения вы30 дает на выход 15 Контроль запрет на элемент И 1 о прохождении кода команды по входу 16 и сигнал Контроль на выход устройства.

20

25

В том случае, когда объем отлаиваемой памяти БПП 14 превьппает объем памяти блока 13 или же отладка программ выполняется отдельными массивами, на регистрах 2 устанавливается адрес зоны БПП 14, которую необходимо заменить памятью блока 13. Количество регистров 2 определяется размером зоны памяти отлаживаемого БПП 14. Например, если объем отлажираемого БПП 14 соответствует п-1б азрядам, а объем памяти блока 13 соответствующим разрядам адреса, размер зоны памяти выбран соответствующим k-9 разрядам адреса, тогда

количество регистров 2 равно 2 16. Шифратор 6 адреса выполняет преобразование старших разрядов адреса отлаживаемого БПП 14 в старших разрядов блока 13. По входу 18 на схему 4 сравнения поступают старшие разряды кода адреса (в данном примере 7 старших разрядов) отлаживаемого БПП 14. Тогда запись информации выполняется только в зону блока 13,

определяемую регистрами 2 и шифратором 6 адреса.

В автоматическом режиме устройство отладки работает в комплексе с ЭВМ в качестве штатного БПП или его части.

Адреса заменяемых зон БПП 14 памятью блока 13 устанавливаются на регистрах 2. Старпгае разряды адреса по адресному входу 18 поступают на схему 4 сравнения, где сравниваются с кодом адреса, установленным на регистрах 2. Младшие разряды кода адреса по адресному входу 19 поступают непосредственно на БПП 14 и блок 13. По входу 16 из ЭВМ через элемент И 1 дешифратор 3 сигналов управления выдается команда считьгоания информации, по которой из распределителя 5 на элементы И 10 и 11 выдаются сигналы считывания информации. Если на одной из схем 4 сравнения есть сигнал сравнения, то он через элемент ИЛИ 7 выдается на элемент И 10, и р блок 13 вьщается сигнал считывания информации, которая по выходу 34 поступает на выход устройства. Если нет сигнала сравнения ни на одной из схем сравнения, то сигнал считывания с распределителя 5 поступает через элемент И 11 30 равенства первой схемы сравнения соена БПП 14, и информация считывается из отлаживаемого БПП 14 и через выход 34 вьщается на выход устройства.

Формула изобретения

Устройство для отладки программ, содержащее распределитель импульсов, три элемента И, группу регистров установки, дешифратор сигналов управления, первую схему сравнения, элемент ИЛИ, элемент НЕ, запоминающий блок без разрушения информации и бло постоянной памяти, причем вход кода команды устройства соединен с первым входом первого элемента И, выход которого соединен с информационным входом дешифратора сигналов управления, выход которого соединен с входо sanyclca распределителя импульсов, первый и второй выходы которого соединены с первыми входами второго и третьего элементов И соответственно.

ВНИИПИ Заказ 7068/55 Тираж 671 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

0

выходы второго и третьего элементов И соединены соответственно с входом записи запоминающего блока без разрушения информации и с входом считывания блока постоянной памяти, выходы регистров установки группы соединены с первым входом первой схемы сравнения, первый адресный вход устройства соединен с вторым входом первой схемы сравнения и с адресными входами старших разрядов блока постоянной памяти, выходы равенства схемы сравнения ; соединены с соответствующими входами элемента ИЛИ, выход которого соединён с вторым входом второго элемента И и через элемент НЕ - с вторым входом, третьего элемента И, информа- ционный вход устройства соединен с

информационным входом запоминающего 0 блока без разрушения информации, второй адресный вход устройства соединен с адресными входами младших разрядов адреса блока постоянной памяти и запоминающего блока без разрушения информации, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены шифратор адреса, регистр ввода,, вторая схема сравнения, причем выходы

5

5

0

0

динены с соответствующими входами шифратора адреса, выходы которого соединены с адресными входами старших разрядов запоминающего блока без раз- 5 рушения информации, третий и четвертый выходы распределителя импульсов соединены соответственно с входом стробирования второй схемы сравнения и входом записи регистра ввода, ни-.,i формационный вход устройства соединен с информационным входом регистра ввода, выход которого соединен с первым информационным входом второй схемы сравнения, информационные выходы блока постоянной памяти и запоминающего устройства без разрушения информации соединены с вторым информационным входом второй схемы сравнения и являются информационным выходом устройства, выход неравенства второй схемы сравнения соединен с вторым входом первого элемента И и является выходом контроля устройства.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программ | 1988 |

|

SU1511750A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

Изобретение относится к области :цифровой вычислительной техники и может быть использовано при отладке программ ЭВМ, в состав которых входят штатные блоки постоянной памяти с рабочими программами. Цель изобретения - сокращение аппаратурных затрат. Устройство для отладки программ содержит элемент И 1, группу регистров 2 установки, дешифратор 3 сигналов управления, схему 4 сравнения, распределитель 5.импульсов, шифратор 6 адреса, элемент ИЛИ 7, элемент НЕ 8, регистр 9 ввода, элементы И 10 и 11, схему 12 сравнения, запоминающий блок 13 без разрушения информации, блок 14 постоянной памяти. Данное устройство обеспечивает эффективную отладку программ за счет подмены участка памяти блока постоянной памяти зоной памяти блока без разруше- д ния информации. 1 ил. (Л

| Устройство для управления обращением к памяти при отладке программ | 1981 |

|

SU1001099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления памятью | 1979 |

|

SU943726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-03-27—Подача