Известны устройства преобразования двоичного кода в десятичный, содержащие комбинационные сумматоры для преобразования двоичного кода числа в двоично-десятичный и дешифраторы преобразования двоично-десятичного кода в десятичный.

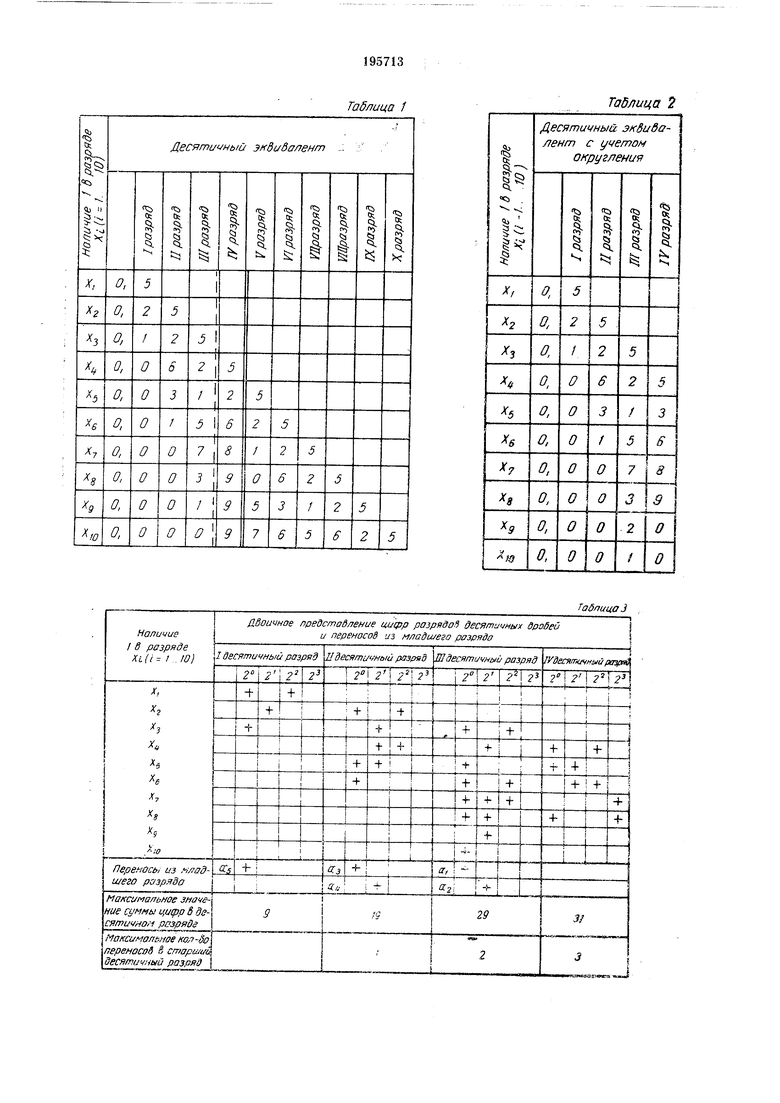

Предложенное устройство отличается тек, что для увеличения быстродействия и упрощения в нем входы сумматоров первой ступени, число которых на единицу больше числа десятичных разрядов, соединены с ходовыми шинами двоичного числа так, что входы сумматоров нулевого порядка связаны с кодовыми шинами первых (младших) двоичных разрядов каждой тетрады двоично-десятичного представления десятичных эквивалентов единиц в разрядах двоичного числа и с шикой переноса единицы младшего разряда предыдущей тетрады, входы сумматоров первого порядка связаны с кодовыми шинами вторых двоичных разрядов каждой тетрады и в случае наличия переноса соединены с шиной переноса двоичной единицы второго разряда предыдущей тетрады и т. д.; входы сумматоров второй ступени связаны с выходами сумматоров первой ступени, и соответственно входы сумматоров третьей ступени - с выходами сумматоров второй ступени; входы схемы определения переносов между десятичными разрядами соединены с выходами старЩ1 Х разрядов сумматоров первой ступени, со всеми выходами сумматоров второй ступени, со всеми выходами су:аматороз третьей ступени в четвертом дополнительном десятичном разряде и с кодовыми шинами преобразуемого двоичного числа с четвертой по лесягую включительно.

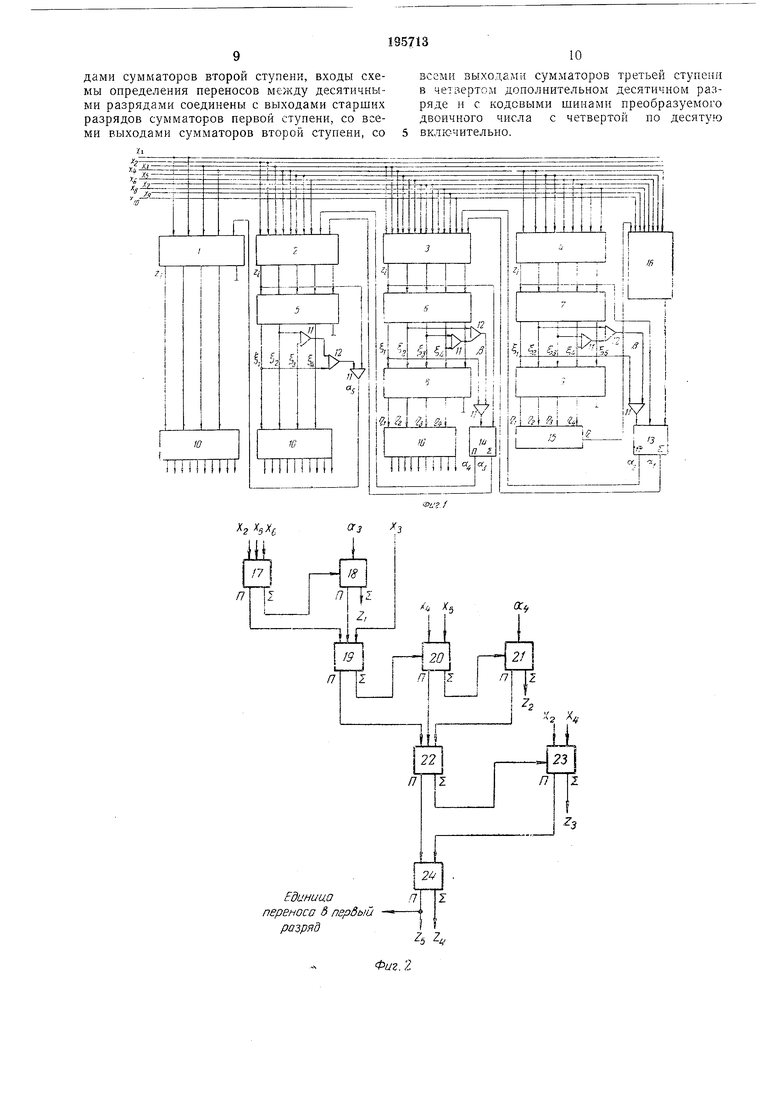

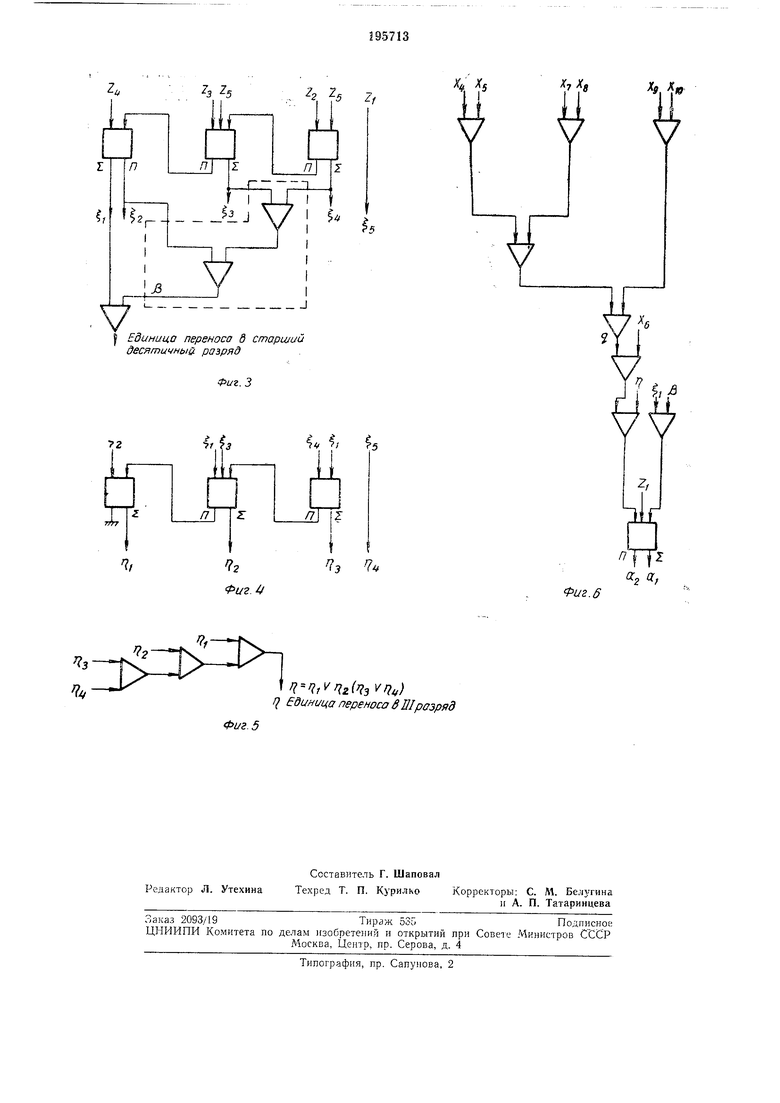

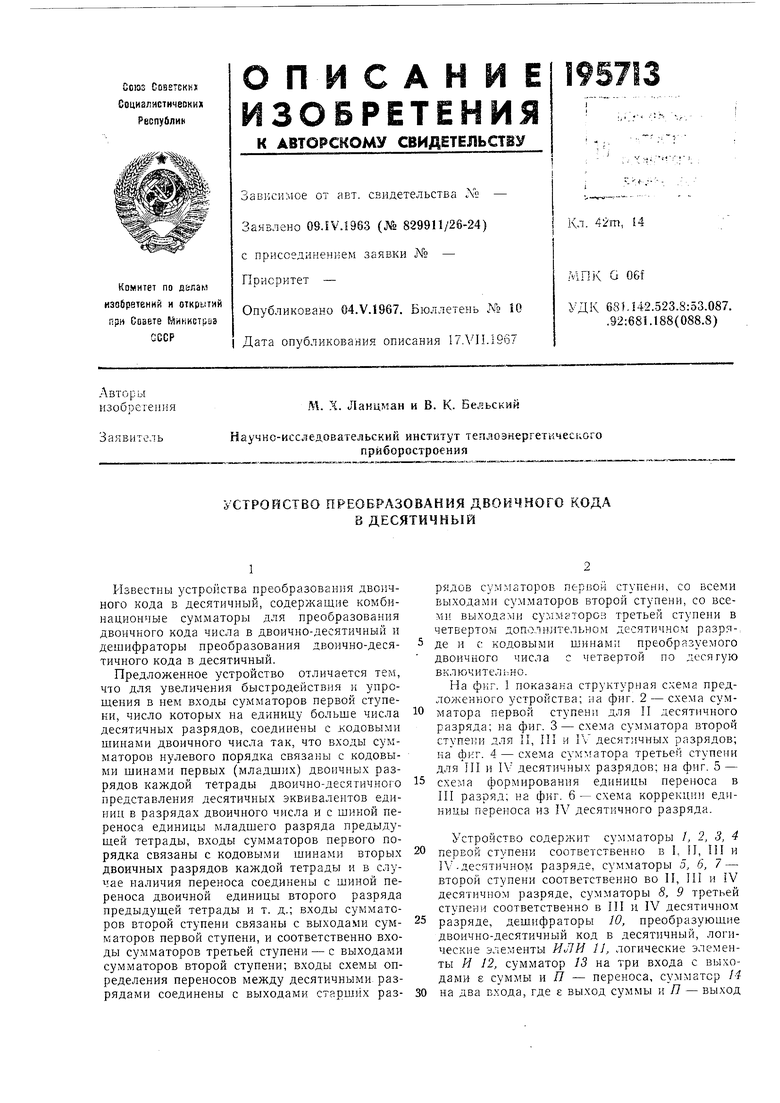

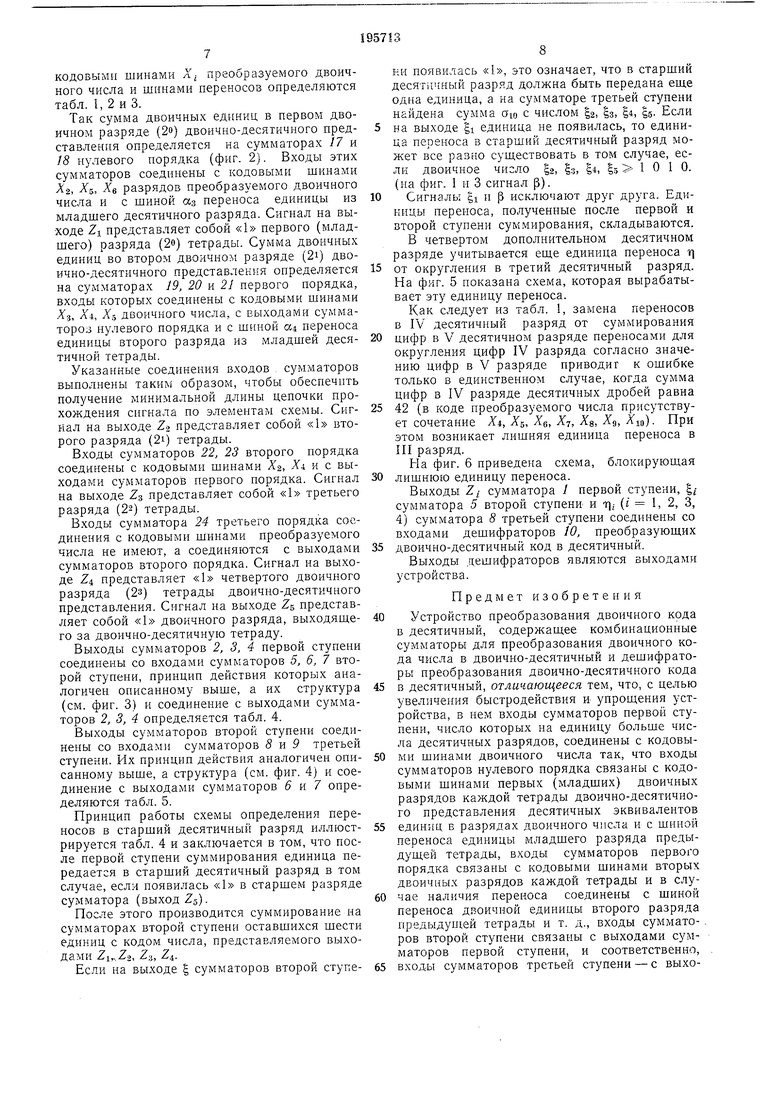

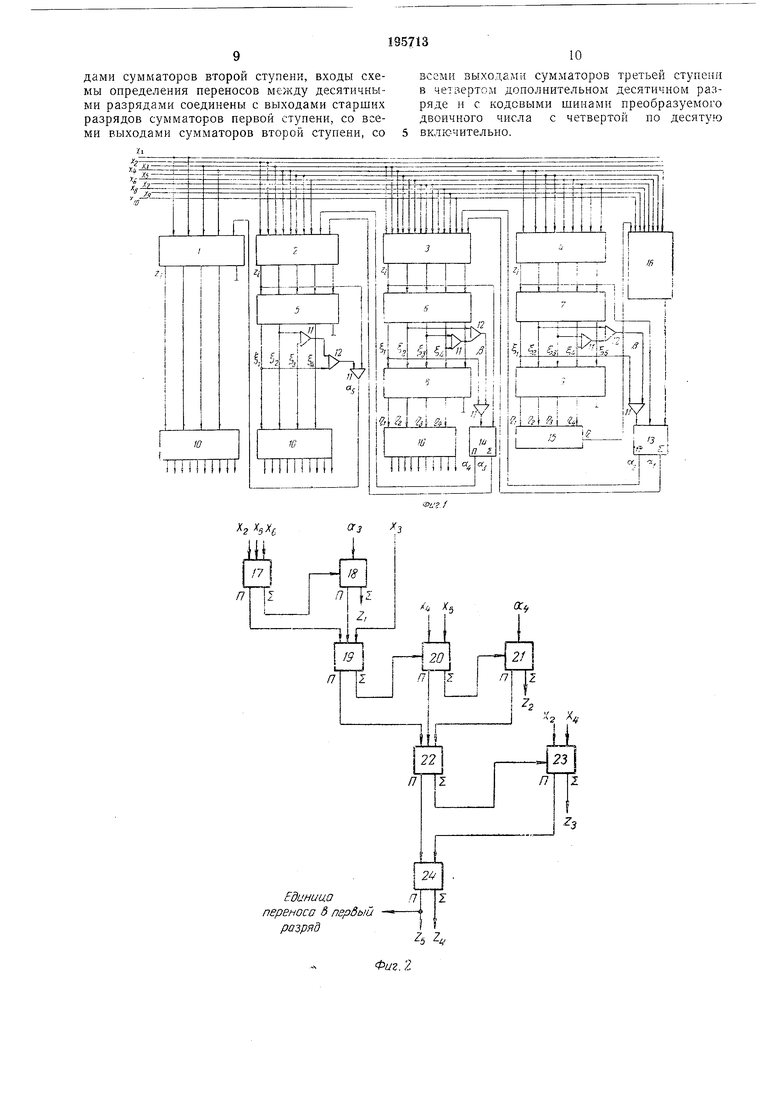

На фиг. 1 показана структурная схема предложенного устройства; на фиг. 2 - схема сумматора первой ступени для II десятичного разряда; на фиг. 3 - схема сумматора второй ступени для II, III и IV десятичных разрядов; на фиг. 4 - схема сумматора третьей ступени для ill и IV десятичных разрядов; на фиг. 5 - схема формирования единицы переноса в III разряд; на фиг. 6 - схема коррекции единицы переноса из IV десятичного разряда.

Устройство содержит сумматоры /, 2, 3, 4 первой ступени соответственно в L II, III и IV-десятичном разряде, сумматоры 5, 6, 7 - второй ступени соответственно во II, III и IV десятичном разряде, сумматоры 8, 9 третьей ступени соответственно в III и IV десятичном

разряде, дешифраторы 10, преобразующие двоично-десятичный код в десятичный, логические элементы ИЛИ 11, логические элементы И 12, сумматор 13 на три входа с выходами 8 суммы и я - переноса, сумматор 14

ТобпииаЗ

переноса, схему 15, определяющую наличие на выходах сумматора третьей ступени четвертого десятичного разряда кода числа, большего или равного пяти, схему 16, блокирующую

единицу переноса из четвертого в третий десятичный разряд, если в разрядах Л; преобразуемой двоичной дроби присутствует сочетание Xj, Х;„ Хц, Х-;, XK, XiQ.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1973 |

|

SU517890A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Двухдекадный двоично-десятичный цифроаналоговый преобразователь | 1987 |

|

SU1571764A1 |

Входы сумматоров 1-4 первой ступени соединены с кодовыми шинами -Yj, Х.. . ю преобразуемого двоичного кода и с выходами схемы, определяющей переносы из младщих десятичных разрядов в старшие десятичные разряды.

ТаВлица 5

ла единиц в каждом двоичном разряде двоично-десятнчного представления десятичных экЕивалентов единиц в разрядах преобразуемого двоичного числа.

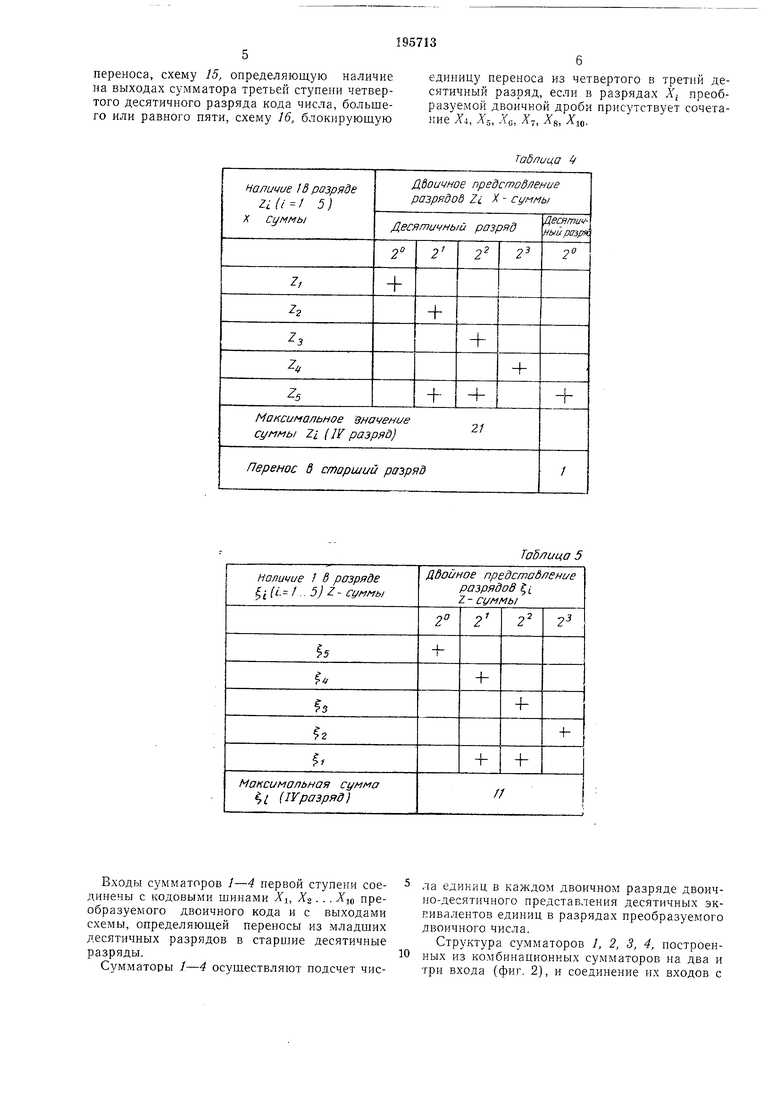

Структура сумматоров 1, 2, 3, 4, построенных из комбинационных сумматоров на два и три входа (фиг. 2), и соединение их входов с кодовыми шинами л; преобразуемого двоичного числа и шинами переносов определяются табл. 1, 2 и 3. Так сумма двоичных единиц в первом двоичиом разряде (2о) двоично-десятичного представления определяется на сумматорах 17 и 18 иулевого порядка (фиг. 2). Входы этих сумматоров соединены с кодовыми шинами z, 5, 6 разрядов преобразуемого двоичного числа и с шиной «з переноса единицы из младшего десятичного разряда. Сигнал на выходе Zi представляет собой «1 первого (младшего) разряда (2) тетрады. Сумма двоичиых единиц во втором двоичном разряде (2i) двоично-десятичного представления определяется на сумматорах 19, 20 и 2} первого порядка, входы которых соединены с кодовыми шинами .3, Л4, As двоичного числа, с выходами сумматороз нулевого порядка и с шиной а. переноса единицы второго разряда из младшей десятичиой тетрады. Указаиные соединения входов . сумматоров выполнены таким образом, чтобы обеспечить получение минимальной длины цепочки прохождения сигнала по элементам схемы. Сигнал на выходе Z представляет собой «1 второго разряда (21) тетрады. Входы сумматоров 22, 23 второго порядка соединены с кодовыми шинами Х, Xi и с выходами сумматоров первого порядка. Сигнал на выходе Zy представляет собой «1 третьего разряда (22) тетрады. Входы сумматора 24 третьего порядка соединения с кодовыми шинами преобразуемого числа не имеют, а соединяются с выходами сумматоров второго порядка. Сигнал на выходе Z4 представляет «1 четвертого двоичного разряда (2з) тетрады двоично-десятичиого представления. Сигнал на выходе Zs представляет собой «1 двоичного разряда, выходящего за двоичио-десятичную тетраду. Выходы сумматоров 2, 3, 4 первой ступени соединены со входами сумматоров 5, 6, 7 второй ступени, принцип действия которых аналогичен описанному выше, а их структура (см. фиг. 3) и соединение с выходами сумматоров 2, 3, 4 определяется табл. 4. Выходы сумматоров второй ступени соединеиы со входами сумматоров 5 и 9 третьей ступени. Их принцип действия аиалогичеи описанному выше, а структура (см. фиг. 4) и соединение с выходами сумматоров 5 и 7 определяются табл. 5. Принцип работы схемы определения переносов в старший десятичный разряд иллюстрируется табл. 4 и заключается в том, что после первой ступени суммирования единица передается в старший десятичный разряд в том случае, если появилась «1 в старшем разряде сумматора (выход Zs). После этого производится суммирование иа сумматорах второй ступени оставшихся шести единиц с кодом числа, представляемого выходами , Zs, Z4. ни появилась «I, это означает, что в старший десятичный разряд должна быть передана еще одна единица, а на сумматоре третьей ступени найдена сумма Ою с числом ga, §.з, I, ss- Если на выходе |i единица не появилась, то единица переноса в старший десятичный разряд может все разно существовать в том случае, если двоичное число ga, |з, li, 5з 1 О 1 0. (на фиг. 1 и 3 сигнал р). Сигналы li и р исключают друг друга. Единицы переноса, полученные после первой и второй ступени суммирования, складываются. В четвертом дополнительном десятичном разряде учитывается еще единица переноса г от округления в третий десятичный разряд. На фиг. 5 иоказана схема, которая вырабатывает эту единицу переноса. Как следует из табл. 1, замена переносов в IV десятичный разряд от суммирования цифр в V десятичном разряде переносами для округления цифр IV разряда согласно значению цифр в V разряде приводит к ошибке только в единствеииом случае, когда сумма цифр в IV разряде десятичных дробей равна 42 (в коде преобразуемого числа присутствует сочетание Хц, Х, Х, XT, Хд, Х, Xj). При этом возникает лишняя единица переноса в III разряд. На фиг. 6 приведена схема, блокирующая лишнюю единицу переноса. Выходы Zi сумматора / первой ступени, g сумматора 5 второй ступени и т); (г 1, 2, 3, 4) сумматора 8 третьей ступени соединены со входами дешифраторов W, преобразующих двоично-десятичный код в десятичный. Выходы дешифраторов являются выходами устройства. Предмет изобретения Устройство преобразования двоичного кода в десятичный, содержащее комбинационные сумматоры для преобразования двоичного кода числа в двоично-десятичный и дешифраторы преобразования двоично-десятичного кода в десятичный, отличающееся тем, что, с целью увеличения быстродействия и упрощения устройства, в нем входы сумматоров первой ступени, число которых на единицу больше числа десятичиых разрядов, соединены с кодовыми шинами двоичного числа так, что входы сумматоров нулевого порядка связаны с кодовыми шинами первых (младших) двоичных разрядов каждой тетрады двоично-десятичиого представления десятичных эквивалентов единиц в разрядах двоичного числа и с шииой переноса единицы младшего разряда предыдущей тетрады, входы сумматоров первого порядка связаны с кодовыми шинами вторых двоичных разрядов каждой тетрады и в случае наличия переноса соединены с шиной переноса двоичной единицы второго разряда предыдущей тетрады и т. д., входы суммато- , ров второй ступени связаны с выходами сумматоров первой ступени, и соответственно, дами сумматоров второй ступени, входы схемы определения переносов между десятичными разрядами соединены с выходами старших разрядов сумматоров первой ступени, со всеми выходами сумматоров второй ступени, со5 (I всеми выходами сумматоров третьей ступени в четвертом дополпительном десятичном разряде и с кодовыми шинами преобразуемого двоичного числа с четвертой ио десятую включительно.

I Единица переноса 6 старший десятичнь1й разряд

Фиг. 3

4 8

9,

()

q Единица переноса 6 Шразряд

Даты

1967-01-01—Публикация