Известные преобразователи двоичного кода в десятичный, содержащие сумматор, дешифратор и логические схемы, осуществляют преобразование двоичного кода в десятичный с разверткой во времени, что снижает быстродействие устройства.

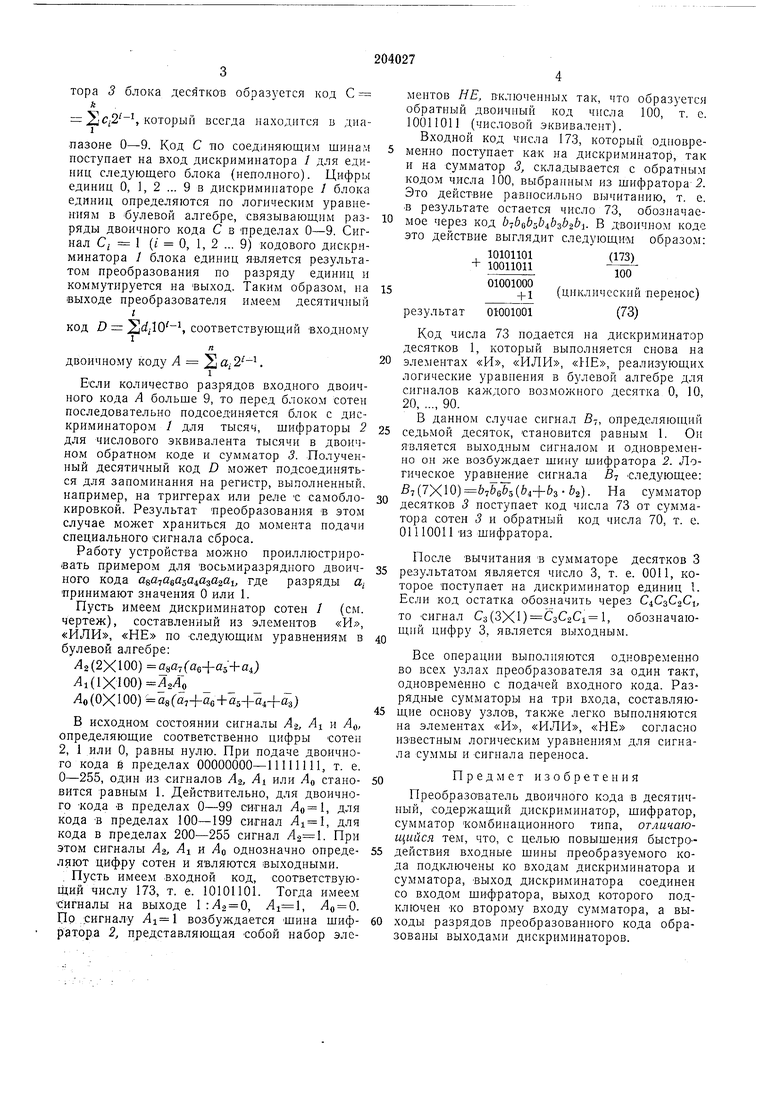

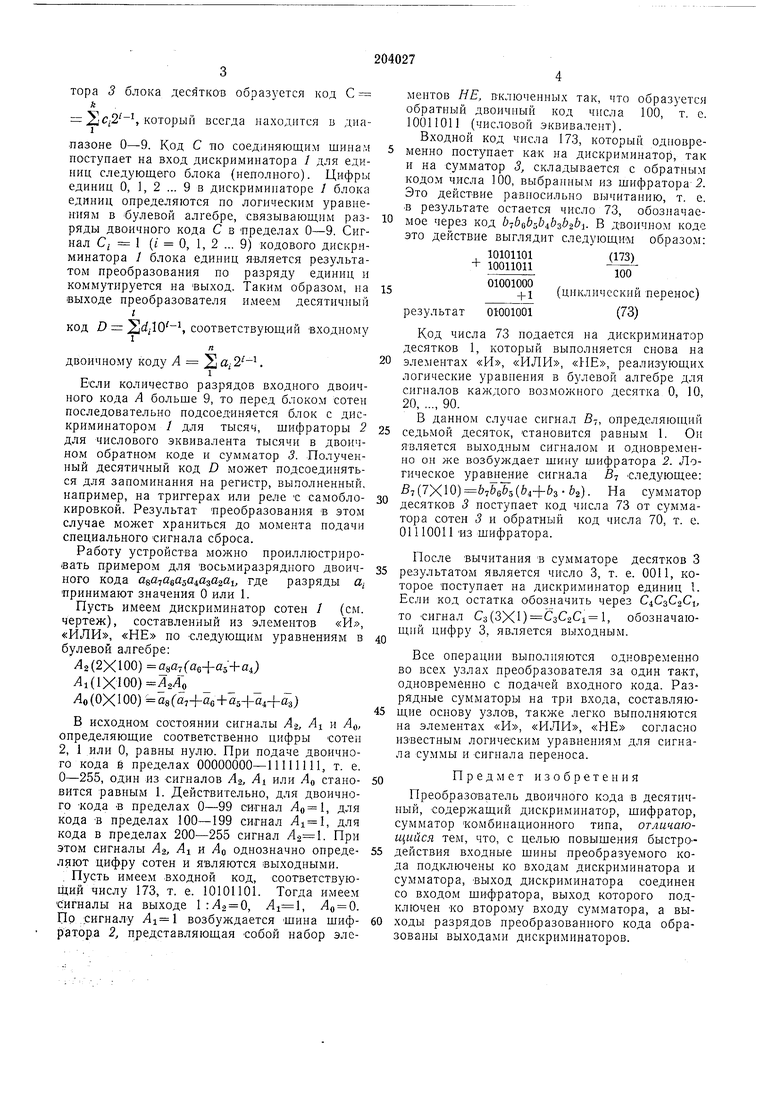

Предложенное устройство отличается от известных тем, что в нем входные шины преобразуемого кода подключены ко входам дискриминатора и сумматора, -выход дискриминатора соединен со входом шифратора, выход которого подключен ко второму входу сумматора, а выходы разрядов преобразованного кода образованы выходами дискриминаторов. На чертеже показана функциональная схема преобразователя.

Входной двоичный код л 2 ij 2 подаваемый параллельно, коммутируется на кодовый дискриминатор / цифры сотен и на один вход п-разрядного сумматора 3 блока сотен. Цифры сотен О, 1, 2 ... в дискриминаторе / определяются по логическим уравнением в булевой аЛГебре, связывающим разряды входного двоичного кода А в пределах 0-99, 100-199, 200-299 и т. д. Сигнал Л; 1 (г 0, 1, 2) кодового дискриминатора / блока СОтен является результатом преобразования по разряду сотен, коммутируется на

выход и на шифратор 2 для блока сотен. По этому сигналу с шифратора 2 на второй в.ход сумматора 3 по соединяющим шинам поступает числовой экви валент выбранной сотни в виде обратного двоичного кода. Сложение слагаемых в прямом и обратном двоичном коде в сумматоре равносильно операции вычитання.

Выходной код сумматора 3, обозначенный

через В 2,-2- всегда находится в диапа1

зоне О-99. Код «В заводится одновременно

на один вход сумматора 3 и на дискриминатор 1 десятков следующего блока. Цифры десятков О, 1, 2 ...8, 9 в дискриминаторе 1 определяются по логическим уравнениям в булевой алгебре, связывающим разряды двоичного кода «В в пределах 0-9, 10-19, 20-29, ... 80-89, 90-99. Сигнал В; Г (г О, 1, 2 ... 9) кодового дискриминатора 1, блока десятков, являющийся результатом преобразования по разряду десятков, коммутируется на выход н

заводится на щифратор 2 для десятков. По этому сигналу с щифратора 2 на второй вход сумматора 3 по соединяющим шинам поступает числовой эквивалент выбранного десятка :в виде обратного двоичного кода. В ретора 3 блока десятков образуется код С k - 2(2, который всегда находится в диапазоне О-9. Код С но соединяющим шинам поступает на вход дискриминатора / для единиц следующего блока (неполного). Цифры единиц О, 1, 2 ... 9 в дискриминаторе 1 блока единиц определяются по логическим уравнениям в булевой алгебре, связывающим разряды двоичного кода С в пределах О-9. Сигнал С,. 1 (г О, 1, 2 ... 9) кодового дискриминатора / блока единиц является результатом преобразования по разряду единиц и коммутируется на выход. Таким образом, на выходе преобразователя нмеем десятичный I код D , соответствующий входному двоичному коду /4 2 а/2 . Если количество разрядов входного двоичного кода А больше 9, то перед блоком сотен последовательно подсоединяется блок с дискриминатором / для тысяч, шифраторы 2 для числового эквивалента тысячи в двоичном обратном коде и сумматор 3. Полученный десятичный код D может подсоединяться для запоминания на регистр, выполненный, например, на триггерах или реле с самоблокировкой. Результат преобразования в этом случае может храниться до момента подачи специального сигнала сброса. Работу устройства можно проиллюстрировать примером для восьмиразрядного двоичного кода a aja a a azdzai, где разряды С; принимают значения О или 1. Пусть имеем дискриминатор сотен / (см. чертеж), составленный из элементов «И, «ИЛИ, «НЕ по следующим уравнениям в булевой алгебре: Л2(2Х100) asc fae+as+aj Л1(1Х100).42Ло Ло(ОХ100) аз (:а7+ае +«5+04+ 3) В исходном состоянии сигналы А, А- и Ло. определяющие соответственно цифры сотен 2, 1 или О, равны нулю. При подаче двоичного кода е пределах 00000000-11111111, т. е. О-255, один из сигналов А, А или Ло становится равным 1. Действительно, для двоичного -кода в пределах О-99 сигнал Ло 1, для кода В пределах 100-199 сигнал A-j , для кода в пределах 200-255 сигнал . При этом сигналы Ло, А и Ло однозначно определяют цифру сотен и являются выходными. . Пусть имеем входной код, соогветствую1ЦИЙ числу 173, т. е. 10101101. Тогда имеем сигналы на выходе 1 :Л2 0, , Ло 0. По .сигналу возбуждается шина щифратор.а 2, представляющая собой набор элементов НЕ, ВКлюченных так, что образуется обратный двоичный код числа 100, т. е. 10011011 (числовой эквивалент). Входной код числа 173, который одновременно поступает как на дискриминатор, так и на сумматор 3, складывается с обратным кодом числа 100, выбранным из шифратора 2. Это действие равносильно вычитанию, т, е. в результате остается число 73, обозначаемое через код . В двоичном коде это действие выглядит следующим образом: , 10101101 + 10011011 01001000 , (циклический перенос) результат 01001001 Код числа 73 подается на дискриминатор десятков 1, который выполняется снова на элементах «И, «ИЛИ, «НЕ, реализующих логические уравнения в булевой алгебре для сигналов каж:1,ого возможного десятка О, 10, 20, ..., 90. В данном случае сигнал Вт, определяющий седьмой десяток, становится равным 1. Он является выходным сигналом и одновременно он же возбуждает шину шифратора 2. Логическое уравнение сигнала B следующее: Б7(7Х10)(4+&з-Й2). На сумматор десятков 5 ноступает код числа 73 от сумматора сотен 3 и обратный код числа 70, т. е. 01110011 из шифратора. После вычитания в сумматоре десятков 3 результатом является число 3, т. е. ООП, которое поступает на дискриминатор единиц 1. Если код остатка обозначить через CiC3C2Ci, то сигнал Сз(ЗХ1)СзС2С1 1, обозначающий цифру 3, является выходным. Все операции выполняются одновременно во всех узлах преобразователя за один такт, одновременно с подачей входного кода. Разрядные сумматоры на три входа, составляющие основу узлов, также легко выполняются на элементах «И, «ИЛИ, «НЕ согласно нзвестным логическим уравнениям для сигнала суммы и сигнала переноса. Предмет изобретения Преобразователь двоичного кода в десятнчный, содержащий дискриминатор, шифратор, сумматор комбинационного типа, отличающийся тем, что, с целью повышения быстродействия входные щины преобразуемого кода подключены ко входам дискриминатора и сумматора, выход дискриминатора соединен со входом щифратора, выход которого подключен «о второму входу сумматора, а выходы разрядов преобразованного кода образованы выходами дискри.минаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1167737A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Реверсивный преобразовательдВОичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU849198A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1990 |

|

RU2010425C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНО- ДЕСЯТИЧНОГО КОДА | 1968 |

|

SU218522A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1330762A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

Авторы

Даты

1967-01-01—Публикация