Известны арифметические устройства цифрового дифференциального анализатора последовательно-последовательного или последовательно-параллельного типа, содержащие накапливающий сумматор для сложения приращений, сумматор для получения подынтегральной функции, множительное устройство и сумматор для получения приращения интеграла.

Предлагаемое устройство отличается от известных тем, что оно содержит первый и второй коммутаторы, первые входы которых соединены с выходом регистра хранения приращений, второй вход первого коммутатора подсоединен к выходу сумматора получения приращений интеграла, а его выход - ко входу накапливающего сумматора для сложения приращений. Выход последнего подключен ко второму входу второго коммутатора, выход которого связан со входом сумматора для получения подынтегральной функции.

Это позволяет уменьшить количество оборудования цифрового дифференциального анализатора.

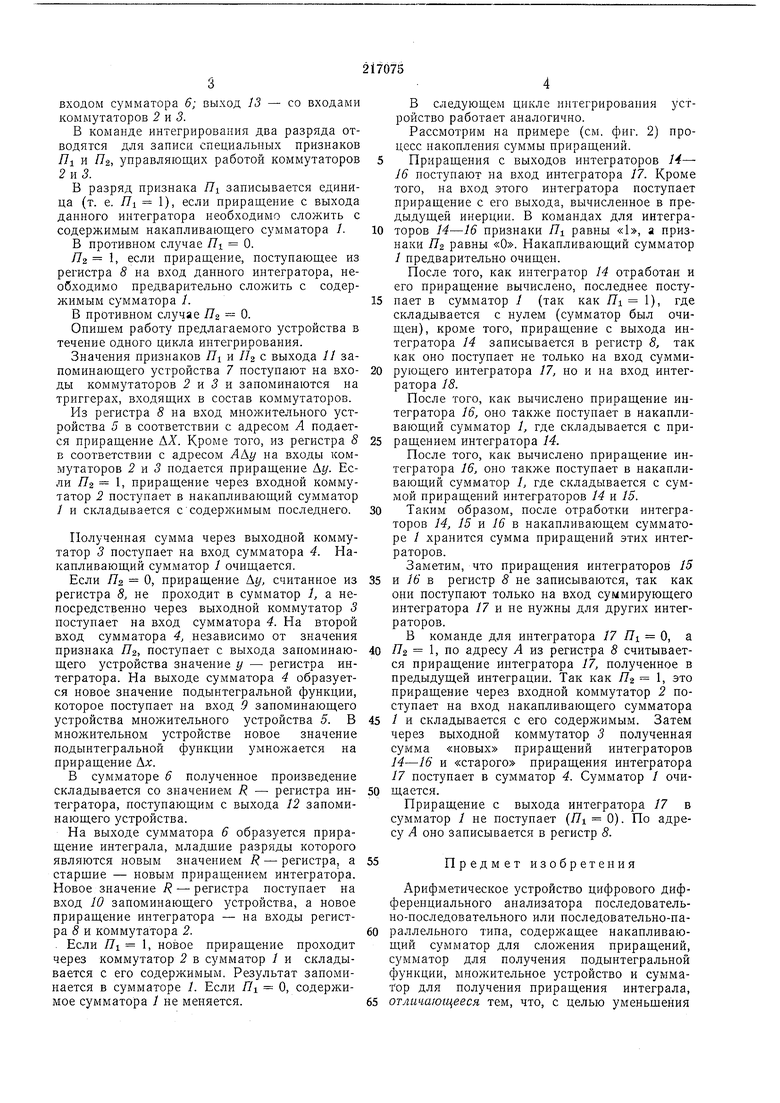

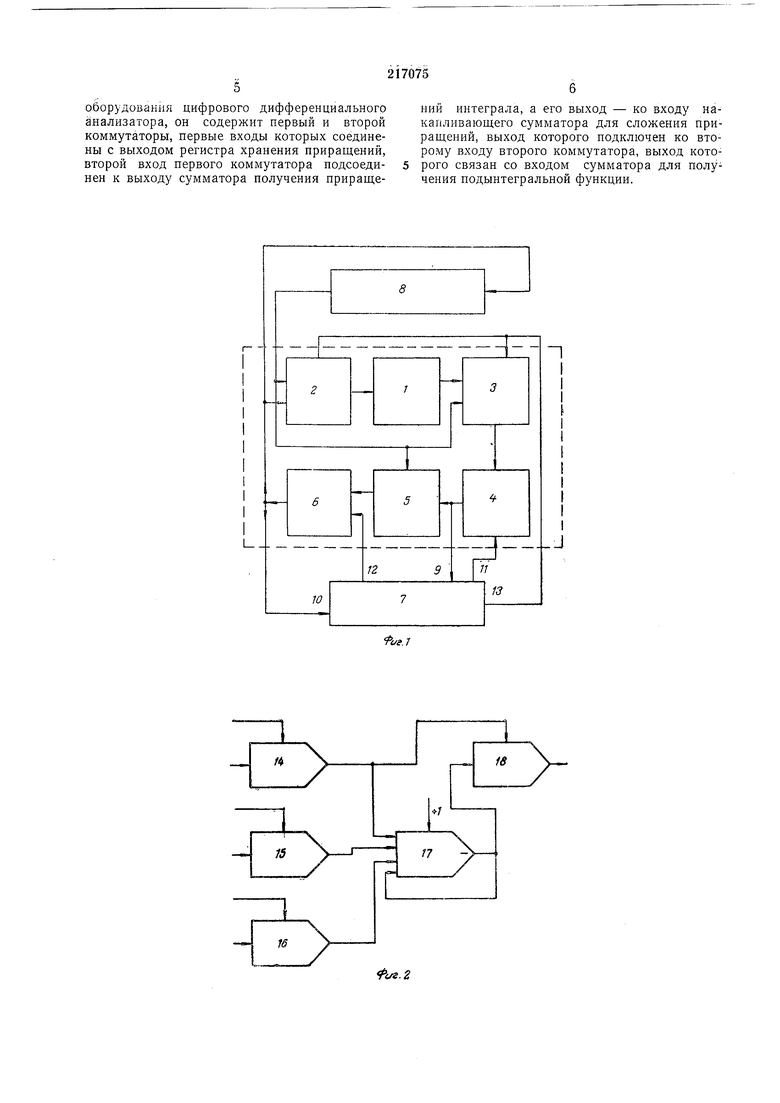

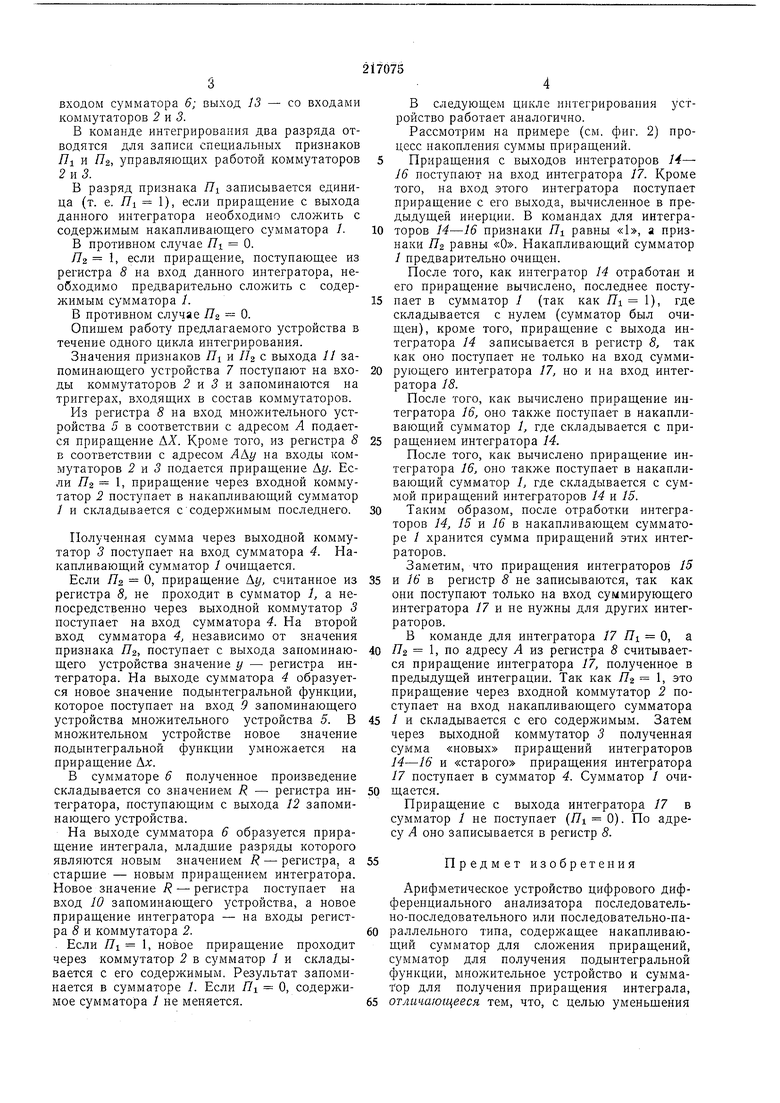

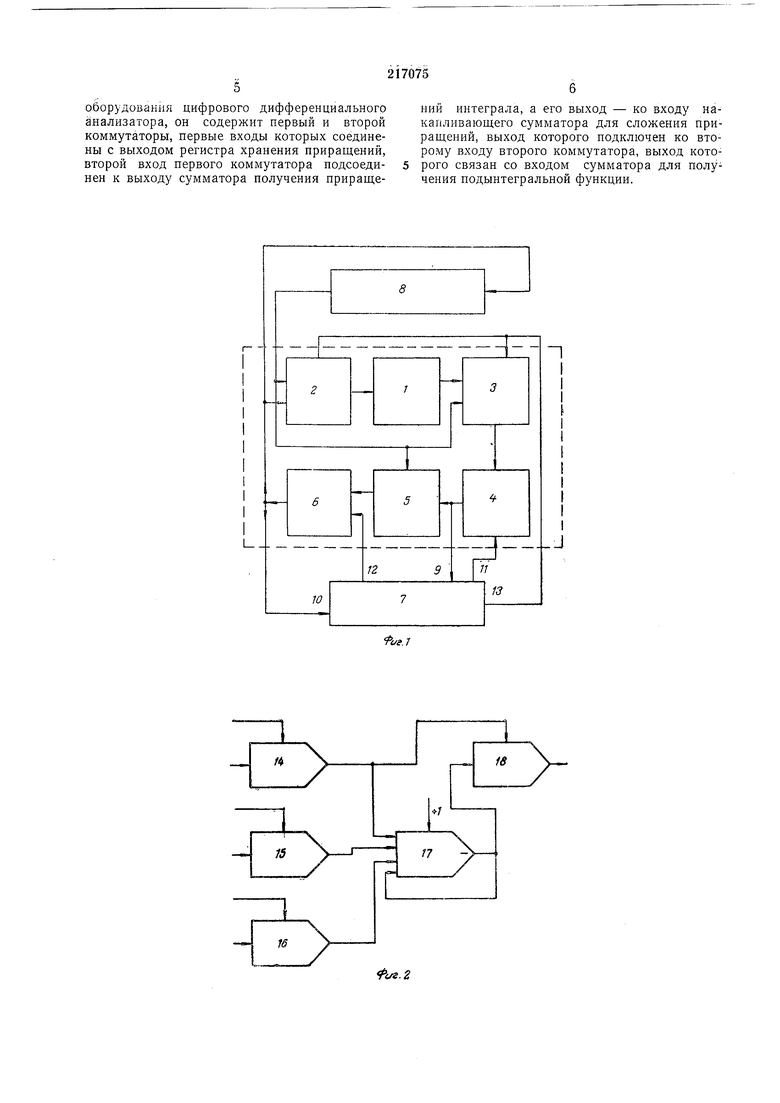

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - пример соединения интеграторов.

мутатор 2 на основе логических схем «И-ИЛИ и статических триггеров, управляющий вводом информации в сумматор; выходной коммутатор 3 на основе логических схем «И-ИЛИ и статических триггеров, управляющий выдачей информации из сумматора; сумматор 4 для получения нового значения подынтегральной функции, множительное устройство 5, сумматор 6 для образования приращения интеграла, запоминающее устройство 7 для хранения программы вычислений и значений у и R регистров интегралов, регистр 8 хранения приращений.

Выход регистра 8 соединен со входами коммутаторов 2, 3 и множительного устройства 5. Выход коммутатора 2 соединен со входом сумматора 1, а выход последнего - со входом коммутатора 3.

Выход комментатора 3 соединен со входом сумматора 4, а выход последнего - со входом множительного устройства 5 и со входом у запоминающего устройства 7.

Выход множительного устройства 5 соединен со входом сумматора 6, а выход последнего - со входами регистра 8 и коммутатора 2} и со входом 10 запоминающего устройства 7.

входом сумматора 6; выход 13 - со входами коммутаторов 2 и 3.

В команде интегрирования два разряда отводятся для записи специальных признаков 111 и ПУ, управляющих работой коммутаторов 2 и 5.

В разряд признака Я записывается единица (т. е. /7i 1), если приращение с выхода данного интегратора необходимо сложить с содержимым накапливающего сумматора /.

В противном случае Я 0.

Яз 1, если приращение, поступающее из регистра 8 на вход данного интегратора, необходимо предварительно сложить с содержимым сумматора /.

В противном случае Яз 0.

Опишем работу предлагаемого устройства в течение одного цикла интегрирования.

Значения признаков П и Яз с выхода // запоминающего устройства 7 поступают на входы коммутаторов 2 и 5 и запоминаются на триггерах, входящих в состав коммутаторов.

Из регистра 8 на вход мнол ительного устройства 5 в соответствии с адресом А подается приращение АХ. Кроме того, из регистра 8 в соответствии с адресом ЛАг/ на входы коммутаторов 2 и 3 подается приращение Дг/. Если Яз 1, приращение через входной коммутатор 2 поступает в накапливающий сумматор / и складывается с содержимым последнего.

Полученная сумма через выходной коммутатор 3 поступает на вход сумматора 4. Накапливающий сумматор / очищается.

Если Яз О, приращение At/, считанное из регистра 5, не проходит в сумматор 1, а непосредственно через выходной коммутатор 5 поступает на вход сумматора 4. На второй вход сумматора 4, независимо от значения признака Яз, поступает с выхода запоминающего устройства значение у - регистра интегратора. На выходе сумматора 4 образуется новое значение подынтегральной функции, которое поступает на вход .9 запоминающего устройства множительного устройства 5. В множительном устройстве новое значение подынтегральной функции умножается на приращение Ал:.

В сумматоре 6 полученное произведение складывается со значением R - регистра интегратора, поступающим с выхода 12 запоминающего устройства.

На выходе сумматора 6 образуется приращение интеграла, младшие разряды которого являются новым значением R - регистра, а старшие - новым приращением интегратора. Новое значение R - регистра поступает на вход 10 запоминающего устройства, а новое приращение интегратора - на входы регистра 8 и коммутатора 2.

. Если IJi 1, новое приращение проходит через коммутатор 2 в сумматор / и складывается с его содержимым. Результат запоминается в сумматоре 1. Если П О, содержимое сумматора 1 не меняется.

В следующем цикле интегрирования устройство работает аналогично.

Рассмотрим на примере (см. фиг. 2) процесс накопления суммы приращений. Приращения с выходов интеграторов 14- 16 ностунают на вход интегратора 17. Кроме того, на вход этого интегратора поступает приращение с его выхода, вычисленное в предыдущей инерции. В командах для интеграторов 14-16 признаки Я равны «1, а признаки Яа равны «О. Накапливающий сумматор 1 предварительно очищен.

После того, как интегратор 14 отработан и его приращение вычислено, последнее постунает в сумматор 1 (так как П, 1), где складывается с нулем (сумматор был очищен), кроме того, приращение с выхода интегратора 14 записывается в регистр 8, так как оно поступает не только на вход суммирующего интегратора 17, но и на вход интегратора 18.

После того, как вычислено приращение интегратора 16, оно также поступает в накапливающий сумматор /, где складывается с приращением интегратора 14.

После того, как вычислено приращение интегратора 16, оно также поступает в накапливающий сумматор 1, где складывается с суммой приращений интеграторов 14 и 15.

Таким образом, после отработки интеграторов 14, 15 и 16 Б накапливающем сумматоре / хранится сумма приращений этих интеграторов. Заметим, что приращения интеграторов 15

и 16 в регистр 8 не записываются, так как они поступают только на вход суммирующего интегратора 17 и не нужны для других интеграторов. В команде для интегратора 17 Ях О, а

Яз 1, по адресу А из регистра 8 считывается приращение интегратора 17, полученное в предыдущей интеграции. Так как Яз 1, это приращение через входной коммутатор 2 поступает на вход накапливающего сумматора

/ и складывается с его содержимым. Затем через выходной коммутатор 3 полученная сумма «новых приращений интеграторов 14-16 и «старого приращения интегратора 17 поступает в сумматор 4. Сумматор / очищается.

Приращение с выхода интегратора /7 в сумматор / не поступает (Я. 0). По адресу А оно записывается в регистр 8.

Предмет изобретения

Арифметическое устройство цифрового дифференциального анализатора последовательно-последовательного или последовательно-нараллельного типа, содержащее накапливающий сумматор для сложения приращений, сумматор для получения подынтегральной функции, множительное устройство и сумматор для получения приращения интеграла,

оборудования цифрового дифференциального анализатора, он содержит цервый и второй коммутаторы, первые входы которых соединены с выходом регистра хранения приращений, второй вход первого коммутатора подсоединен к выходу сумматора получения приращении интеграла, а его выход - ко входу накапливающего сумматора для сложения приращений, выход которого подключен ко второму входу второго коммутатора, выход которого связан со входом сумматора для получения подынтегральной функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU328482A1 |

| Цифровой интегратор | 1983 |

|

SU1191925A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор для решения краевых задач | 1984 |

|

SU1211712A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

Даты

1968-01-01—Публикация