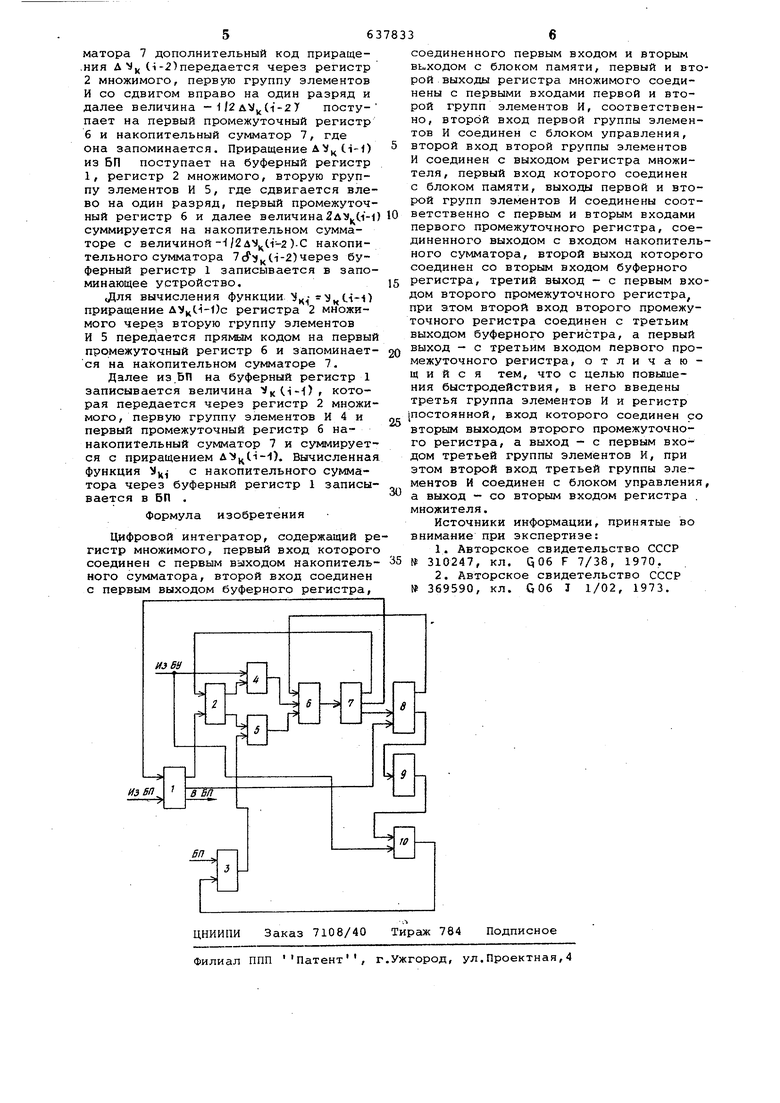

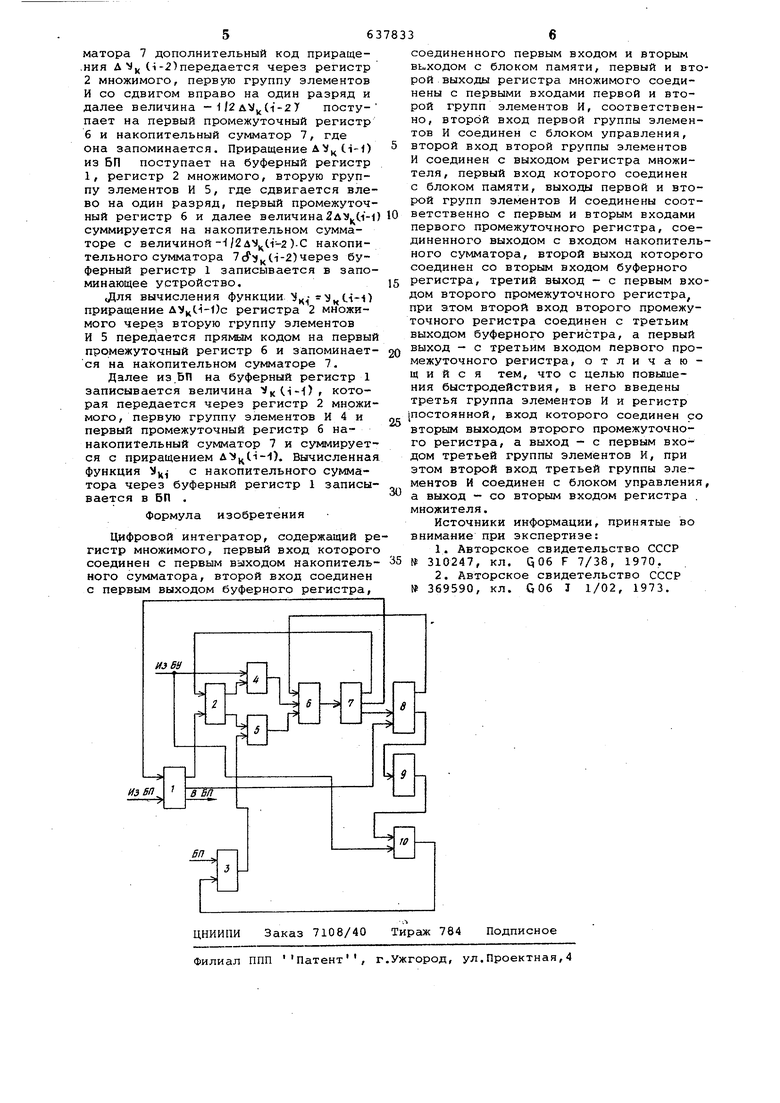

И соединен с блоком управления, а выход - со вторым входом регистра множителя. На чертеже представлена структурна схема описываемого цифрового интегратора, где 1 буферный регистр, 2 регистр множимого, 3 -регистр множите ля, 4 - первая группа элементов И, 5 - вторая группа элементов И, 6 первый промежуточный регистр, 7 - накопительный сумматор, 8 - второй промежуточный регистр, 9 - регистр постоянной, 10 - третья группа элементов И. Работа устройства показывается на примере реализации алгоритма интегрирования по формуле кубических парабол , ,) . -H/8d x)p(i-2)-2/3AX, ,-v)ti-1HAV(i-1), ()2uV(l-1)--f/2AV(l-2), (1) Выполняется алгоритм следующей по следовательности: S, Vp-i;2i.p, S, 2,51, й м/гдчр., 2:,2j-v-((i-2), П 2; 2уЗдХ, (1-2) )-Г/2д {1-2). ..) (2) Произведение 2/3 ДX, необходимое для всех блоков, вычисляется вначале решения задачи. Множитель .2/3 из блока управления записывается,в регистр 3 множителя. Множимое ДХ из БП поступает в регистр 2 множимого, и далее осуществляется умножение принятым в данном интеграторе способом. Полученнее произведение 2/Э ДX с накопительного сумматора 7 через второй промежуточный регистр 8 записывается в регистр 9 постояннойдля запоминания. Реализация алгоритма (2) осуществляется в следующей последовательности. Для образования суммы S подынтегральная функция )p.j из БП записывается в буферный регистр 1. Далее 5р,- через регистр 2 множимого, вторую группу элементов И 5 и первый про межуточный регистр 6 поступает в накопительный сумматор 7. Для получени 1/2Vpi функция Vp.j передается из ре гистра 2 множимого через первую груп пу элементов И 4 со сдвигом вправо н один разряд на первый промежуточный р гистр 6. В накопительном сумматоре 7 производится суммирование 1l2Sp c paнее записанной функцией . Получе . Получе ная сумма S.J передается для запоминания из накопительного сумматора 7 на второй промежуточный регистр 8. CSTviMa S2 получается аналогично. Приращение из БП записываетс в буферный регистр 1, откуда передается в регистр 2 множимого и через первую группу элементов И 4 со сдвигом вправо на один разряд в первый пр промежуточный регистр 6. Далее /2д:: p поступает в накопительный сумматор 7 Для получения /t6дSp1 величина 1/2 AVp-f с сумматора 7 поступает в регистр 2 множимого через первую группу элементов И 4 со сдвигом вправо на три разряда в первый промежуточный регистр 6. Полученная величина 1/16 д) складывается с записанной в накопительном сумматоре 7 величиной -1/2 uVpi . Полученная сумма S 2 запоминается в накопительном сумматоре 7. Величина S образуется при сложении величины S , и величины 2 / которая со второго промежуточного регистра 8 передается на первый промежуточный регистр б и суммируется с величиной S 2 , хранимой в накопительном сумматоре 7. Сумма запоминается на накопительном сумматоре 7. Для вычисления величины S из БП на буферный регистр 1 записывается величина (УЗр (i-2), которая поступает на регистр 2 множимого и далее через первую группу элементов И 4 со сдвигом вправо на три разряда на первый промежуточный регистр 6. Полученная величина 1/8 3pXi-2) передается в накопительный сумматор 7 и суммируется с величиной Sj . Для вычисления произведения П величина S4 .передается с сумматора 7 на регистр 2 множимого. Множитель Д с регистра 9 постоянной через третью группу элементов И 10 записывается в регистр 3 множителя. При умножении анализируются два младших разряда множителя 2/здХ . Результат анализа в виде управляющих сигналов подается на вторую группу элементов И 5, через которые множимое 2д с регистра 2 множимого в зависимости от этих управляющих сигналов передается либо прямым кодом. либо дополнительным кодом, либо прямым кодом со сдвигом влево на один разряд на первый промежуточный регистр б и в накопительный сумматор 7. Затем множитель сдвигается на регистре 3 множителя на два разряда, осуществляется анализ следующих двух разрядов множителя и соответствующая передача множимого через вторую группу элементов И 5 на первый промежуточный регистр 6 и накопительный сумматор 7. Этот процесс продолжается до тех пор, пока проанализируются все разряды множителя. В результате умножения 2д2/ЗдХ образуется приращение uу , которое передается с накопи v, тельного сумматора 7 через буферный регистр 1 в бП . Для получения величины cf: (.1-21 2ДN(1-)-1/2дv(-i-2)из БП на буферный регистр передается приращение (1-2), которое через регистр 2 множимого поступает на вторую группу элементов И 5 и дополнительным концом записывается на первый промежуточный регистр б и далее в накопительный сумматор 7. С накопительного сум

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Устройство для умножения двоичных чисел | 1985 |

|

SU1260948A1 |

| Устройство для умножения п-разрядных двоичных чисел | 1974 |

|

SU575651A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

Авторы

Даты

1978-12-15—Публикация

1975-11-13—Подача