Предложение относится к области импульсной и цифровой техники.

Известны буферные запоминающие устройства, предназначенные для снижения до допустимого значения местной (по времени) частоты следования импульсов и содержащие в качестве основного элемента следящий интегратор (нуль-орган) или пересчетные схемы.

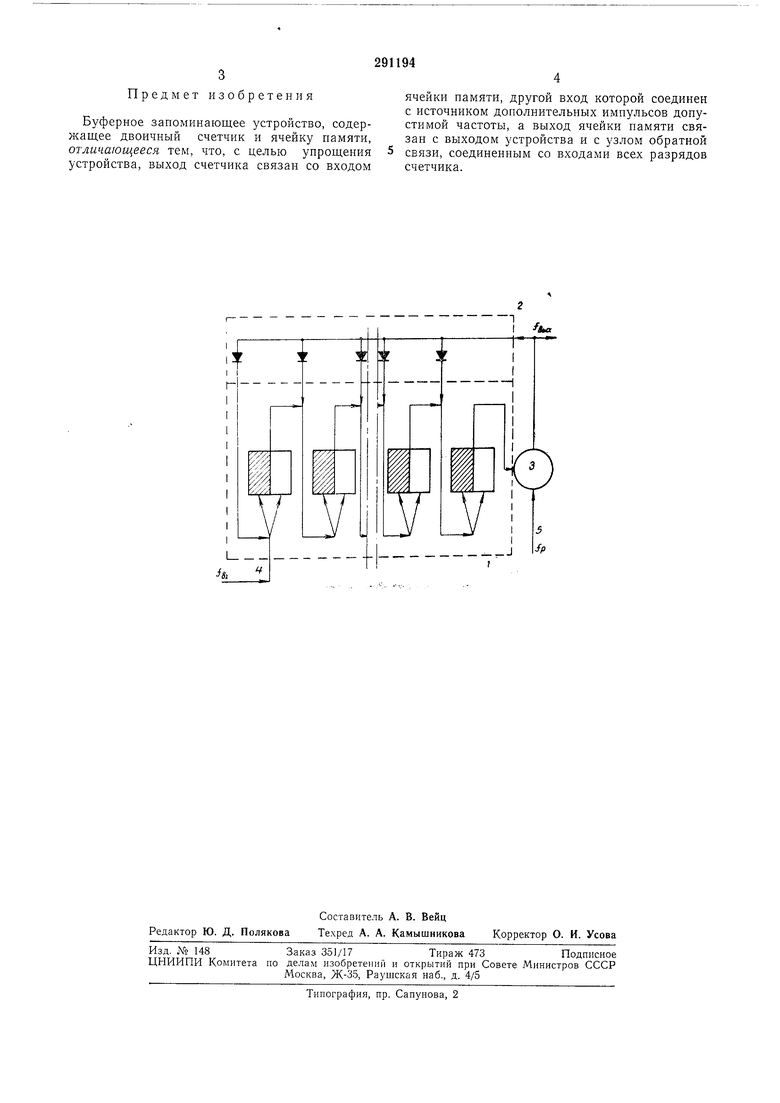

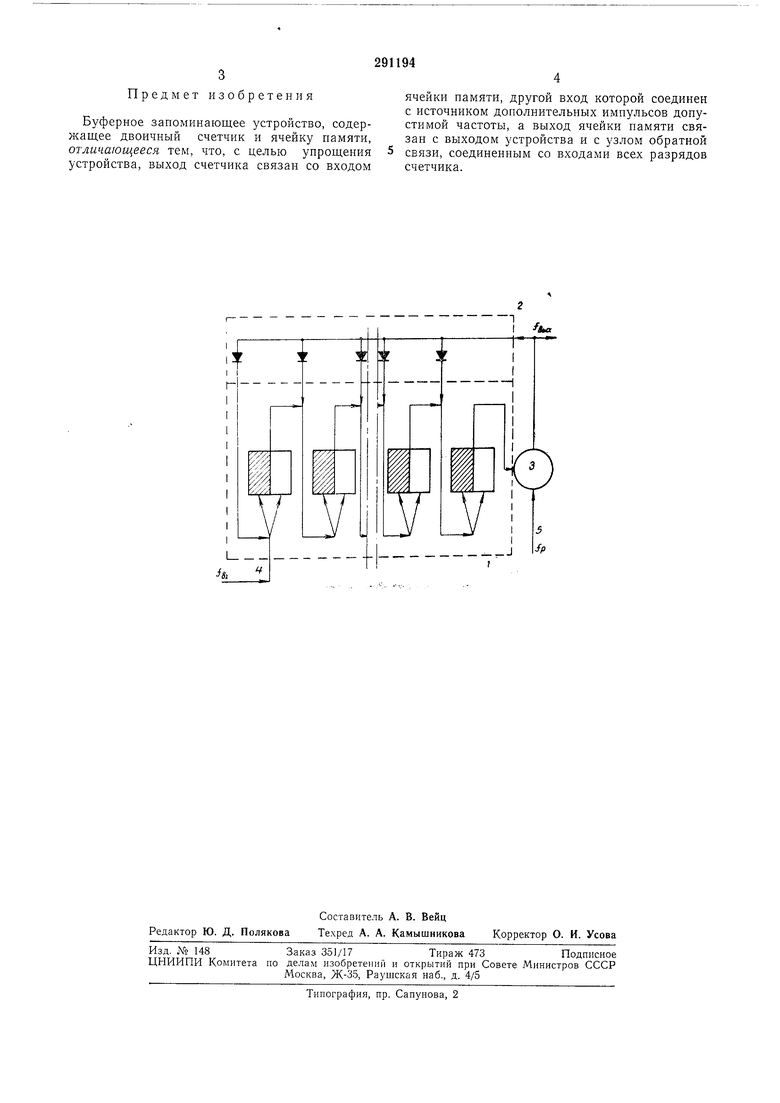

Предлагаемое устройство отличается тем, что выход счетчика связан со входом ячейки памяти, другой вход которой соединен с источником дополнительных импульсов допустимой частоты, а выход ячейки памяти связан с выходом устройства и с узлом обратной связи, соединенным со входами всех разрядов счетчика.

Это позволяет упростить устройство.

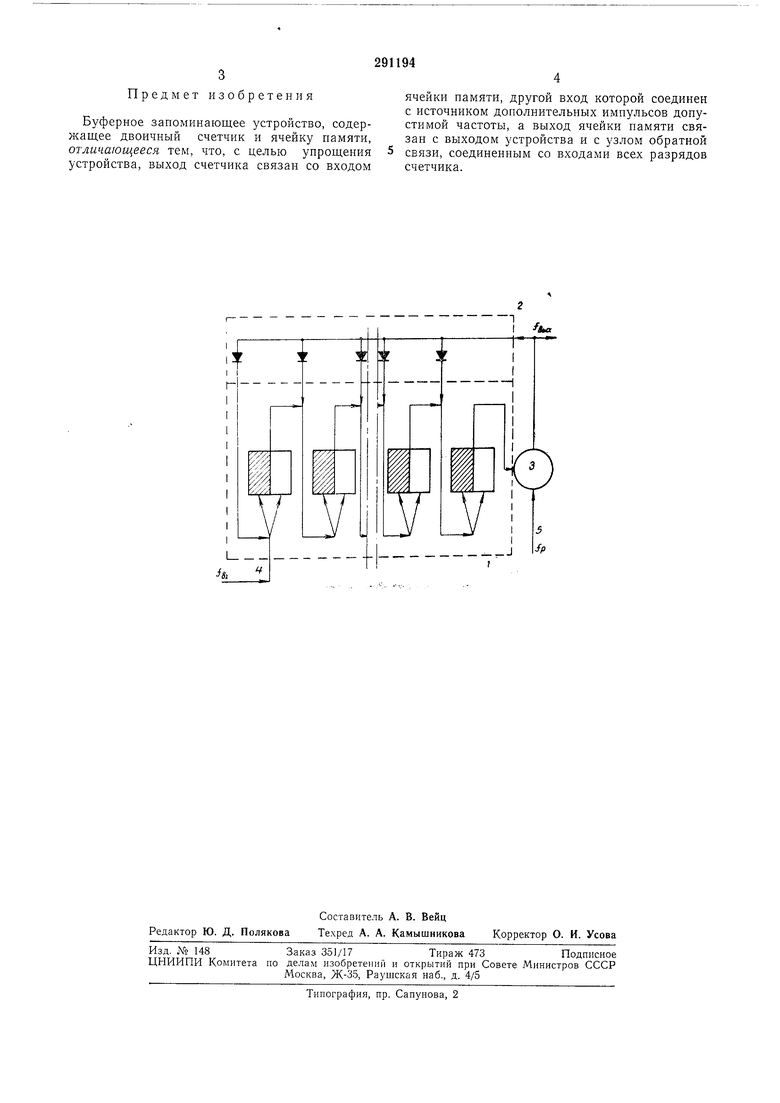

Схема устройства показана на чертеже.

Устройство содержит «-разрядный двоичный счетчик 1, узел обратной связи 2 и ячейку памяти 3. На вход 4 поступают входные импульсы с переменной частотой /, а на вход 5 - импульсы с рабочей частотой /р.

Устройство работает следующим образом.

Если в ячейке памяти 5 записана единица, то импульс частоты fp вызывает выходной импульс и формирует импульсы, поступающие через узел 2 одновременно на входы всех разрядов счетчика /, Совокупность этих импульсов иредставляет собой отрицательную единицу в дополнительном коде.

В исходном состоянии в счетч1 ке 1 хранится код «2п-1, а в ячейке 3 записан нуль. Первый входной импульс частоты вызовет «очищение счетчика / и запись единицы в ячейку 3. В дальнейшем каждый входной импульс увеличивать, а выходной импульс (частоты fp) уменьщать содержимое счетчика 1 на единицу, и с выхода буферного запоминающего устройства будут выдаваться импульсы с ггостоянной частотой до тех пор, пока содержимое счетчика не станет равным нулю.

Когда в некоторый момент в счетчике / останется лишь единица, очередной код обратной связи вызовет очищение счетчика / и запись единицы в ячейку 3, и если к моменту /; поступления следующего импульса частоты /р на вход счетчика не поступит очередной импульс частоты /, то буферное устройство, выдав еще один импульс выходной частоты fp, вернется в исходное состояние.

До поступления очередного импульса частоты / импульсы частоты fp не будут вызывать

5 выдачи вы.ходных импульсов и изменения состояния буферного запоминающего устройства. Общее число импульсов, выданных буферным устройством на момент ti, будет равно числу ноступивщих на его вход нмпульсов частоты f.

Предмет изобретения

Буферное запоминающее устройство, содержащее двоичный счетчик и ячейку памяти, отличающееся тем, что, с целью упрощения устройства, выход счетчика связан со входом

ячейки памяти, другой вход которой соединен с источником дополнительных импульсов допустимой частоты, а выход ячейки памяти связан с выходом устройства и с узлом обратной связи, соединенным со входами всех разрядов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU512484A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство преобразования временных интервалов в двоичный код для процесса сбора,обработки и передачи многоканального потока информации | 1982 |

|

SU1015494A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| Запоминающее устройство | 1984 |

|

SU1257700A2 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

Даты

1971-01-01—Публикация