Изобретение относится к области вычислительной техники.

Известен запоминающий элемент на МОПтранзисторах, содержащий триггер из двух активных и двух нагрузочных транзисторов, адресные транзисторы, разрядные шины «единиц и «нулей, адресные шины и шину восстанавливающих импульсов.

Недостатком известного запоминающего элемента является сложная, схема ,и относительно большая ллощадь, занимаемая на подложке.

Предлагаемый запоминающий элемент (ЗУ) отличается тем, что сток одного нагрузочного транзистора соединен с разрядной шиной «единиц, сток другого - с разрядной шииой «нулей, а их затворы соединены с адресной шиной, но которой в промежутках меледу адресными импульсами для подпитки триггера подаются «восстанавливающие импульсы.

Это позволяет упростить схему и уменьшить площадь, занимаемую элементом на подложке.

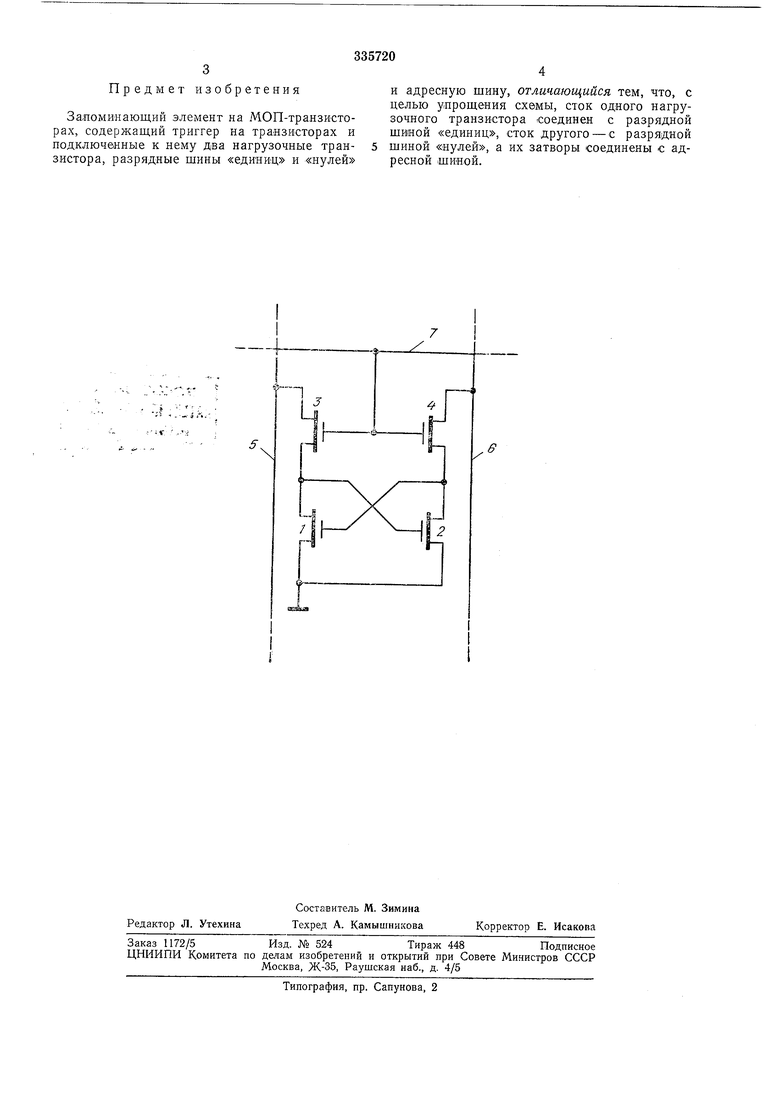

На чертеже показан запоминающий элемент.

Он содержит активные транзисторы /, 2; нагрузочные транзисторы 3, 4, разрядную шину «единиц 5, разрядную шину «нулей 6 и адресную шину 7.

Запоминающий элемент .работает следующим образом.

Хранение информации достигается подзарядкой паразитной емкости затвора активных транзисторов / или 2 путем подачи восстанавливающих импульсов по адресной шине 7 в промежутках между циклами записи и считывания. Шина 7 имеет потенциал подложки, разрядные шины 5, 6 - потенциал источника питания-.

Запись осуществляется одновременной подачей адресного импульса на затворы транзисторов 3, 4 и импульса записи по одной из шин 5 или 6. При этом происходит перезаряд емкостей затворов транзисторов /, 2 и ЗУ переходит в новое устойчивое состояние или, если запись была подтверждающей, то элемент сохраняет прежнее состояние.

При поступлении на затворы транзисторов 3, 4 адресного импульса, они открываются и подключают шины 5 и б к транзисторам / и 2

соответственно. В разрядной шине, которая подключается к открытому транзистору, появляется ток, являющийся сигналом считывания. В другой разрядной шине протекает ток помехи, который намного меньше сигнала счиПредмет изобретения

Запоминающий элемент на МОП-транзисторах, содержащий триггер на транзисторах и подключенные к нему два нагрузочные транзистора, разрядные шины «единиц и «нулей

и адресную шину, отличающийся тем, что, с целью упрощения схемы, сток одного нагрузочного транзистора соединен с разрядной щиной «единиц, сток другого-с разрядной щиной «нулей, а их затворы соединены с адресной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| ИНТЕГРАЛЬНАЯ МАТРИЦА НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU342222A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU731474A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕЛ1ЕНТ | 1971 |

|

SU289446A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Запоминающий элемент на мдп транзисторах | 1973 |

|

SU450230A1 |

Даты

1972-01-01—Публикация