|1

Изобретение относится к технике, решающей задачу сбора дискретной информации от двухпозиционных датчиков для передачи ее в устройство приема и обработки информацией, в частности в управляющую вычислительную машину.

В отличие от известных устройств предлагаемое изобретение расширяет функциональные возможности устройства сбора данных от пвухпозиционных датчиков, сокращает объем передаваемых от пего данных с одновременным увеличением полпоты передаваемых сведений с поведений датчиков, повышает надежность и экономичность устройства, а также обеспечивает возможность его построения па иптгегралъных схемах со средней и большой степенью интеграции.

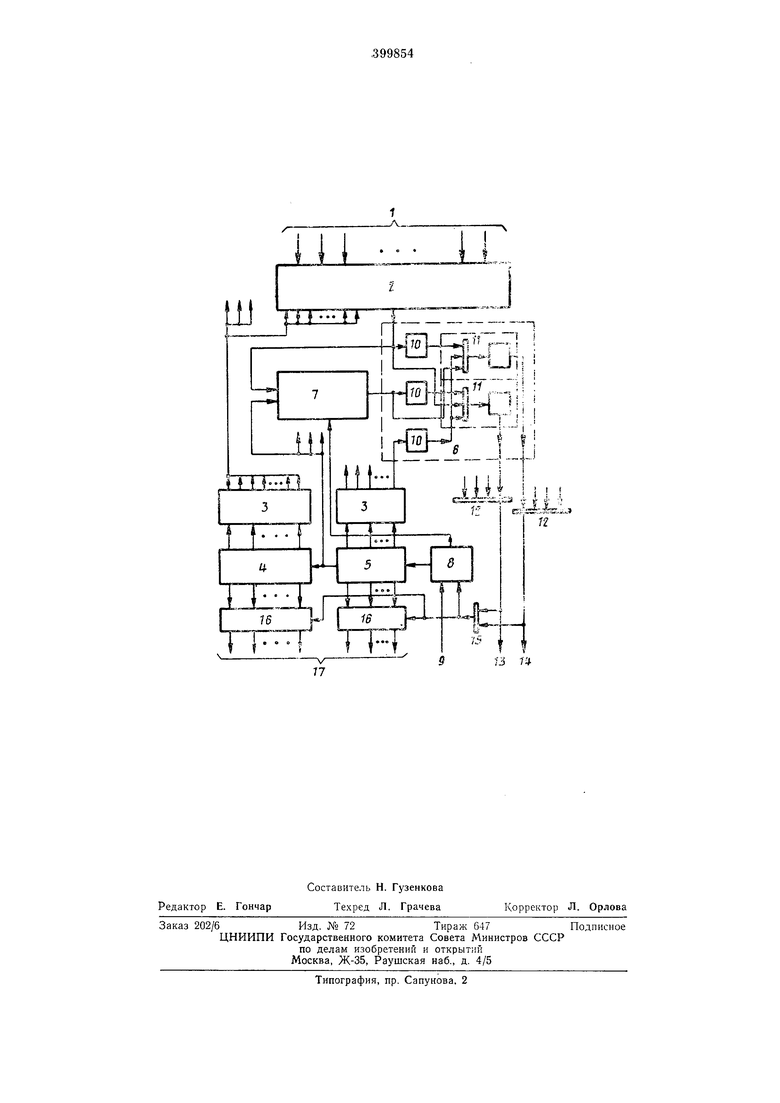

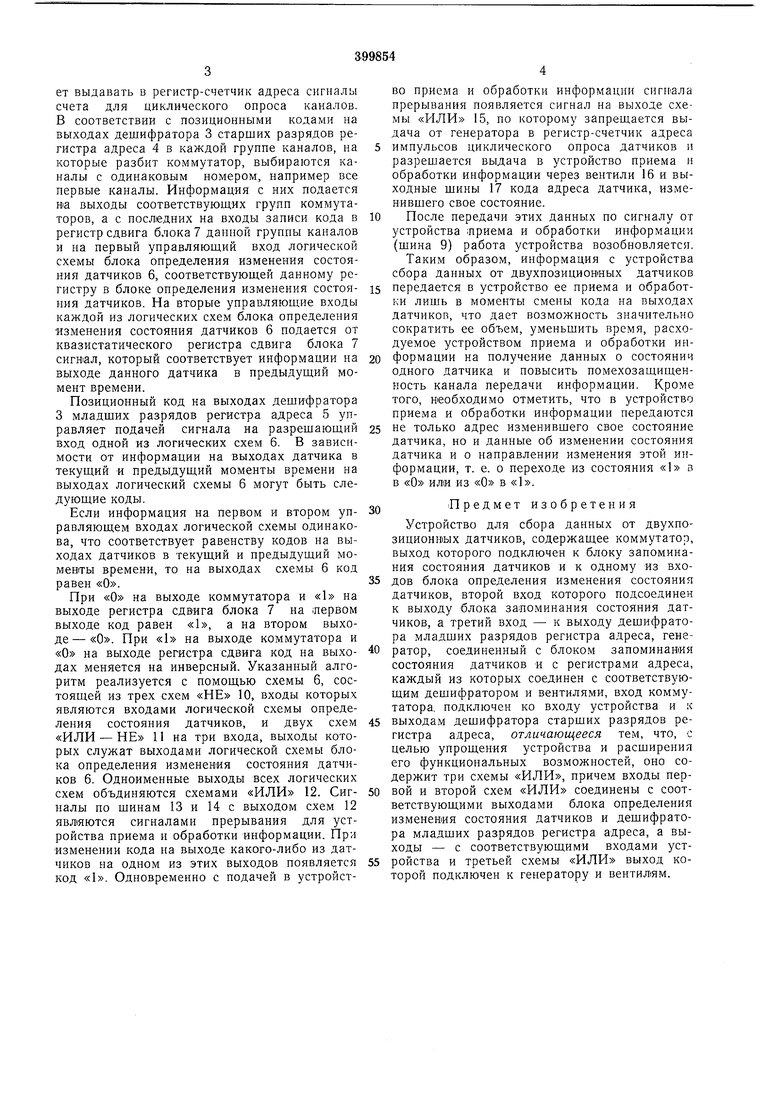

На чертеже приведна схема устройства.

Сигналы от датчиков поступают на входы 1 коммутатора 2, на который от дешифратора 3 старших разрядов регистра адреса 4 подаются управляющие сигналы. Коммутатор разбит на несколько частей - групп каналов (на чертеже показана лишь одна группа). В каждой из групп число каналов равно числу выходов дешифратора 3 старших разрядов регистра адреса 4, а общее число групп каналов равно числу выходов дешифратора 3 младших разрядов регистра адреса 5.

Выход каждой группы каналов коммутатора соединен с первым управляющим входом соответствующей логической схемы блока определения изменения состояния датчиков бис входом записи кода соответствующего регистра блока запоминания состояния датчиков 7 (па чертеже изобрал ена лишь одна логическая схема и один регистр). Регистры блока 7 выполнены на квазистатических элементах и

имеют число разрядов, равное числу каналов в данной группе коммутатора. Число логических схем в блоке определения изменения состояния датчиков равно числу выходов дешифратора 3 младших разрядов регистра адреса 5.

На входы квазистатического регистра блока 7, построенного на интегральных схемах с МОП-структурой, поступают тактовые сигналы от генератора 8 и сигналы сдвига информации с выхода, служащего соединением

младших и старших разрядов в регистре адреса 5 и 4. Информация с выхода регистра сдвига поступает на второй управляюший вход соответствующей логической схемы блока определения изменения состояния датчиков

6, па третий - разрешающий вход которой подается сигнал с одного из выходов дешифратора 3 младших разрядов регистра адреса 5. Устройство работает следующим образом. По сигналу от устройства приема и обработки информации (шина 9) генератор 8 начинает выдавать в регистр-счетчик адреса сигналы счета для циклического опроса каналов. В соответствии с позиционными кодами на выходах дешифратора 3 старших разрядов регистра адреса 4 в каждой группе каналов, на которые разбит коммутатор, выбираются каналы с одинаковым номером, например все первые каналы. Информация с них подается ва выходы соответствующих групп коммутаторов, а с последних на входы записи кода в регистр сдвига блока 7 данной групиы каналов и на первый управляющий вход логической схемы блока определения изменения состояния датчиков 6, соответствующей данному регистру в блоке определения изменения состояния датчиков. На вторые управляющие входы каждой из логических схем блока определения изменения состояния датчиков 6 подается от квазистатического регистра сдвига блока 7 сигнал, который соответствует информации на выходе данного датчика в предыдущий момент времени.

Позиционный код на выходах дещифратора 3 младщих разрядов регистра адреса 5 управляет подачей сигнала на разрешающий вход одной из логических схем 6. В зависимости от информации на выходах датчика в текущий и предыдущий моменты времени на выходах логический схемы 6 могут быть следующие коды.

Если информация на первом и втором управляющем входах логической схемы одинакова, что соответствует равенству кодов на выходах датчиков в текущий и предыдущий момееты времени, то на выходах схемы 6 код равен «О.

При «О на выходе коммутатора и «1 на выходе регистра сдвига блока 7 на терном выходе код равен «1, а на втором выходе- «О. При «1 на выходе коммутатора и «О на выходе регистра сдвига код на выходах меняется на инверсный. Указанный алгоритм реализуется с помощью схемы 6, состоящей из трех схем «НЕ 10, входы которых являются входами логической схемы определения состояния датчиков, и двух схем «ИЛИ - НЕ 11 на три входа, выходы которых служат выходами логической схемы блока определения изменения состояния датчиков 6. Одноименные выходы всех логических схем объдиняются схемами «ИЛИ 12. Сигналы по шинам 13 и 14 с выходом схем 12 являются сигналами прерывания для устройства приема и обработки информации. При изменении кода на выходе какого-либо из датчиков на одном из этих выходов появляется код «Ь. Одновременно с подачей в устройство приема и обработки информации сигнала прерывания появляется сигнал на выходе схемы «ИЛИ 15, по которому запрещается выдача от генератора в регистр-счетчик адреса импульсов циклического опроса датчиков и разрешается выдача в устройство приема и обработки информации через вентили 16 и выходные шины 17 кода адреса датчика, изменившего свое состояние.

После передачи этих данных по сигналу от

устройства ;приема и обработки информации

(шина 9) работа устройства возобновляется.

Таким образом, информация с устройства

сбора данных от двухпозициовных датчиков

передается в устройство ее приема и обработки лишь в моменты смены кода на выходах датчиков, что дает возможность значительно сократить ее объем, уменьшить время, расходуемое устройством приема и обработки информации на получение данных о состоянии одного датчика и повысить помехозащищенность канала передачи информации. Кроме того, необходимо отметить, что в устройство приема и обработки информации передаются

не только адрес изменившего свое состояние датчика, но и данные об изменении состояния датчика и о направлении изменения этой информации, т. е. о переходе из состояния «1 в в «О или из «О в «1.

Предмет изобретения

Устройство для сбора данных от двухпозиционных датчиков, содержащее коммутатор, выход которого подключен к блоку запоминания состояния датчиков и к одному из входов блока определения изменения состояния датчиков, второй вход которого подсоединен к выходу блока запоминания состояния датчиков, а третий вход - к выходу дешифратора младщих разрядов регистра адреса, генератор, соединенный с блоком запоминания состояния датчиков и с регистрами адреса, каждый из которых соединен с соответствующим дешифратором и вентилями, вход коммутатора, подключен ко входу устройства и к

выходам дешифратора старших разрядов регистра адреса, отличающееся тем, что, с целью упрощения устройства и расширения его функциональных возможностей, оно содержит три схемы «ИЛИ, причем входы первой и второй схем «ИЛИ соединены с соответствующими выходами блока определения изменения состояния датчиков и дешифратора младщих разрядов регистра адреса, а выходы - с соответствующими входами устройства и третьей схемы «ИЛИ выход которой подключен к генератору и вентиЛ1Ям.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для ввода информации | 1983 |

|

SU1151945A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1971 |

|

SU297070A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

Авторы

Даты

1973-01-01—Публикация