Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам (ЗУ) электронных вычислительных машин.

Уже известны блоки управления выборкой информации из запоминающего устройства, состоящие из транзисторов, резисторов и источников питания.

Однако В известные блоки управления выборкой информации из ЗУ входит большое количество (6 транзисторов и 3 резистора) электрорадиоэлементов и они имеют два сигнальных входа.

Цель изобретения - повысить надежность работы блока управления.

Это достигается тем, что в нем коллектор первого транзистора через первый резистор подключен к первому источнику питания, а эмиттер соединен с шиной нулевого потенциала, коллектор второго транзистора соединен со вторым источником питания, эмиттер через второй резистор подключен к шине нулевого потенциала, а база соединена с коллектором первого транзистора.

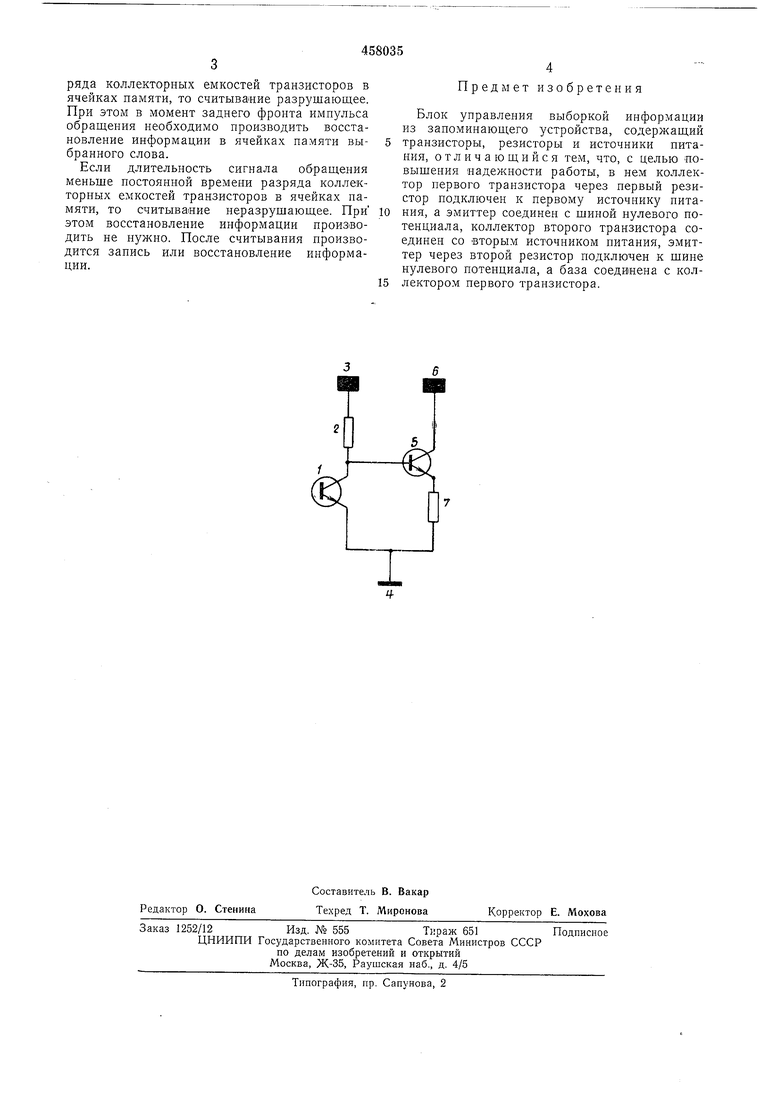

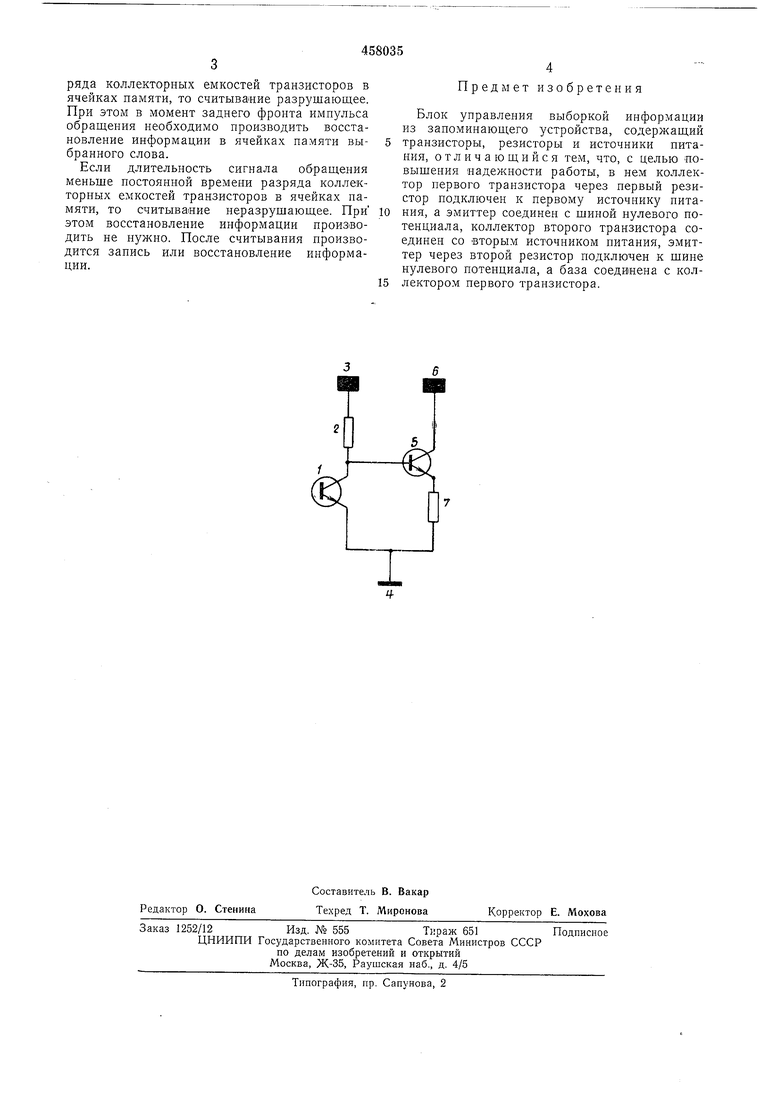

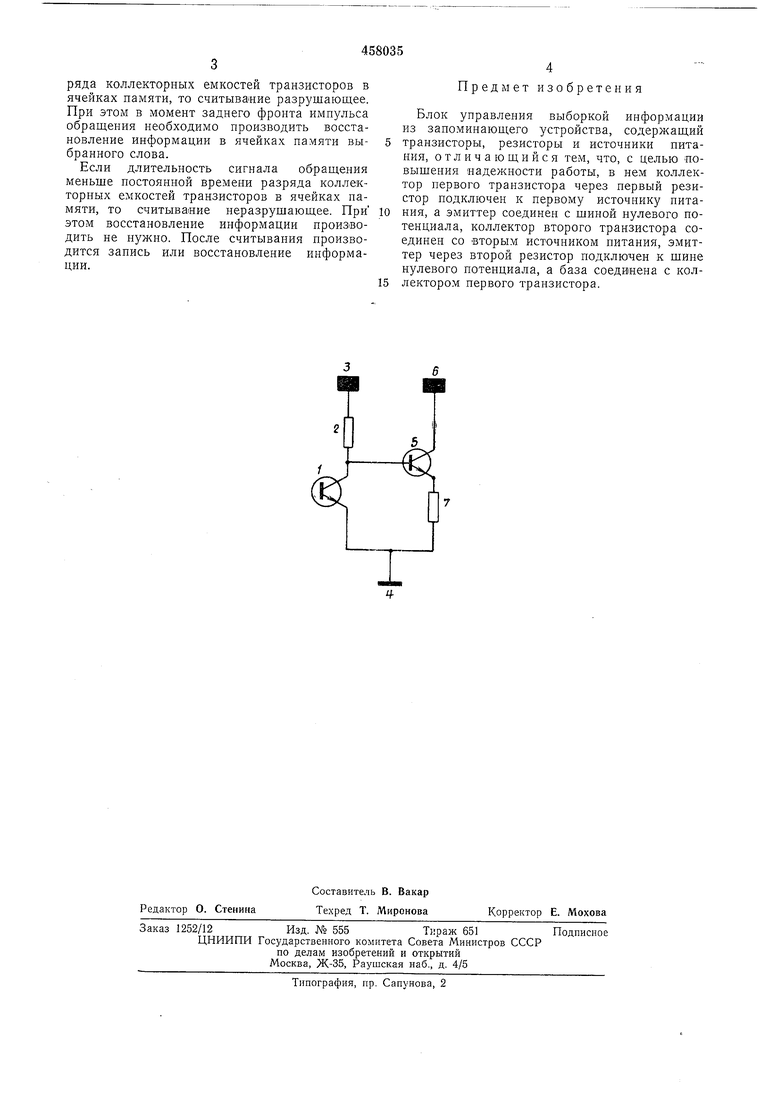

На чертеже представлен блок управления выборкой информации из ЗУ. Коллектор первого транзистора 1 через первый резистор 2 подключен к первому источнику питания 3, а эмиттер соединен с шиной нулевого потенциала 4, коллектор второго транзистора 5 соединен со вторым источником питания 6, эмиттер через второй резистор 7 подключен к шине нулевого потенциала 4, а база соединена с коллектором первого транзистора 1.

Блок управления выборкой информации из ЗУ работает следующим образом.

Возможны два режима работы: хранение информации (слово не выбрано) и обращение (запись или чтение информации в «акопителе).

В режиме хранения информации напряжение па входе блока управления равно нулю. Транзистор 1 закрыт, а транзистор 5 открыт. Источники питания 3 и 6 обеспечивают требуемое напряжение в линии слова, необходимое для храпения информации в ячейках запоминающего устройства.

В режиме обращения на входе транзистора 1 появляется положительный сигнал, транзистор открывается и яереходит в режим насыщения, напряжение на его коллекторе становится близким к нулю. Транзистор 5 закрывается. Напряжение в линии слова падает до нуля, что приводит к возникновению сигнала чтения отрицательной полярности.

В зависимости от длительности сигнала обращения считывание будет разрушающим или неразрушающим. Если длительность сигнала обращения больше постоянной времени ра ряда коллекторных емкостей транзисторов в ячейках памяти, то считывание разрушающее. При этом в момент заднего фронта импульса обращения необходимо производить восстановление информации в ячейках памяти выбранного слова.

Если длительность сигнала обращения меньше постоянной времени разряда коллекторных емкостей транзисторов в ячейках памяти, то считывание неразрущающее. При этом восстановление информации производить не нужно. После считывания производится запись или восстановление информации.

Предмет изобретения

Блок управления выборкой информации из запоминающего устройства, содержащий транзисторы, резисторы и источники питания, отличающийся тем, что, с целью повыщения надежности работы, в нем коллектор первого транзистора через первый резистор подключен к первому источнику питания, а эмиттер соединен с щиной нулевого потенциала, коллектор второго транзистора соединен со вторым источником питания, эмиттер через второй резистор подключен к щине нулевого потенциала, а база соединена с коллектором первого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1979 |

|

SU799002A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

Авторы

Даты

1975-01-25—Публикация

1971-05-31—Подача