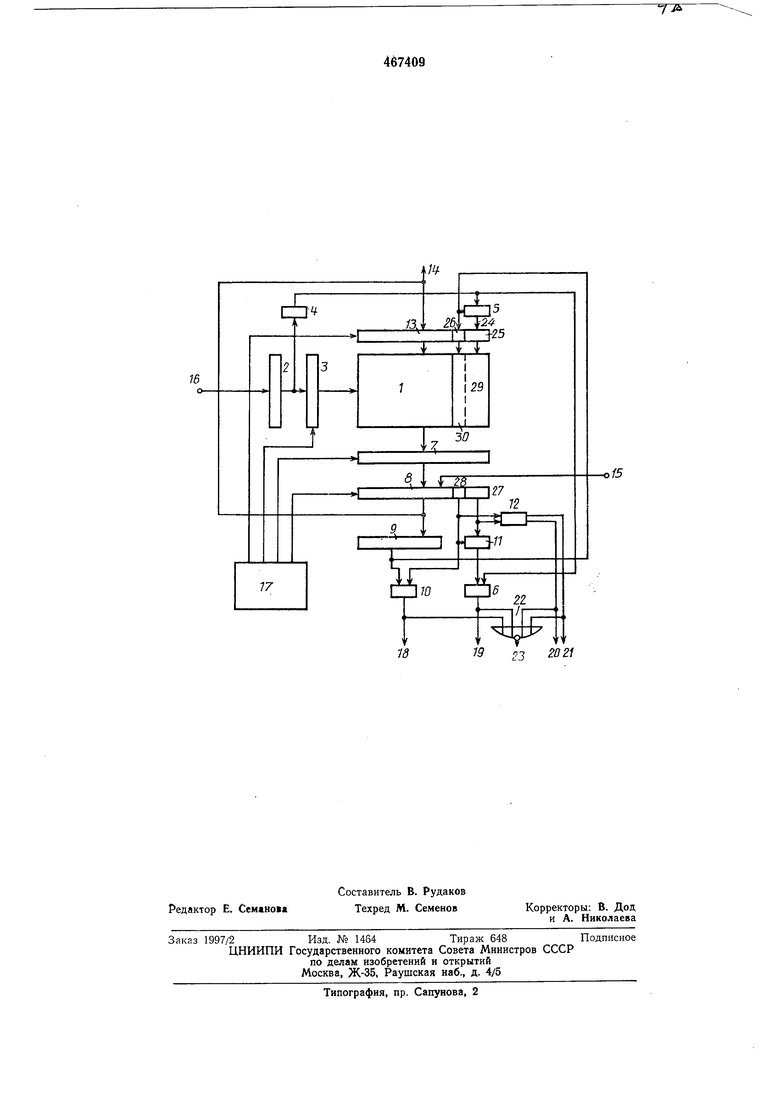

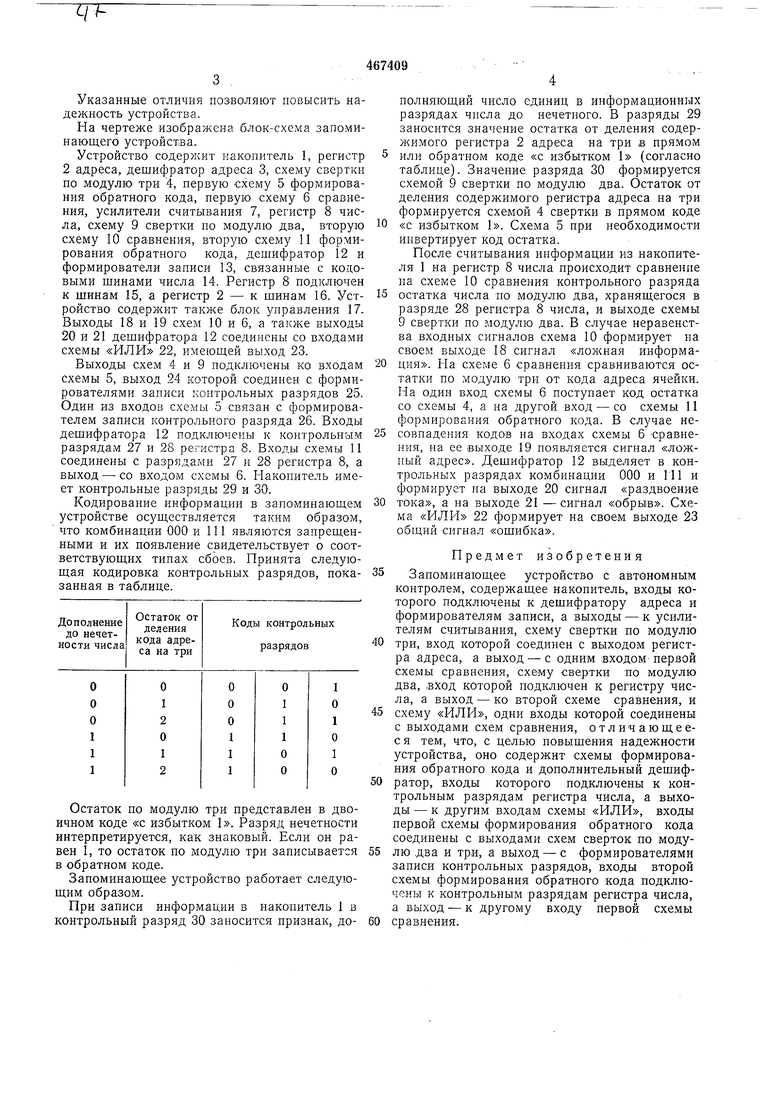

Указанные отличия позволяют повысить надежность устройства. На чертеже изображена блок-схема запоминающего устройства. Устройство содержит накопитель 1, регистр 2 адреса, дешифратор адреса 3, схему свертки по модулю три 4, первую схему 5 формирования обратного кода, первую схему 6 сравнения, усилители считывания 7, регистр 8 числа, схему 9 свертки по модулю два, вторую схему 10 сравнения, вторую схему 11 формирования обратного кода, дешифратор 12 и формирователи записи 13, связанные с кодовыми шинами числа 14. Регистр 8 подключен к шинам 15, а регистр 2 - к шинам 16. Устройство содержит также блок управления 17. Выходы 18 и 19 схем 10 и 6, а также выходы 20 и 21 дешифратора 12 соединены со входами схемы «ИЛИ 22, имеюш,ей выход 23. Выходы схем 4 и 9 подключены ко входам схемы 5, выход 24 которой соединен с формирователями записи контрольных разрядов 25. Один из входов схемы 5 связан с формирователем записи контрольного разряда 26. Входы дешифратора 12 подключены к контрольным разрядам 27 и 28 регистра 8. Входы схемы И соединены с разрядами 27 и 28 регистра 8, а выход -со входом схемы 6. Накопитель имеет контрольные разряды 29 и 30. Кодирование информации в запоминаюп ем устройстве осундествляется таким образом, что комбинации 000 и 111 являются запрещенными и их ноявление свидетельствует о соответствующих типах сбоев. Принята следующая кодировка контрольных разрядов, показанная в таблице. Остаток по модулю три представлен в двоичном коде «с избытком 1. Разряд нечетности интерпретируется, как знаковый. Если он равен 1, то остаток по модулю три записывается в обратном коде. Запоминающее устройство работает следующим образом. При записи информации в накопитель 1 в контрольный разряд 30 заносится признак, дополняющий число единиц в информационных разрядах числа до нечетного. В разряды 29 заносится значение остатка от деления содержимого регистра 2 адреса на три в прямом или обратном коде «с избытком 1 (согласно таблице). Значение разряда 30 формируется схемой 9 свертки по модулю два. Остаток от деления содержимого регистра адреса на три формируется схемой 4 свертки в прямом коде «с избытком 1. Схема 5 при необходимости инвертирует код остатка. После считывания информации из накопителя 1 на регистр 8 числа происходит сравнение на схеме 10 сравнения контрольного разряда остатка числа по модулю два, хранящегося в разряде 28 регистра 8 числа, и выходе схемы 9 свертки по модулю два. В случае неравенства входных сигналов схема 10 формирует на своем выходе 18 сигнал «ложная информация. На схеме 6 сравнения сравниваются остатки по модулю три от кода адреса ячейки. На один вход схемы 6 поступает код остатка со схемы 4, а на другой вход - со схемы 11 формирования обратного кода. В случае несовпадения кодов на входах схемы 6 Сравнения, на ее выходе 19 появляется сигнал «ложный адрес. Дещифратор 12 выделяет в контрольных разрядах комбинации 000 и 111 и формирует на выходе 20 сигнал «раздвоение тока, а на выходе 21 - сигнал «обрыв. Схема «ИЛИ 22 формирует на своем выходе 23 общий Сигнал «ошибка. Нредмет изобретения Запоминающее устройство с автономным контролем, содержащее накопитель, входы которого подключены к дещифратору адреса и формирователям записи, а выходы - к усилителям считывания, схему свертки по модулю три, вход которой соединен с выходом регистра адреса, а выход - с одним входом первой схемы сравнения, схему свертки по модулю два, ,вход которой подключен к регистру ч-исла, а выход - ко второй схеме сравнения, и схему «ИЛИ, одни входы которой соединены с выходами схем сравнения, отлиЧающеес я тем, что, с целью повышения надежности устройства, оно содержит схемы формирования обратного кода и дополнительный дешифратор, входы которого подключены к контрольным разрядам регистра числа, а выходы - к другим входам схемы «ИЛИ, входы первой схемы формирования обратного кода соединены с выходами схем сверток по модулю два и три, а выход - с формирователями записи контрольных разрядов, входы второй схемы формирования обратного кода подключены к контрольным разрядам регистра числа, а выход - к другому входу первой схемы сравнения.

с5

г

75

2д,

24

325

i

29

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU985830A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

-of5

i гб

7

72

I СТ

11

75 яз 20 2i

5

Авторы

Даты

1975-04-15—Публикация

1973-07-18—Подача