1

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования кодов.

Известен преобразователь двоично-десятичного кода в двоичный, содержащий при преобразовании т-разрядного десятичного чит

ела, первый регистр с т разрядными, входы

о

которых соединены с выходами соответствующих разрядов г -разрядного сумматора.

т

Выходы () младших разрядов первого регистра соединены со входами соответстт

вующих разрядов ( )-разрядного второго регистра; устройство содержит также элементы «И и «ИЛИ.

Известный преобразователь характеризуется большим временем преобразования информации и большими аппаратурными затратами.

Целью изобретения является упрощение устройства и повышение его быстродействия.

Предложенное устройство отличается тем, что содержит дополнительную схему «И и схему «НЕ. Входы дополнительной схемы

«И соединены с входными шинами всех разрядов тетрады, соединенными со входами соответствующих младших разрядов сумматора. Выход дополнительной схемы «И соединен непосредственно и через схему «НЕ с управляющими входами второго и первого регистров соответственно.

Это позволяет повысить быстродействие устройства за счет совмещения циклов приема и преобразования информации и упростить его за счет использования периодичности поступления информации при управлении устройством.

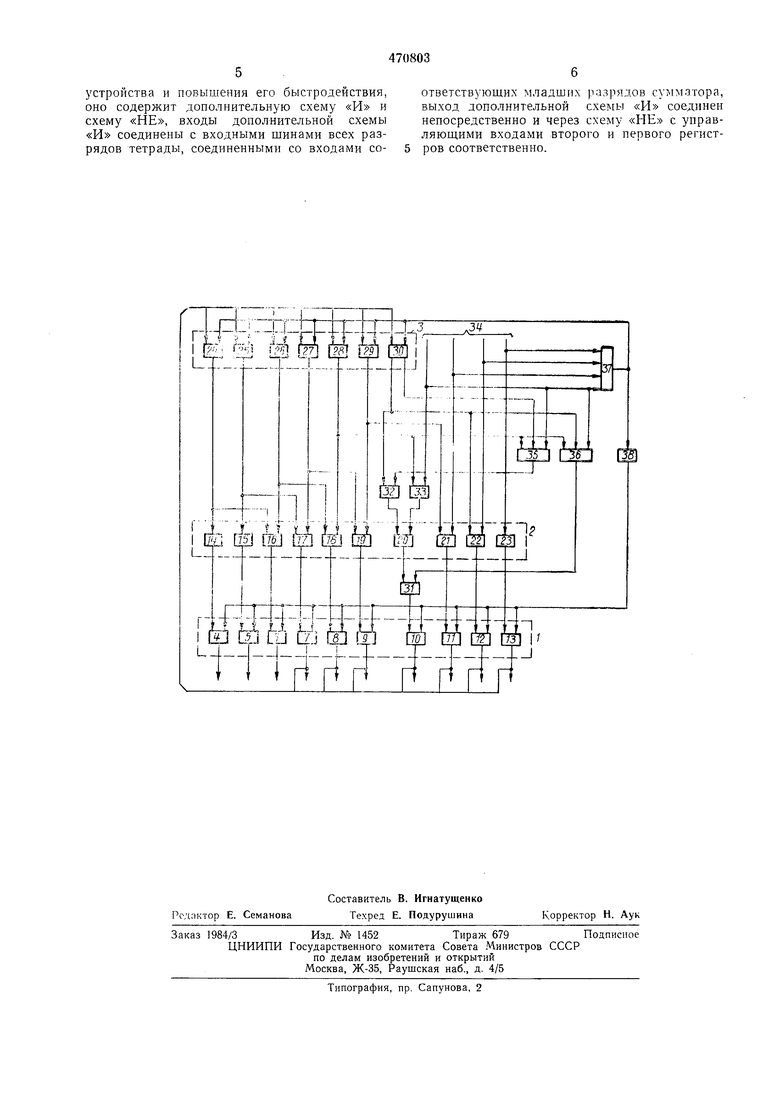

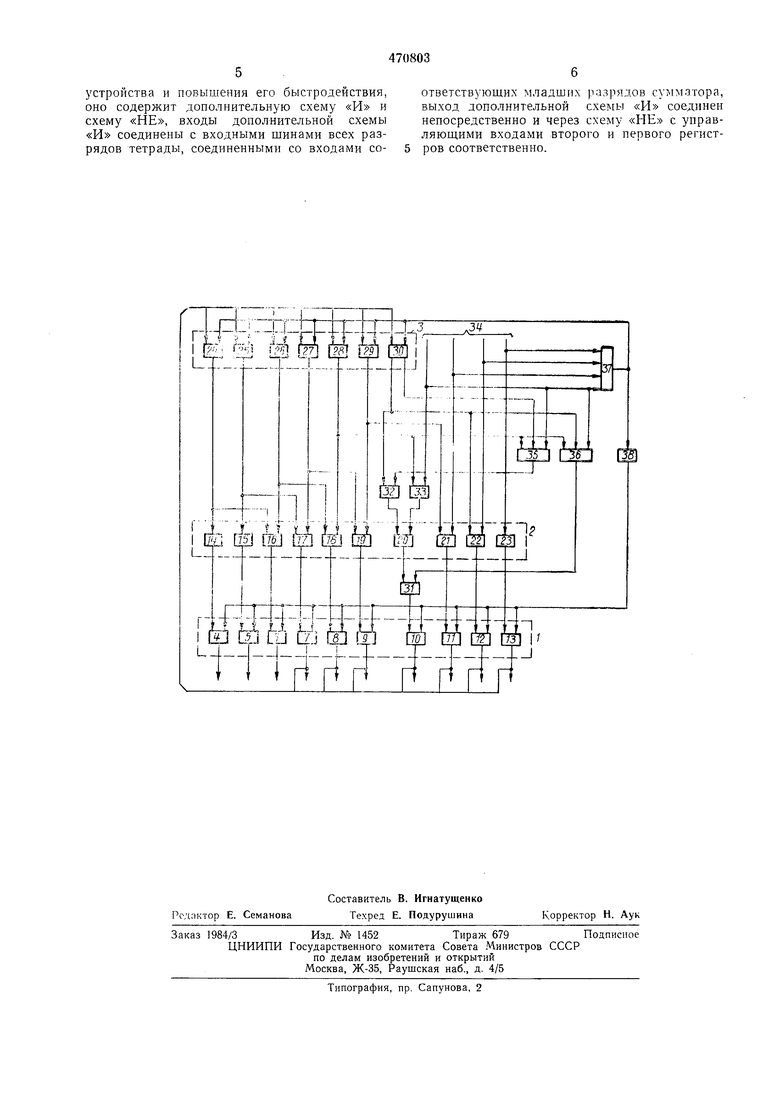

На чертеже изображена схема устройства для т 3, где т - количество разрядов преобразуемого десятичного числа.

Основу устройства составляют последоваттельно соединенные в кольцо j -разрядный

(для т 3 - десятиразрядный) регистр 1,

тт

.-г-разрядный сумматор 2 и (.-3)-разрядный регистр 3. Регистр 1 выполнен на триггерах 4-13. Сумматор 2 выполнен на одноразрядных сумматорах 14-23, а регистр 3 - на триггерах 24-30. Входы разрядов регистра 1 соединены с выходами соответствующих разрядов сумматора 2, причем их четвертые младшие разряды соединены через

IIL

схему «ИЛИ 31. Выходы ( )

младших

разрядов регистра i соединены со входами соответствующих разрядов регистра 3. Выход каждого i-ro разряда регистра 3, начиная со старшего разряда, неиосредственно или через схемы «ИЛИ 32 и «ИЛИ 33 соединены со входами i-ro и (i+2)-ro разрядов сумматора 2. Инверсный выход первого и выход третьего младших разрядов регистра 3 и входная шина 34 старше1-о разряда тетрады соединены со входами четвертого младшего разряда сумматора 2. Вход схемы «ИЛИ 32 соединен с выходом схемы «И 35. Входы схемы «И 36 соединены с выходами первого и третьего младших разрядов регистра 3 и с входной шиной старшего разряда тетрады 34, а выход схемы «И 36 соединен через схему «ИЛИ 31 со входом четвертого младшего разряда регистра 1. Входы схемы «И 37 соединены с входными шинами 34 всех разрядов аетрады, соединенными со входами соответствующих младших разрядов сумматора 2, при этом старший разряд тетрады соединен с четвертым младшим разрядом сумматора 2 через схему «ИЛИ 33. Выход схемы «И 37 соединен неиосредственно н через схему «ИЕ 38 - с управляющими входами регистров 3 и 1 соответственно.

Устройство работает следующим образом.

В исходном состоянии триггеры 4-13 и 24-30 регистров 1 и 3 установлены в состояние «О, информация на входе устройства отсутствует, что соответствует подаче на входные шины 34 кода 1111. При этом со схемы «И 37 на регистр 3 поступает сигнал, разрешающий запись информации, снимаемой с выходов регистра 1, а со схемы «НЕ 38 на регистр 1 поступает сигнал, запрещающий запись информации, снимаемой с выходов сумматора 2. Цикл приема и преобразовании двоично-десятичного кода в двоичный равен периоду поступления десятичных чисел в виде двоично-десятичных тетрад и состоит из первого полупериода поступления информации и второго полупериода ее отсутствия.

В первом полупериоде со схемы «И 37 на регистр 3 поступает сигнал, запрещающий запись информации, снимаемой с выходов регистра 1, так как код на входных шинах 34 при любом значении десятичного числа от «О до «9 отличен от кода 1111, а со схемы «НЕ 38 на регистр 1 поступает сигнал, разрешающий запись информации, снимаемой с выходов сумматора 2.

Двоично-десятичный код со входных шин 34 поступает на соответствующие четыре младших разряда сумматора 2, а двоичный код с выходов регистра 3 - на соответствующие входы сумматора 2. После сложения на сумматоре в соответствующие разряды регистра 1 записывается число, равное сумме преобразуемого числа и результата предыдущего цикла преобразования, умноженного на десять. Схемы «ИЛИ 32 и «ИЛИ 35 и 36 исключают случаи нарущения работы сумматора 2 в процессе работы устройства. Во втором полупериоде со схемы «И 37 на регистр 3 поступает сигнал, разрешающий запись информации, снимаемой с выходов регистра 1; результат преобразования, полученный в первом полупериоде, записывается в

регистр 3, а запись в регистр 1 запрещается сигналом, поступающим со схемы «НЕ 38. Одновременно с выходов регистра 1, являющихся выходами устройства, может производиться считывание промежуточного результата преобразования. Преобразование т-разрядного десятичного числа производится устройством за m циклов. После считывания окончательного результата преобразования устройство устанавливается в исходное состоянИе.

Цепи установки триггеров регистров в исходное состояние и цепи переносов сумматора на чертеже не показаны. Таким образом, устройство производит преобразование десятичного числа по мере периодического поступления его разрядов в виде тетрад, что позволяет совместить циклы приема и преобразования информации и, следовательно, повысить быстродействие устройства, а также упростить его.

Предмет изобретения

35 Преобразователь двоично-десятичного кода в двоичный, содержащий при преобразовании -разрядного десятичного числа первый реразрядами, входы которых соедигистр с

g2

нены с выходами соответствующих разрядов

т/ 2 о

гу-разрядного сумматора, выходы ly - 1

младших разрядов первого регистра соединены со входами соответствующих разрядов

т „ 2-разрядного второго регистра, выход

каждого 1-го разряда второго регистра, начиная со старщего разряда, непосредственно и

через первую и вторую схемы «ИЛИ соединены со входами i-ro и (t+2)-ro разрядов сумматора, инверсный выход первого и выход третьего младших разрядов второго регистра и входная Ш1ина старшего разряда

тетрады соединены со входами первой схемы «И выход, которой через первую схему «ИЛИ соединен со входом четвертого младшего разряда сумматора, входы второй схемы «И соединены с выходами первого и

третьего младших разрядов второго регистра и с входной шиной старшего разряда тетрады, а выход второй схемы «И соединен через третью схему «ИЛИ со входом четвертого младшего разряда первого регистра, отличающийся тем, что, с целью упрощения

устройства и повышения его быстродействия, оно содержит доиолиительную схему «И и схему «НЕ, входы дополнительной схемы «И соединены с входными шинами всех разрядов тетрады, соединенными со входами соответствующих младших разрядов су 1матора, выход дополнительной схемы «И соед,инен непосредственно и через схему «НЕ с управляющими входами второго и первого регистров соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU699520A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

fIjTJ tl

и r/6j 071 ш сю М

L.....3 k ь -,-,-j El-,. ., f.jy. JL-.- J

32 т г

i rjTin.rr nirr:rTzr :-т

rl j rl LI 1 tT Ij i

1-ttF f ff

Ш Ш Ш LzJ ta Ш ш ш Ш ш I

Авторы

Даты

1975-05-15—Публикация

1973-07-02—Подача